張琴1,楊瑩1,楊燦美2,林福江1

(1.中國科學(xué)技術(shù)大學(xué) 信息科學(xué)技術(shù)學(xué)院,安徽 合肥 230027;2.中國科學(xué)技術(shù)大學(xué) 先進(jìn)技術(shù)研究院,安徽 合肥 230027)

摘要:10GBASE-KR變速箱的功能是實(shí)現(xiàn)156.25 MHz下66 bit數(shù)據(jù)與644.53 MHz下16 bit數(shù)據(jù)之間的通信。該文在深入研究萬兆以太網(wǎng)物理編碼子層(Physical Coding Sublayer ,PCS)的功能以及變速箱原理的基礎(chǔ)上,提出一種新的變速箱實(shí)現(xiàn)方法,將其分成讀寫數(shù)據(jù)轉(zhuǎn)換和異步FIFO(First In First out)兩個(gè)模塊,完成發(fā)送通道和接收通道的設(shè)計(jì)。該方法有效減少了存儲(chǔ)器的數(shù)目,使存儲(chǔ)器數(shù)目由原來的528個(gè)減少到82個(gè)。本設(shè)計(jì)使用Verilog硬件描述語言,采用ModelSim進(jìn)行功能仿真,并利用EDA(Electronic Design Automation)工具完成邏輯綜合。仿真結(jié)果表明,該方法實(shí)現(xiàn)了變速箱的功能要求,并具有面積小、速度快的特點(diǎn)。

關(guān)鍵詞:變速箱;萬兆以太網(wǎng);PCS;邏輯綜合

0引言

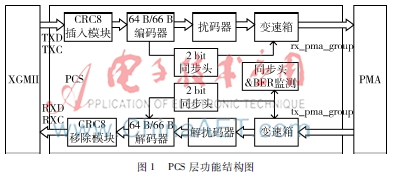

圖1PCS層功能結(jié)構(gòu)圖變速箱的功能是在保證數(shù)據(jù)率不變的前提下,完成高速信號(hào)與低速信號(hào)之間的通信,廣泛應(yīng)用于高速通信系統(tǒng)中。萬兆以太網(wǎng)作為以太網(wǎng)領(lǐng)域的先進(jìn)技術(shù),具有工作速率快、可靠性高、應(yīng)用范圍廣的特點(diǎn),有著廣泛的發(fā)展前景。本文根據(jù)10GBASEKR協(xié)議標(biāo)準(zhǔn),設(shè)計(jì)了一種新的物理編碼子層(PCS)變速箱實(shí)現(xiàn)方法,有效地簡化了電路的復(fù)雜度。

1PCS層的功能與結(jié)構(gòu)

PCS層位于媒體訪問控制子層(MAC)與物理介質(zhì)連接子層(PMA)之間,通過XGMII接口和PMA服務(wù)接口與上下層實(shí)現(xiàn)通信[1]。PCS層的結(jié)構(gòu)圖如圖1所示。由圖可知,PCS層由發(fā)送通道和接收通道構(gòu)成,發(fā)送通道將XGMII傳輸?shù)?2 bit(兩路32 bit的TXD和4 bit的TXC)數(shù)據(jù)轉(zhuǎn)換成16 bit的數(shù)據(jù)發(fā)送到PMA層,包括CRC8插入模塊、64 B/66 B編碼器、擾碼器和變速箱;接收通道接收PMA傳輸?shù)?6 bit的數(shù)據(jù)并轉(zhuǎn)換為72 bit(兩路32 bit的RXD和4 bit的RXC)數(shù)據(jù),包括CRC8移除模塊、64 B/66 B解碼器、解擾碼器和變速箱。整個(gè)PCS層以及XGMII接口的時(shí)鐘頻率為156.25 MHz,PMA層的時(shí)鐘頻率為644.53 MHz[2]。

2變速箱原理及傳統(tǒng)設(shè)計(jì)方法

由PCS層結(jié)構(gòu)圖可知,變速箱位于擾碼器/解擾碼器和PMA層之間,完成156.25 MHz的低速信號(hào)與644.53 MHz的高速信號(hào)間的通信。

發(fā)送通道中,變速箱的輸入為由擾碼器輸出的64 bit數(shù)據(jù)和64 B/66 B編碼器輸出的2 bit同步頭構(gòu)成的66 bit數(shù)據(jù),輸出是16 bit數(shù)據(jù),并發(fā)送到PMA層;接收通道中,變速箱輸入為PMA傳輸?shù)?6 bit數(shù)據(jù),輸出66 bit數(shù)據(jù),并將同步后的64 bit數(shù)據(jù)傳送到解擾碼器以及將2 bit同步頭傳送到64 B/66 B解碼器。

變速箱完成數(shù)據(jù)率為10.312 5 Gb/s信號(hào)間的傳輸,實(shí)現(xiàn)156.25 MHz下66 bit數(shù)據(jù)與644.53 MHz下16 bit數(shù)據(jù)的轉(zhuǎn)換。

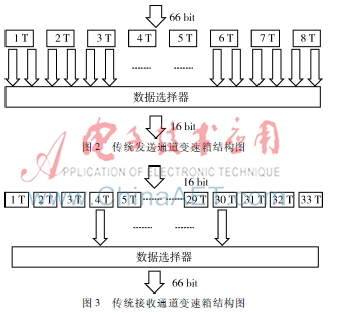

傳統(tǒng)的變速箱結(jié)構(gòu)圖如圖2和圖3所示[3]。圖2為發(fā)送通道變速箱結(jié)構(gòu)圖,其中,1 T~8 T是8個(gè)存儲(chǔ)單元,深度為66 bit,總共528 bit的存儲(chǔ)單元,每個(gè)存儲(chǔ)單元對(duì)應(yīng)每個(gè)時(shí)鐘周期的輸入數(shù)據(jù),然后通過數(shù)據(jù)選擇器在輸出時(shí)鐘有效沿到來時(shí)選擇一路數(shù)據(jù)輸出。該結(jié)構(gòu)實(shí)現(xiàn)的是8個(gè)66 bit數(shù)據(jù)轉(zhuǎn)換為33個(gè)16 bit數(shù)據(jù)。

圖4發(fā)送通道變速箱電路結(jié)構(gòu)圖圖3為接收通道變速箱結(jié)構(gòu),其中,1 T~33 T是33個(gè)存儲(chǔ)單元,深度為16 bit,同樣耗費(fèi)528 bit的存儲(chǔ)單元,每個(gè)存儲(chǔ)單元對(duì)應(yīng)每個(gè)時(shí)鐘周期的輸入數(shù)據(jù),然后通過數(shù)據(jù)選擇器在輸出時(shí)鐘有效沿到來時(shí)選擇一路數(shù)據(jù)輸出。從而實(shí)現(xiàn)16 bit數(shù)據(jù)到66 bit數(shù)據(jù)的轉(zhuǎn)換。

這種電路結(jié)構(gòu)耗費(fèi)的存儲(chǔ)器太多,導(dǎo)致整個(gè)電路的面積很大,并且造成很大的延遲。為了保證數(shù)據(jù)輸出時(shí)輸入數(shù)據(jù)已經(jīng)穩(wěn)定建立,數(shù)據(jù)選擇器的第一次輸出選擇的是第12個(gè)16 bit,還需人為加入17.05 ns的延遲[3]。另外,這種結(jié)構(gòu)的控制信號(hào)不易產(chǎn)生,電路的穩(wěn)定性大大降低。本文提出一種新的設(shè)計(jì)方法能夠有效地解決上述問題。

3新的變速箱設(shè)計(jì)

變速箱的設(shè)計(jì)難點(diǎn)是輸入數(shù)據(jù)寬度與輸出數(shù)據(jù)寬度不成整數(shù)倍,所以每次發(fā)送或者接收到的數(shù)據(jù)不能正好全部發(fā)完,剩下的數(shù)據(jù)必須等下一時(shí)刻數(shù)據(jù)到來時(shí)再發(fā)送。而且每次剩余的數(shù)據(jù)位置是不固定的。

本文將變速箱分為兩個(gè)部分:讀寫數(shù)據(jù)轉(zhuǎn)換模塊和異步FIFO模塊。讀寫數(shù)據(jù)轉(zhuǎn)換模塊完成數(shù)據(jù)轉(zhuǎn)換和處理剩余比特?cái)?shù)據(jù)問題,異步FIFO模塊完成跨時(shí)鐘域的數(shù)據(jù)傳輸。

發(fā)送通道中,本文選用16位的寄存器緩存每次讀取數(shù)據(jù)所余下的2 bit數(shù)據(jù)。每次寫操作對(duì)應(yīng)4次讀操作,在第8次寫操作時(shí),16位的寄存器中緩存了16 bit的數(shù)據(jù),所以,對(duì)應(yīng)5次讀操作,以實(shí)現(xiàn)8個(gè)66 bit的寫數(shù)據(jù)轉(zhuǎn)換為33個(gè)16 bit的讀數(shù)據(jù)。

本設(shè)計(jì)難點(diǎn)在于如何設(shè)計(jì)控制信號(hào)。因?yàn)槊看巫x寫操作結(jié)束后,余下的2 bit數(shù)據(jù)在16位寄存器中的位置是不固定的。本文設(shè)置了一個(gè)與讀時(shí)鐘同步的7位計(jì)數(shù)器,在每次讀操作結(jié)束,計(jì)數(shù)器累加16,同時(shí),設(shè)置了一個(gè)與讀時(shí)鐘同步的模33計(jì)數(shù)器,控制每33個(gè)讀時(shí)鐘周期只讀8次。電路結(jié)構(gòu)圖如圖4所示。在PCS時(shí)鐘有效沿將輸入的66 bit數(shù)據(jù)通過異步FIFO與PMA時(shí)鐘域同步,并通過模33計(jì)數(shù)器控制PMA的讀操作,輸出寄存在66位的寄存器中,將其高16 bit寄存到16位的緩存器中。

該方法有效減少了存儲(chǔ)器的數(shù)量,由傳統(tǒng)方法的528個(gè)存儲(chǔ)器減少到了82個(gè)存儲(chǔ)器(66+16=82),降低了異步FIFO的復(fù)雜度,并且減少了整個(gè)電路的面積。使用Verilog HDL[4]語言描述,部分關(guān)鍵代碼如下:

always @ (*)

case(counter)

7′d0:tx _group= shift_reg2[15: 0];

7′d2:tx _group={shift_reg1[1:0],shift_reg2[15:2]};

7′d4:tx _group={shift_reg1[3:0],shift_reg2[15: 4]};

7′d6:tx _group={shift_reg1[5:0],shift_reg2[15: 6]};

7′d8:tx _group={shift_reg1[7: 0],shift_reg2[15: 8]};

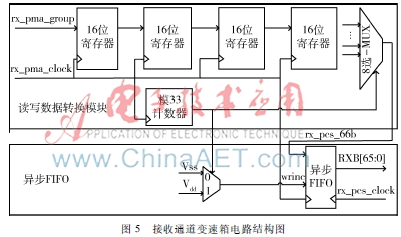

接收通道中,設(shè)置4個(gè)16位寄存器級(jí)聯(lián),將每個(gè)寄存器的輸出與輸入拼接構(gòu)成66 bit數(shù)據(jù)。設(shè)計(jì)難點(diǎn)同樣在于如何設(shè)計(jì)控制信號(hào)。4個(gè)16 bit數(shù)據(jù)只能組成64 bit數(shù)據(jù),需要拼接2 bit數(shù)據(jù),而這2 bit數(shù)據(jù)的位置是不確定的,另外寫時(shí)鐘頻率比讀時(shí)鐘頻率快很多,直接利用異步FIFO將導(dǎo)致FIFO總是寫滿狀態(tài)。

本文設(shè)置了一個(gè)與寫時(shí)鐘同步的模33計(jì)數(shù)器,控制選擇正確的66 bit的拼接數(shù)據(jù),同時(shí)控制每33個(gè)寫時(shí)鐘周期只寫8次數(shù)據(jù),輸入到異步FIFO中,避免了由于寫時(shí)鐘頻率比讀時(shí)鐘頻率快很多而導(dǎo)致FIFO總是寫滿的情況。電路結(jié)構(gòu)如圖5所示。在PMA時(shí)鐘有效沿,計(jì)數(shù)器開始計(jì)數(shù),生成的控制信號(hào)作為8選1 MUX的選擇信號(hào),選擇正確的信號(hào)作為異步FIFO的寫信號(hào)。同時(shí),模33計(jì)數(shù)器開始計(jì)數(shù),控制寫使能信號(hào)的產(chǎn)生,控制異步FIFO的寫操作,輸出正確的66 bit信號(hào)。本文中的異步FIFO均采用傳統(tǒng)的異步FIFO設(shè)計(jì)結(jié)構(gòu)[5],利用2級(jí)D觸發(fā)器級(jí)聯(lián),并采用格雷碼完成寫地址與讀時(shí)鐘以及讀地址與寫時(shí)鐘的同步,避免電路出現(xiàn)亞穩(wěn)態(tài)。與傳統(tǒng)設(shè)計(jì)方法相比,本設(shè)計(jì)有效地降低了電路的復(fù)雜度和整個(gè)電路的面積。部分關(guān)鍵代碼為:

圖5接收通道變速箱電路結(jié)構(gòu)圖always @ (*)

case(rx_fetch_cnt[4:2])

3'd0: rx_pcs_66b={rx_pma_group[1:0],rx_pma_group1,

rx_pma_group2,rx_pma_group3,rx_pma_group4};

3'd1: rx_pcs_66b={rx_pma_group[3 :0],rx_pma_group1,

rx_pma_group2,rx_pma_group3,rx_pma_group4[15: 2]};

3'd2: rx_pcs_66b={rx_pma_group[5 :0],rx_pma_group1,

rx_pma_group2,rx_pma_group3,rx_pma_group4[15: 4]};

3'd3: rx_pcs_66b={rx_pma_group[7 :0],rx_pma_group1,

rx_pma_group2,rx_pma_group3,rx_pma_group4[15: 6]};

3'd4: rx_pcs_66b={rx_pma_group[9 :0],rx_pma_group1,

rx_pma_group2,rx_pma_group3,rx_pma_group4[15: 8]};

3'd5: rx_pcs_66b={rx_pma_group[11:0],rx_pma_group1,

rx_pma_group2,rx_pma_group3,rx_pma_group4[15:10]};

4功能仿真與邏輯綜合

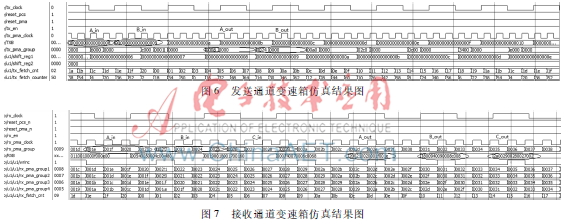

本設(shè)計(jì)通過編寫測試向量采用ModelSim工具完成各個(gè)模塊的功能仿真,仿真結(jié)果如圖6和圖7所示。圖6中,當(dāng)輸入信號(hào)為A_in時(shí),對(duì)應(yīng)的輸出為A_out;當(dāng)輸入信號(hào)為B_in時(shí),對(duì)應(yīng)的輸出為B_out。圖7中,當(dāng)輸入信號(hào)為A_in時(shí),對(duì)應(yīng)的輸出為A_out;當(dāng)輸入信號(hào)為B_in時(shí),對(duì)應(yīng)的輸出為B_out;當(dāng)輸入信號(hào)為C_in時(shí),對(duì)應(yīng)的輸出為C_out。為了保證信號(hào)的穩(wěn)定性,人為地加入了一定的延遲。從仿真結(jié)果可以看出,輸入所對(duì)應(yīng)的輸出都是正確的,表明本設(shè)計(jì)實(shí)現(xiàn)了PCS層發(fā)送通道和接收通道的變速箱功能仿真。

另外,本設(shè)計(jì)采用Synopsys公司的Design Compiler[6]工具完成了邏輯綜合。綜合結(jié)果表明設(shè)計(jì)完全符合PCS變速箱的時(shí)序要求。發(fā)送和接收電路分別留有4.56 ns、3.92 ns的時(shí)鐘裕量,且面積小,分別使用了近1 000個(gè)邏輯門;在工作頻率方面,發(fā)送電路使用了286個(gè)D觸發(fā)器,最高寫時(shí)鐘頻率分別為232.56 MHz、927.35 MHz,最高讀時(shí)鐘頻率分別為961.54 MHz、211.42 MHz,使用了近1 300個(gè)邏輯門。與傳統(tǒng)的設(shè)計(jì)方法[3]相比,面積縮小了近30%,工作速度提高了近50%。

5結(jié)論

本文在研究變速箱原理的基礎(chǔ)上,根據(jù)其內(nèi)在的邏輯關(guān)系,將電路分成寫數(shù)據(jù)轉(zhuǎn)換模塊和異步FIFO兩部分,設(shè)計(jì)了PCS層發(fā)送通道和接收通道的變速箱。完成了功能仿真和邏輯綜合。綜合結(jié)果表明,該方法有效地解決了控制信號(hào)不易設(shè)計(jì)和亞穩(wěn)態(tài)的問題,縮小了面積,提高了工作速率。

參考文獻(xiàn)

[1] Vivado design suite user guide: 10 GB Ethernet PCS/PMA v4.0[Z]. PG068 October 2, 2013.

[2] IEEE Std 802.3ap[S]. 2012 Edition.

[3] 敖志剛.萬兆位以太網(wǎng)及其實(shí)用技術(shù)[M].北京:電子工業(yè)出版社,2007.

[4] 夏宇聞.Verilog數(shù)字系統(tǒng)設(shè)計(jì)(第二版)[M].北京:北京航空航天大學(xué)出版社,2008.

[5] VERILOG E, CUMMINGS C E. Simulation and synthesis techniques for asynchronous FIFO design[M]. Snug, 2002.