文獻標識碼: A

DOI:10.16157/j.issn.0258-7998.2016.09.003

中文引用格式: 張德智,曾星星, 胡倩. 基于并行處理技術(shù)的寬帶直擴信號捕獲方法[J].電子技術(shù)應(yīng)用,2016,42(9):10-13.

英文引用格式: Zhang Dezhi,Zeng Xingxing,Hu Qian. Wideband DS-Signal capture scheme based on parallel processing technology[J].Application of Electronic Technique,2016,42(9):10-13.

0 引言

擴頻信號以其隱蔽性好、抗干擾性強的特點,在各類通信、導(dǎo)航、數(shù)據(jù)鏈傳輸體制中得到廣泛應(yīng)用[1]。常用擴頻信號(如GPS)偽碼速率不超過10.23 Mcps,偽碼長度不超過1 023,擴頻增益較低、信號帶寬較窄,抗干擾和保密能力有限。隨著飛行器通信頻段由傳統(tǒng)的L、S頻段向更高的Ku、Ka頻段邁進,用戶信道資源日趨豐富,帶寬達數(shù)百兆赫茲的寬帶擴頻體制逐步得到應(yīng)用,寬帶擴頻信號頻譜更隱蔽保密性更高,抗干擾能力更強,具有良好的應(yīng)用前景。

同窄帶擴頻信號相比,寬帶擴頻信號帶寬更寬,AD采樣速率要求高達數(shù)百兆赫茲,超出大多數(shù)后端器件直接處理能力[2]。目前主流的擴頻快捕算法均針對10 Mbps以下的窄帶擴頻信號,而對于寬帶擴頻信號尚未發(fā)現(xiàn)有效的捕獲方法。為解決此問題,本文設(shè)計一種基于并行信號處理技術(shù)的快捕算法,在不降低前端采樣率的情況下,使得后端處理器件在可承受的時鐘頻率下實現(xiàn)寬帶擴頻信號的快速捕獲。

1 捕獲算法頂層設(shè)計

1.1 指標需求

某項目寬帶擴頻信號為零中頻形式,速率為153.45 Mcps,信息速率10 kbps,偽碼周期15 345(內(nèi)外碼相乘的復(fù)合碼形式,內(nèi)碼長15,碼率153.45 M,外碼長1 023碼率10.23 M,相位相干對齊),信號體制為PCM-DS(直接序列擴頻)-BPSK(載波相位調(diào)制),多普勒動態(tài)范圍±90 kHz,最大變化率±2.4 kHz/s,載頻為S頻段。

1.2 硬件架構(gòu)設(shè)計

考慮射頻濾波器矩形系數(shù),信號采樣率至少應(yīng)大于1.2 GHz,為降低對AD器件及后端處理器件壓力,應(yīng)選用正交采樣形式,這樣雙通道AD采樣速率600 MHz即可滿足低通采樣要求。后端信號處理FPGA(現(xiàn)場可編程邏輯門陣列)采用XC5VFX100T,根據(jù)器件特性無法直接工作于600 MHz處理采樣數(shù)據(jù),因此需采用并行信號處理技術(shù),實現(xiàn)以面積換速度。

1.3 軟件功能設(shè)計

解調(diào)算法整體結(jié)構(gòu)如圖1所示,功能上可劃分為串并轉(zhuǎn)換、并行下變頻、并行偽碼NCO、并行載波NCO、并行偽碼生成器、捕獲處理模塊、跟蹤處理模塊等。

串并轉(zhuǎn)換模塊將AD輸入的高速串行數(shù)據(jù)拼接、轉(zhuǎn)換成8路并行的I、Q數(shù)據(jù),供后續(xù)并行處理。AD器件自帶1分2 DEMUX,將I、Q通道的數(shù)據(jù)速率降低至300 MHz(如圖1所示,I0、I1、Q0、Q1速率為300 MHz),這樣后端FPGA串并轉(zhuǎn)換處理時鐘僅需300 MHz。對I0、I1(同理Q0、Q1)分別再進行1分4的串并轉(zhuǎn)換,并按照采樣時間的先后順序重新排列拼接,最終將600 MHz的10 bit采樣數(shù)據(jù),1分8串并轉(zhuǎn)換成80 bit的拼接數(shù)據(jù)。這樣后續(xù)信號處理工作時鐘降為75 MHz,易于FPGA實現(xiàn)。

輸入信號含有載波多普勒,I、Q數(shù)據(jù)經(jīng)串并轉(zhuǎn)換模塊后變成8路并行數(shù)據(jù),需要經(jīng)并行下變頻模塊進行去多普勒處理。并行下變頻模塊由并行載波NCO驅(qū)動,中心頻率受捕獲模塊和跟蹤模塊控制字控制。

針對并行處理后的I、Q數(shù)據(jù),本地偽碼生成器同樣采用并行模式,由并行碼NCO驅(qū)動。NCO的頻率控制字由捕獲模塊和跟蹤模塊控制,實現(xiàn)本地偽碼滑動。輸入數(shù)據(jù)和本地偽碼解擴后進捕獲模塊,完成載波和偽碼捕獲,調(diào)整偽碼和載波NCO到近似對齊的相位和頻率上。捕獲完成后轉(zhuǎn)入跟蹤環(huán)節(jié)。

1.4 捕獲參數(shù)設(shè)計

速率為153.45 Mcps,信息速率10 kbps,偽碼周期15 345,因此積分清零時間選定為0.1 ms。根據(jù)碼多普勒和載波多普勒比例關(guān)系,fdchip為偽碼多普勒,Rc為偽碼速率,fc為載波頻率,fdop為載波多普勒。

當載波多普勒達到±90 kHz時,偽碼多普勒可達fdchip=6.818 kHz,積分清零時間為0.1 ms,則積分清零周期內(nèi)偽碼會漂移0.68個碼片,因此一次滑動半個碼片是不可行的,需要在頻域上分段搜索以降低碼多普勒影響。

因此本設(shè)計采用頻率分段+內(nèi)碼滑動相關(guān)+外碼匹配濾波的捕獲方式,滑動相關(guān)找到內(nèi)碼相位,對內(nèi)碼進行積分累加后,再對外碼進行匹配濾波,濾波器長度只需要1 023,資源占用較少。

2 核心模塊設(shè)計

2.1 正交下變頻設(shè)計

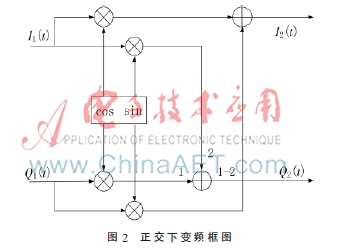

本方案中AD采樣信號是下變頻后的零中頻基帶信號,AD輸入含有I、Q兩個支路,因此本地產(chǎn)生的數(shù)字下變頻需要采取特殊設(shè)計。將輸入I、Q信號定義如下:

用復(fù)信號表示為:

由此可得正交下變頻器的結(jié)構(gòu)如圖2所示。

2.2 基于并行載波NCO的下變頻實現(xiàn)

本地NCO的采樣率應(yīng)與輸入信號采樣率一致為600 MHz,如此高采樣速率的NCO無法直接在器件中實現(xiàn),需要采樣并行設(shè)計。根據(jù)DDS原理,本地載波信號頻率可表示為式(9),fs為信號采樣率,這里為600 MHz,fc為希望得到的頻率,N為量化位數(shù),K為頻率控制字,可根據(jù)fs、fc、N求出。

fc=fs·K/2N(9)

如果系統(tǒng)時鐘為600 MHz,則1個NCO可在8個時鐘周期內(nèi)得到8個載波相位,記為Ph1,…,Ph8,通過查表可得到相應(yīng)載波幅度值,這樣在1/75 MHz(8個600 MHz時鐘周期)時間內(nèi)得到8個連續(xù)的載波采樣點。

當系統(tǒng)時鐘為75 MHz時,若采用8個載波NCO同時工作,則在1/75 MHz時間內(nèi)同樣可得到8個相位值P1,…,P8,分別查表得到8個載波幅值,這樣在1/75 MHz時間內(nèi)同樣得到8個載波采樣點。通過調(diào)整各NCO的步進值,可使得P1,…,P8與Ph1,…,Ph8等效,從而實現(xiàn)與600 MHz的載波NCO等效。

NCO具體設(shè)計方式如下,設(shè)任一時刻8個NCO的相位累加器值為Pi,i=1,…,8,則Pi表達式如式(10)所示,其中P0為上一個時鐘周期第8個累加器的相位值,K與式(9)一致,這樣P1,…,P8與Ph1,…,Ph8等效。

Pi=P0+K·i,i=1,…,8(10)

在一個時鐘周期內(nèi)8個累加器可以得到P1,…,P8共8個相位值,通過查找8塊同樣的查找表,可以得到等效在600 MHz采樣率下連續(xù)的8個載波值cos(n+1),…,cos(n+8),sin(n+1),…,sin(n+8)。

這樣數(shù)字化后的并行下變頻的結(jié)果I3(n+k)、Q3(n+k),k=1,…,8表達式如式(11)、式(12)所示:

I3(n+k)=I2(n+k)·cos(n+k)+Q2(n+k)·sin(n+k)(11)

Q3(n+k)=Q2(n+k)·sin(n+k)-I2(n+k)·cos(n+k)(12)

其中I2(n+k)=Q2(n+k)為串并轉(zhuǎn)換后的采樣數(shù)據(jù),為降低后續(xù)處理資源消耗,將下變頻后的輸出截位至12 bit,則8路并行后的輸出為96 bit。

2.3 并行本地偽碼產(chǎn)生

擴頻信號的捕獲需要本地產(chǎn)生與發(fā)端一致的偽碼序列,由本地碼NCO推動碼生成器產(chǎn)生,對于本設(shè)計偽碼速率高達153.45 Mcps,采樣率為600 MHz,同樣只能采用并行的偽碼生成方式。根據(jù)式(9),fs為信號采樣率,這里為600 MHz,fc為碼率153.45 Mcps,N為量化位數(shù)取N=36,則可求出頻率控制字K。

與2.2節(jié)類似,偽碼時鐘由8個獨立的碼NCO模塊產(chǎn)生。定義75 MHz主時鐘下的并行碼鐘為pn_clk[clk1,clk2,…,clk8],clki,i=1,...,8代表在600 MHz采樣頻率下的連續(xù)8個偽碼時鐘,1個主時鐘內(nèi)共有8個采樣點。clki可由式(13)得出,Pc0為上一個時鐘周期第8個相位累加器的相位值,Pci(i=1,...,8)為8路碼NCO模塊的36位累加器相位值。

{clki,Pci}=Pc0+K·i(13)

本設(shè)并行計偽碼的產(chǎn)生由ROM查表實現(xiàn),將復(fù)合碼的內(nèi)碼、外碼的一個周期序列存儲到ROM中,通過不同的查找地址得出相應(yīng)偽碼。由于偽碼速率和主時鐘非整數(shù)倍關(guān)系(2.046),可知在1個75 MHz時鐘周期內(nèi)(等效8個600 MHz時鐘)最多同時存在3個內(nèi)碼碼片(2個完整碼片,1個不完整碼片)。因此選用了3個深度為15,寬度為1 bit的ROM用于存儲內(nèi)碼,ROM_B中的內(nèi)碼相位比ROM_A滯后1個碼片,ROM_C中的內(nèi)碼相位比ROM_B滯后1個碼片。

外碼的產(chǎn)生于內(nèi)碼類似,在1個75 MHz主時鐘內(nèi)最多存在2個內(nèi)碼,因此需要兩個深度為1 023寬度為1 bit的ROM用于存儲外碼。

并行偽碼產(chǎn)生的仿真結(jié)果如圖3所示, clk為75 MHz主時鐘,pn_clk為8路并行碼時鐘,0、1交替的位置表示一個碼片的起止位置。以pn_clk=[01111000]為例,在此主時鐘周期內(nèi)存在8個600 MHz時鐘采樣點,前一碼片的最后一個采樣點在bit7結(jié)束,bit6-bit3為當前碼片的起止位置,bit2-bit0為下一個碼片的前3個采樣點位置。偽碼輸出記為pn_out[pn1,pn2,,...pn8],其中pni,i=1...8代表在該75 MHz時鐘內(nèi),由600 MHz時鐘對偽碼進行采樣,得到的8個采樣數(shù)據(jù)。

2.4 捕獲方案設(shè)計

根據(jù)前述分析,本方案采用頻率分段+匹配濾波器的捕獲方式,該方式操作簡單,具有最快的捕獲速度,但資源消耗較大,但對于XC5VFX100T系列平臺影響較小。

擴頻信號的快捕包括載波和偽碼兩個層面,載波捕獲采用分段搜索的策略,在每個頻段內(nèi)搜索偽碼相位,并對偽碼進行輔助,降低載波多普勒的影響。考慮到跟蹤模塊鎖頻環(huán)的有效牽引范圍為±1/4T,T為積分清零時間0.1 ms,因此對于本設(shè)計多普勒分段間隔不應(yīng)超過5 kHz。本設(shè)計多普勒搜索范圍要求±90 kHz,變化率2.4 kHz/s,分段間隔過窄會導(dǎo)致捕獲時間變長,綜合考慮后這里取分段間隔為2.4 kHz,共劃分為81個分段,多普勒搜索范圍可達±96 kHz,捕獲完成后多普勒補償精度可達±1.2 kHz。

由于輸入偽碼的復(fù)合碼特性,可以將偽碼捕獲分為外碼捕獲、內(nèi)碼捕獲兩個過程,內(nèi)碼周期很短只有15,故可以采用滑動相關(guān)的方式,一次步進半個碼片,滑動一個完整內(nèi)碼周期后進行積分清0,積分周期為一個外碼碼片的周期即0.1/1 023 ms。

這樣積分清0后的偽碼速率從153.45 Mcps降到10.23 Mcps,再進入1 023長的匹配濾波器,連續(xù)1 023個積分值進入后(即一個完整外碼周期)可得到相關(guān)峰值。當內(nèi)碼滑動到對齊位置時,外碼匹配濾波器的輸出一定會出現(xiàn)最大相關(guān)峰。采用這種方式只需要設(shè)計1 023長的匹配濾波器,可以節(jié)省設(shè)計資源。為了提高捕獲靈敏度,可以對匹配濾波結(jié)果作非相干累加,非相干累加10次后,信噪比可提高約7 dB。匹配濾波器的工作頻率只需10.23 MHz,不再需要并行信號處理[4]。

由于碼多普勒存在,當分段間隔為2.4 kHz時,經(jīng)載波輔助后,當前頻帶內(nèi)的最大碼多普勒為:

fdchip=1.2k153.45/2 325=79.2 Hz(14)

復(fù)合碼周期為0.1 ms,累加10次后用時1 ms,在此期間內(nèi)碼片偏移0.079 2個碼片,若內(nèi)碼按照1/2碼片滑動,則滑動一次后實際變化0.5-0.079 8=0.42個碼片,則為了保證能遍歷所有內(nèi)碼相位,內(nèi)碼滑動次數(shù)應(yīng)至少為15/0.42=36次。

捕獲流程為:捕獲環(huán)節(jié)開始后,首先從多普勒分段1開始滑動內(nèi)碼相位,外碼同時作匹配濾波,內(nèi)碼遍歷結(jié)束后可得到36個相關(guān)峰值;多普勒分段切換至分段2,重復(fù)上述過程,當所有81頻率分段均遍歷完成后,可得2 916個相關(guān)峰,記最大相關(guān)峰為peak1,記錄對應(yīng)的外碼序號和內(nèi)碼序號;由于遍歷過程用時較長,在此期間多普勒會發(fā)生動態(tài)變化,因此還需在peak1所在頻率分段的相鄰3個段內(nèi)重新搜索碼相位,此過程的最大相關(guān)峰為peak2,當相關(guān)峰peak2與peak1可比擬,且對應(yīng)外碼、內(nèi)碼序號與peak1位置接近時,認為捕獲完成。將peak2所在多普勒分段信息補償載波NCO,實現(xiàn)頻率捕獲,根據(jù)內(nèi)碼和外碼序號置偽碼生成器,實現(xiàn)偽碼粗對準,隨后轉(zhuǎn)入跟蹤環(huán)節(jié)。

3 仿真結(jié)果及性能分析

3.1 仿真結(jié)果

由Simulink產(chǎn)生采樣率為600 MHz,C/No=90 dB/Hz(等效信號電平-80 dBm),多普勒為50 kHz的復(fù)合碼擴頻信號作為仿真輸入。當搜索到正確頻道時內(nèi)碼滑動過程對應(yīng)的外碼匹配濾波仿真結(jié)果如圖4所示。rms_out為外碼匹配濾波結(jié)果,此時有非常明顯的相關(guān)峰出現(xiàn)。當內(nèi)碼滑動相差超過一個碼片時,外碼匹配濾波的相關(guān)峰急劇降低,仿真結(jié)果如圖5所示。

3.2 捕獲時間計算

根據(jù)前述分析,遍歷一個頻率分段需要滑動36次,內(nèi)碼滑動期間外碼非相干累加10次,所需時間為36×10×0.1=36 ms。第一次遍歷搜索81個分段,用時81×36 ms=2.916 s,此期間最大多普勒變化達2.916 s*2.4 kHz/s=7.2 kHz跨越三個頻率分段,需要對當前分段和前后相鄰各3個分段進行再次搜索。

第二次遍歷搜索7個頻道,用時7×36 ms=0.252 s。

總捕獲時間為2.916+0.252=3.168 s。

3.3 資源占用分析

本算法串并轉(zhuǎn)換模塊、下變頻模塊、偽碼NCO模塊、偽碼產(chǎn)生模塊、捕獲模塊的內(nèi)碼滑動、積分累加為并行處理環(huán)節(jié),占用資源較多;捕獲模塊外碼匹配濾波、捕獲策略設(shè)計、跟蹤環(huán)節(jié)是非并行設(shè)計模塊。占用資源較少。經(jīng)ISE綜合,共占用FPGA片內(nèi)63%的Slice資源、46%的塊RAM資源、52%的乘法器資源。

4 結(jié)論

經(jīng)過分析計算可知,本文提出的寬帶擴頻信號捕獲算法,通過“以面積換速度”的形式,利用并行信號處理技術(shù),有效降低了系統(tǒng)處理時鐘要求,算法技術(shù)可行實現(xiàn)簡單,共占用FPGA片內(nèi)63%的Slice資源、46%的塊RAM資源、52%的乘法器資源,資源占用率較低,利于工程實現(xiàn)。

參考文獻

[1] 黃愛軍.衛(wèi)星通信抗干擾設(shè)計考慮及性能分析[J].電訊技術(shù),2012,52(3):259-263.

[2] 童長海,鄭雪峰,鄭戈,等.600 Mb/s高速數(shù)傳接收機的設(shè)計與實現(xiàn)[J].遙測遙控,2007,28(S1):34-38.

[3] 嚴家明,李瑾,胡楚鋒.基于正交混頻的數(shù)字下變頻技術(shù)研究[J].計算機測量與控制.2009,17(1):200-202.

[4] 代敏,禹思敏,羅玉玲.匹配濾波器同步捕獲技術(shù)FPGA設(shè)計[J].通信技術(shù).2010,43(2):13-16.