文獻(xiàn)標(biāo)識碼: A

DOI:10.16157/j.issn.0258-7998.2016.09.010

中文引用格式: 龍奎成,卿粼波,,何小海,,等. 基于FPGA的DSC高速譯碼器設(shè)計(jì)及實(shí)現(xiàn)[J].電子技術(shù)應(yīng)用,2016,,42(9):39-43.

英文引用格式: Long Kuicheng,,Qing Linbo,He Xiaohai,,et al. The design and implementation of DSC high speed decoder based on FPGA[J].Application of Electronic Technique,,2016,42(9):39-43.

0 引言

分布式信源編(DSC)解碼較傳統(tǒng)信道編解碼而言,因其編碼簡單,、譯碼復(fù)雜成為近年來通信領(lǐng)域的研究熱點(diǎn)。DSC編碼端各信源獨(dú)立編碼,,譯碼端根據(jù)信源的相關(guān)性聯(lián)合譯碼,,從而降低了編碼的復(fù)雜度,而把整個系統(tǒng)的復(fù)雜度轉(zhuǎn)移到譯碼端,,所以本文重點(diǎn)研究DSC譯碼器的設(shè)計(jì),。

Turbo碼和LDPC碼是實(shí)現(xiàn)DSC譯碼器的兩種主要編碼。在DSC譯碼過程中,,Turbo碼譯碼算法復(fù)雜,、譯碼延時(shí)長且存在一定的不可檢測錯誤,而LDPC碼具有較大的靈活性,、較低的差錯平底特性,、譯碼速度快、具有高效的譯碼迭代算法[1],,因此LDPC碼更適合于實(shí)現(xiàn)DSC譯碼器,。

LDPC碼分為規(guī)則LDPC碼和非規(guī)則LDPC碼,非規(guī)則LDPC碼的譯碼性能優(yōu)于規(guī)則LDPC碼,,是目前己知的最接近Shannon限的碼[2],,所以本文采用非規(guī)則LDPC碼實(shí)現(xiàn)DSC譯碼器。

本文設(shè)計(jì)的DSC譯碼器具有反饋信道,,根據(jù)當(dāng)前聯(lián)合譯碼的結(jié)果把譯碼判決信息反饋到編碼端,,但這種方法對實(shí)時(shí)性要求很高[3],這是限制DSC譯碼器工程應(yīng)用的一個重要因素,。FPGA由于其強(qiáng)大的數(shù)據(jù)并行處理能力,,能夠做到數(shù)據(jù)處理的實(shí)時(shí)性、高效性,。所以,,F(xiàn)PGA能夠解決DSC譯碼器反饋信道實(shí)時(shí)性的問題。

Log-BP算法,、BP-Based算法,、歸一化最小和(NMS)算法是3種常用的DSC譯碼算法,這3種算法把一部分乘法用求和運(yùn)算代替極大地減少了運(yùn)算量,。Log-BP算法修正了碼長較長時(shí)概率 BP 譯碼算法計(jì)算不穩(wěn)定的問題,,但是仍然存在乘法運(yùn)算不利于 FPGA實(shí)現(xiàn)。BP-Based算法雖然降低了運(yùn)算量,,但BP-Based 算法相對于Log-BP算法收斂速度慢,,譯碼性能也不如前者[4],。NMS算法和BP-Based算法的復(fù)雜度幾乎相同,若選取合適的歸一化因子η,,能將乘法用加法和移位操作代替,,并且其譯碼性能與概率BP算法幾乎一致[5]。因此,,NMS算法在FPGA實(shí)現(xiàn)時(shí)被大量采用,。

基于非規(guī)則LDPC碼、FPGA,、NMS譯碼算法3方面的優(yōu)點(diǎn),,本文的主要工作是采用非規(guī)則LDPC碼、運(yùn)用NMS譯碼算法設(shè)計(jì)了一種全新的,、實(shí)時(shí)高速的DSC譯碼器并在Xilinx XC7VX485T上實(shí)現(xiàn)了該譯碼器,。該譯碼器的吞吐率可達(dá)197 Mb/s,具有較好的工程應(yīng)用價(jià)值,。

1 DSC譯碼器實(shí)現(xiàn)的理論基礎(chǔ)

1.1 DSC的基本原理

假設(shè)Xi(i=1,,2…N)是來自同一個系統(tǒng)的N個信源,這N個信源之間的相關(guān)性稱為邊信息,,現(xiàn)對這N個信源進(jìn)行獨(dú)立編碼,,將編碼后的N路信息傳輸?shù)酵粋€譯碼節(jié)點(diǎn),并結(jié)合邊信息進(jìn)行聯(lián)合譯碼,。因此,,DSC系統(tǒng)的編碼端極為簡單,其復(fù)雜度主要體現(xiàn)在譯碼端,。

1.2 基于非規(guī)則LDPC碼的DSC系統(tǒng)

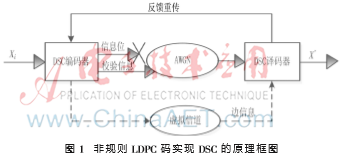

圖1是非規(guī)則LDPC碼實(shí)現(xiàn)DSC系統(tǒng)的框圖,,其中Xi(i=1,2…N)表示來自同一個系統(tǒng)的N個信源,,DSC編碼器和譯碼器根據(jù)非規(guī)則LDPC碼的校驗(yàn)矩陣(H矩陣)而設(shè)計(jì),。

從圖1中可知,非規(guī)則LDPC碼實(shí)現(xiàn)DSC編解碼系統(tǒng)的基本原理:信源Xi經(jīng)過DSC編碼器后輸出信息位和校驗(yàn)信息,,與傳統(tǒng)譯碼相比,,DSC編解碼系統(tǒng)丟棄信息位并且經(jīng)高斯白噪聲(AWGN)信道每次只傳輸少量的校驗(yàn)位到DSC譯碼器,如此可以實(shí)現(xiàn)碼率自適應(yīng)并提高壓縮效率,。同時(shí)邊信息經(jīng)過虛擬信道傳輸?shù)紻SC譯碼器進(jìn)行聯(lián)合譯碼,,如果此時(shí)能夠正確譯碼就輸出譯碼信息X’,否則進(jìn)行反饋重傳校驗(yàn)位繼續(xù)譯碼,,直至正確譯碼輸出,。

1.3 LDPC譯碼算法

NMS譯碼算法具體闡述如下:

設(shè)α2為AWGN信道的方差,yi表示接收到的信息,L(ci)為信道初始化信息,,L(qij)為變量節(jié)點(diǎn)接收來自校驗(yàn)節(jié)點(diǎn)的信息,,L(rji)為校驗(yàn)節(jié)點(diǎn)接收來自變量節(jié)點(diǎn)的信息,L(Qi)是變量節(jié)點(diǎn)接收到的全部信息,,C(i)表示連接變量節(jié)點(diǎn)i的所有校驗(yàn)節(jié)點(diǎn),,C(i)\j表示連接變量節(jié)點(diǎn)i中除j外的全部校驗(yàn)節(jié)點(diǎn),C(j)\i表示連接校驗(yàn)節(jié)點(diǎn)j中除i外的全部變量節(jié)點(diǎn),,η表示歸一化因子,。

(1)初始化:

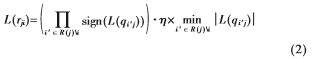

(2)更新校驗(yàn)節(jié)點(diǎn):

(3)更新變量節(jié)點(diǎn):

(4)更新L(Qi):

(5)最后,對任意i,,有:

若變量節(jié)點(diǎn)收集到的信息值L(Qi)<0,,對任意i,,判別譯出的碼字 ,。如果H^T c^^=0或者譯碼的迭代次數(shù)等于預(yù)設(shè)的最大值,c^^也作為最終譯碼輸出,,并強(qiáng)制終止譯碼計(jì)算,;否則轉(zhuǎn)至步驟(2)繼續(xù)譯碼計(jì)算。

,。如果H^T c^^=0或者譯碼的迭代次數(shù)等于預(yù)設(shè)的最大值,c^^也作為最終譯碼輸出,,并強(qiáng)制終止譯碼計(jì)算,;否則轉(zhuǎn)至步驟(2)繼續(xù)譯碼計(jì)算。

從式(2)中可以看出NMS算法仍然存在少量的乘法運(yùn)算,,若選取合理的η,,則能在不損失譯碼性能的情況下,將乘法用加法和移位操作代替[5],,使譯碼的計(jì)算量最少,、譯碼的復(fù)雜度最小、FPGA消耗的資源最少,。

η是一個小于1的正常數(shù),,通常在FPGA上實(shí)現(xiàn)LDPC譯碼算法時(shí)選取η為0.75,此時(shí)的NMS算法譯碼性能最佳[6],。

2 DSC譯碼器設(shè)計(jì)

文獻(xiàn)[7]對非規(guī)則(2 048,,1 024)、碼率1/2的H矩陣的研究表明該H矩陣在譯碼過程中能夠?qū)崿F(xiàn)相當(dāng)?shù)偷恼`碼率,。因此本文選用此類型度分布為(λ(x),,ρ(x)),碼率為1/2的非規(guī)則H矩陣,,其中λ(x)=0.285 6x+0.257 5x2+0.456 7 x7,,ρ(x)=0.003 4x5+0.996 6x6。

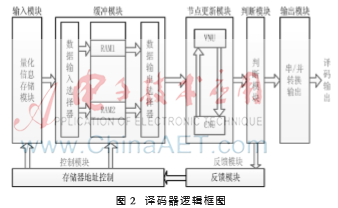

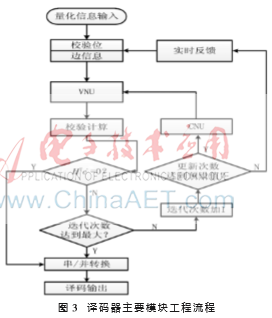

本文設(shè)計(jì)的DSC譯碼器分為輸入模塊,、緩沖模塊,、節(jié)點(diǎn)信息更新模塊、判決模塊、控制模塊,、反饋模塊,、輸出模塊。圖2是DSC譯碼器的邏輯結(jié)構(gòu)圖,,該譯碼器主要模塊的功能如下:

(1)將量化好的邊信息,、校驗(yàn)位信息存入FPGA Block RAM模塊中。

(2)緩沖模塊中兩個完全相同的RAM塊用于乒乓操作,,周期性地切換數(shù)據(jù)選擇器可以提高數(shù)據(jù)傳輸?shù)乃俾?、效率,亦能使緩沖模塊與節(jié)點(diǎn)更新模塊的速率相匹配,。

(3)控制模塊用于控制量化信息存儲器和緩沖模塊的工作時(shí)序,,保證這兩個模塊有序工作,保證數(shù)據(jù)連續(xù),。

(4)節(jié)點(diǎn)信息更新模塊控制變量和校驗(yàn)兩類節(jié)點(diǎn)的信息更新,,并將判決信息輸出給判決模塊。

(5)反饋模塊把判決結(jié)果實(shí)時(shí)反饋到數(shù)據(jù)輸出選擇器端,,通知輸出選擇器繼續(xù)發(fā)送校驗(yàn)信息,。

該譯碼器的設(shè)計(jì)重點(diǎn)體現(xiàn)在節(jié)點(diǎn)更新模塊、判決模塊和反饋模塊,。圖3是這3個模塊的工作流程,。

2.1 量化位數(shù)及迭代次數(shù)設(shè)計(jì)

量化必然會損失信息,所以量化位數(shù)的設(shè)計(jì)對信息重建至關(guān)重要,。量化位數(shù)越多,,則信息損失越少,譯碼正確性越高,,但計(jì)算量會增加,、消耗的FPGA資源也越多;若量化位數(shù)太少,,丟失的信息過多,,雖然計(jì)算量減少、消耗FPGA資源減少,,但可能造成譯碼錯誤,。

文獻(xiàn)[8-9]中提出(q,f)均勻量化方案,,其中量化位數(shù)q=8,,因量化精度對譯碼性能影響很小,故取f=2足矣,。鑒于Xilinx XC7VX485T的邏輯資源相對豐富,,本文設(shè)計(jì)了(8,,2)、(9,,2),、(10,2),、(11,,2)4種量化方案,這4種量化方案經(jīng)ISE布局布線后消耗FPGA中一種重要資源指標(biāo)Slice Registers的情況如表1所示,。

根據(jù)面積換“速度”的思想,,提高FPGA資源利用率的同時(shí)增加譯碼的準(zhǔn)確性。因此,,根據(jù)表1可知(10,,2)均勻量化方案最適合本文DSC譯碼量化要求。

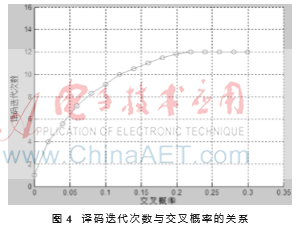

另一個重要的參數(shù)是譯碼迭代次數(shù),。通常碼長,、碼率相同時(shí),不同交叉概率對應(yīng)的譯碼迭代次數(shù)不同,。通過仿真AWGN信道下碼長2 048,、碼率1/2,、量化位數(shù)10 bits的信號,,得出交叉概率與譯碼迭代次數(shù)之間的關(guān)系,如圖4所示,。

圖4表明,,交叉概率變大時(shí),譯碼迭代次數(shù)隨之增加,。當(dāng)交叉概率超過0.2后,,譯碼迭代次數(shù)不再改變。所以本文設(shè)計(jì)譯碼迭代次數(shù)的最大值為12,。

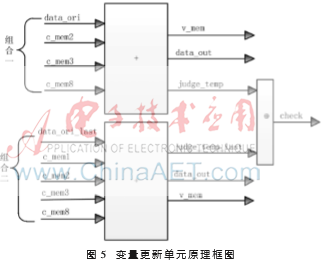

2.2 變量更新單元設(shè)計(jì)

從式(3)和式(4)可知,,變量節(jié)點(diǎn)的更新主要是加法運(yùn)算。初始信息與校驗(yàn)信息送入VNU更新變量節(jié)點(diǎn)并計(jì)算出各碼位判決控制信息,。其原理框圖如圖5所示,,由于H矩陣非規(guī)則,所以設(shè)計(jì)了兩種校驗(yàn)信息組合方式,。

其中,,data_ori、data_ori_last表示兩種組合狀態(tài)的初始信息,,c_mem1,、c_mem2、c_mem3、c_mem8表示分別與度為1,、2,、3、8的變量節(jié)點(diǎn)相連的校驗(yàn)節(jié)點(diǎn)信息,,v_mem表示更新后的變量節(jié)點(diǎn)信息,,judge_temp、judge_temp_last表示兩種組合狀態(tài)的中間判決信息,,check表示輸入判決模塊的最終判決信息,。

VNU計(jì)算完成后,將judge_temp,、judge_temp_last進(jìn)行異或運(yùn)算得到判決結(jié)果check,,如果判斷結(jié)果是0,則表示譯碼正確,,將譯碼結(jié)果送至串/并轉(zhuǎn)換模塊輸出,,否則表示譯碼錯誤。

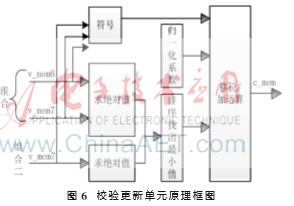

2.3 校驗(yàn)更新單元設(shè)計(jì)

根據(jù)式(2)可知,,更新校驗(yàn)節(jié)點(diǎn)信息需要求絕對值,、求符號、排序找出最小值,、移位和加運(yùn)算這4個步驟,。在式(2)中,雖然選擇合適的η可以將乘法全部轉(zhuǎn)化成移位和加法運(yùn)算,,但是大量的移位操作會占用過多的時(shí)鐘周期,,因此在CNU模塊的移位/加運(yùn)算中采用“流水移位/加運(yùn)算”的方式,這樣不但提高了時(shí)鐘利用率,、運(yùn)算效率,,也降低了FPGA資源的消耗。

CNU的原理框圖如圖6所示,,由于H矩陣非規(guī)則,,所以設(shè)計(jì)了兩種變量信息組合方式。

其中,,v_mem6,、v_mem7分別表示與度為6、7的校驗(yàn)節(jié)點(diǎn)相連的變量節(jié)點(diǎn)信息,, c_mem表示更新后的校驗(yàn)節(jié)點(diǎn)信息,。

3 DSC譯碼器設(shè)計(jì)結(jié)果分析

3.1 DSC譯碼器結(jié)構(gòu)分析

通常情況下,串行譯碼的譯碼效率最低,,全并行譯碼器的譯碼效率最高,,但是FPGA有限的邏輯資源限制了這種方法的實(shí)用性,。為了平衡FPGA資源的利用率和譯碼器的譯碼效率,本文采用部分并行的思想設(shè)計(jì)譯碼器,。

由于本文的H矩陣是非規(guī)則的,,不同度的節(jié)點(diǎn)組合在一起消耗的FPGA資源不一樣。綜合考慮運(yùn)算量,、FPGA資源,、占用時(shí)鐘周期等因素,設(shè)計(jì)VNU中組合一,、組合二的結(jié)構(gòu)如表2,、表3所示。

從表2,、表3中可以看出組合一的并行度是77,,組合二的并行度是46。所以VNU組合一經(jīng)過26個狀態(tài)以及VNU組合二經(jīng)過1個狀態(tài)可以完全更新變量節(jié)點(diǎn),。

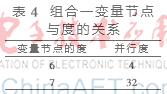

設(shè)計(jì)CNU中組合一,、組合二的結(jié)構(gòu)如表4、表5所示,。從表4,、表5中可以看出組合一的并行度是36,組合二的并行度是38,,所以CNU組合一經(jīng)過1個狀態(tài)以及CNU組合二經(jīng)過26個狀態(tài)可以完全更新校驗(yàn)節(jié)點(diǎn),。

3.2 DSC譯碼器時(shí)序圖

為了驗(yàn)證該DSC譯碼器設(shè)計(jì)的可行性,在MATLAB中隨機(jī)產(chǎn)生一段二進(jìn)制信息序列,,先進(jìn)行LDPC編碼,,再進(jìn)行AWGN信道加噪和BPSK調(diào)制,,得到初始化信息,,然后作10 bits均勻量化,將量化結(jié)果存入Block RAM中作為譯碼器輸入,。

該譯碼器正確譯碼一次的主要信號時(shí)序圖如圖7所示(為了清晰地顯示信號,,故將圖中的信號名重寫)。信號的含義如下:clk表示譯碼器的全局時(shí)鐘,,rst表示譯碼器的全局復(fù)位,,out_flag表示譯碼輸出標(biāo)志,out_en表示譯碼輸出使能,,iter_counter表示譯碼迭代次數(shù),,check表示譯碼判決信號,data_out表示譯碼輸出,。圖7(b),、圖7(c)是圖7(a)中a,、b局部放大后的圖。

從圖7(b)可以看出該譯碼器經(jīng)過10次循環(huán)迭代后,,判決信息輸出為0,,說明譯碼器譯碼正確。對比MATLAB產(chǎn)生的二進(jìn)制信息序列,,表明譯碼輸出結(jié)果與產(chǎn)生的二進(jìn)制信息序列完全一致,,至此證明了該譯碼器設(shè)計(jì)是正確的。

3.3 DSC系統(tǒng)壓縮性能

一般而言,,信源的交叉概率越大,,正確譯碼所需的校驗(yàn)位個數(shù)越多。為驗(yàn)證本文設(shè)計(jì)的DSC系統(tǒng)的壓縮性能,,通過改變信源的交叉概率測試正確譯碼需要的校驗(yàn)位個數(shù),,并與MATLAB中設(shè)計(jì)的DSC系統(tǒng)對比。本文設(shè)計(jì)的DSC系統(tǒng)與MATLAB中設(shè)計(jì)的DSC系統(tǒng)壓縮性能對比如圖8所示,。

從圖8中可知,,在FPGA和MATLAB實(shí)現(xiàn)的DSC系統(tǒng)中,正確譯碼所需的校驗(yàn)位個數(shù)都隨交叉概率增加而增加,。當(dāng)交叉概率相同時(shí),,本文設(shè)計(jì)實(shí)現(xiàn)的DSC系統(tǒng)比MATLAB仿真的DSC系統(tǒng)需要更多的校驗(yàn)位才能正確譯碼,主要原因是受FPGA資源限制導(dǎo)致量化位數(shù)不夠并且FPGA在布局布線時(shí)有延遲,。

該DSC高速譯碼器在Xilinx XC7VX485T上實(shí)現(xiàn),,ISE完成布局布線消耗的FPGA資源如表6所示。

經(jīng)過時(shí)序約束,,譯碼器最大工作頻率f可達(dá)195.048 MHz,,譯出一個碼字需要169個時(shí)鐘。根據(jù)吞吐率計(jì)算公式N×f/(k×T),,其中N是碼長,,f是時(shí)鐘工作頻率,k是最大譯碼迭代次數(shù),,T是譯出一個碼字的周期,,則譯碼吞吐率可達(dá)197 Mb/s。

4 結(jié)束語

本文針對當(dāng)前DSC譯碼器譯碼實(shí)時(shí)性差,、譯碼效率低等因素設(shè)計(jì)了一種全新的,、高速部分并行的DSC譯碼器,并在Xilinx XC7VX485T芯片上實(shí)現(xiàn),,在設(shè)計(jì)時(shí)最大限度平衡了FPGA資源,、譯碼復(fù)雜度和譯碼效率。該DSC譯碼器的設(shè)計(jì)具有一般性,、便于移植等特點(diǎn),,其高達(dá)197 Mb/s的吞吐率,,使該DSC譯碼器具有較強(qiáng)的工程實(shí)用性。

參考文獻(xiàn)

[1] 楊春玲,,夏洪濤,,張興紹.基于LDPC的碼率自適應(yīng)分布式視頻編碼[J].中國圖象圖形學(xué)報(bào),2010,,15(12):1707-1713.

[2] CHUNG S Y,,F(xiàn)ORNEY G D,RICHARDSON T J,,et al.On the design of low-density parity-check codes with in 0.004 5 dB of the Shannon limit[J].Communications Letters,,IEEE,2001,,5(2):58-60.

[3] 薛國棟.分布式信源編碼理論與應(yīng)用研究[D].北京:北京郵電大學(xué),,2009.

[4] WANG J,YANG S H.A novel log-BP decoding algorithm for LDPC codes[C].Software Engineering,,2009.WCSE'09.WRI World Congress on.IEEE,,2009,1:305-307.

[5] JIANG N,,PENG K,,SONG J,et al.High-throughput QCLDPC decoders[J].Broadcasting,,IEEE Transactions on,,2009,55(2):251-259.

[6] 姜博宇,,姚遠(yuǎn)程,,秦明偉.硬件可實(shí)現(xiàn)的LDPC譯碼算法研究[J].現(xiàn)代電子技術(shù),2014,,37(17):5-8.

[7] COLE C.Error floor analysis for an ensemble of easily implementable irregular(2048,,1024) LDPC codes[C].Military Communications Conference,2008.MILCOM 2008.IEEE.IEEE,,2008:1-5.

[8] 劉文燾,,李強(qiáng),李少謙.π—旋轉(zhuǎn)LDPC碼譯碼算法及其量化研究[J].信息技術(shù),,2006,29(11):38-40.

[9] 吳斌,,楊波,,葉明.LDPC硬件實(shí)現(xiàn)中的數(shù)據(jù)量化位數(shù)選擇及其性能仿真[J].信息通信,2012(2):24-26.