文獻(xiàn)標(biāo)識(shí)碼: A

DOI:10.16157/j.issn.0258-7998.2016.08.007

中文引用格式: 林慧,蔣武,熊熙,等. Verifier提高驗(yàn)證完備性[J].電子技術(shù)應(yīng)用,2016,42(8):37-40,43.

英文引用格式: Lin Hui,Jiang Wu,Xiong Xi,et al. Verifier-Improve the simulation verification completeness[J].Application of Electronic Technique,2016,42(8):37-40,43.

1 介紹

ADE Explorer、ADE Assembler是Cadence Virtuoso ADE一系列產(chǎn)品的重要模擬設(shè)計(jì)驗(yàn)證工具,將驗(yàn)證技術(shù)可視化,能夠很好地支持工程師子模塊的模擬設(shè)計(jì)驗(yàn)證,大大提高了驗(yàn)證效率。現(xiàn)有的驗(yàn)證直接根據(jù)仿真結(jié)果來(lái)決定驗(yàn)證設(shè)計(jì)的好壞與否。這種驗(yàn)證流程簡(jiǎn)單有效,但是也有其弊端——規(guī)格無(wú)標(biāo)準(zhǔn)可循、難以覆蓋更高層的設(shè)計(jì),導(dǎo)致難以及時(shí)發(fā)現(xiàn)并規(guī)避設(shè)計(jì)更深層的問(wèn)題。在整合了ADE Explorer、ADE Assembler強(qiáng)大的簡(jiǎn)單有效的驗(yàn)證功能的基礎(chǔ)上,ADE Verifier在驗(yàn)證流程上做了進(jìn)一步的優(yōu)化,能夠有效彌補(bǔ)現(xiàn)有模擬設(shè)計(jì)驗(yàn)證存在的不足,很大程度上提高了模擬設(shè)計(jì)驗(yàn)證的可靠性和完備性。ADE Verifier特性如圖1所示。

圖1 ADE Verifier特性

2 Verifier驗(yàn)證流程

Verifier支持自頂向下、自下向上、混合的設(shè)計(jì)方法。本文描述Verifier自頂向下的設(shè)計(jì)方法。根據(jù)客戶(hù)需求、業(yè)務(wù)場(chǎng)景和條件等原始需求,項(xiàng)目管理者(PM/PL)整合原始需求,轉(zhuǎn)換成設(shè)計(jì)語(yǔ)言,細(xì)化、分解設(shè)計(jì)需求。然后將整個(gè)需求分配給不同的工程師。根據(jù)分配得到的需求,工程師深入理解設(shè)計(jì)需求,量化相應(yīng)的設(shè)計(jì)規(guī)格,并設(shè)計(jì)仿真用例和測(cè)試用例,完成仿真。然后將需求設(shè)計(jì)和規(guī)格設(shè)計(jì)進(jìn)行最后,工程師提交驗(yàn)證數(shù)據(jù),項(xiàng)目管理者就可以及時(shí)觀測(cè)驗(yàn)證結(jié)果,跟蹤項(xiàng)目驗(yàn)證進(jìn)度。ADE Verifier驗(yàn)證流程如圖2所示。

圖2 ADE Verifier驗(yàn)證流程

2.1 項(xiàng)目管理者建立Requirement

需求的建立有兩種方式,一是項(xiàng)目管理者在verifier里面創(chuàng)建的,二是直接導(dǎo)入指定格式的需求表格,包括csv文件和excel文件。

需求的內(nèi)容包括項(xiàng)目名稱(chēng),模塊名稱(chēng),指標(biāo)的最大值與最小值、指標(biāo)的單位、責(zé)任人、類(lèi)型以及詳細(xì)的描述等。指標(biāo)的最大值與最小值、指標(biāo)的單位都是作為后續(xù)規(guī)格設(shè)計(jì)的約束。內(nèi)容可以由中文、英文、日語(yǔ)、德語(yǔ)、北印度語(yǔ)5種語(yǔ)言組成。

需求的類(lèi)型包括以下幾種:Note,Spec Pass,Ran OK,Manual。Note類(lèi)型的需求是不需要仿真驗(yàn)證;Spec Pass類(lèi)型和Ran OK類(lèi)型的需求是可以進(jìn)行仿真驗(yàn)證的,二者差別就是Spec Pass類(lèi)型的需求要考慮需求設(shè)計(jì)的指標(biāo)值來(lái)決定需求的狀態(tài),Ran OK類(lèi)型的需求只會(huì)根據(jù)仿真結(jié)果來(lái)決定需求的狀態(tài);Manual類(lèi)型的需求是指是要人為判斷設(shè)計(jì)的成功與否,而不是直接簡(jiǎn)單地根據(jù)仿真結(jié)果來(lái)決定。

需求是Hierarchy結(jié)構(gòu)的。從頂層模塊開(kāi)始進(jìn)行需求設(shè)計(jì),細(xì)化到每個(gè)子模塊的需求設(shè)計(jì),直到完成整個(gè)項(xiàng)目的需求設(shè)計(jì)。每個(gè)需求設(shè)計(jì)都會(huì)指定一個(gè)責(zé)任人,后續(xù)每個(gè)責(zé)任人都只需要對(duì)各自被分配到的需求負(fù)責(zé)人。

在現(xiàn)有的整個(gè)項(xiàng)目需求設(shè)計(jì)基礎(chǔ)上,可以新增需求、刪除現(xiàn)有需求、編輯現(xiàn)有需求。

2.2 項(xiàng)目管理者分配Requirement

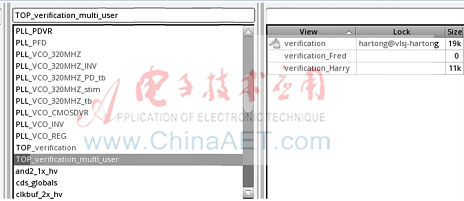

根據(jù)需求責(zé)任人,可以將master verification分成幾個(gè)不同的owner verification。每個(gè)責(zé)任人只需要著眼于own verification,根據(jù)被分配到的需求進(jìn)行規(guī)格設(shè)計(jì)。如圖3所示,F(xiàn)red、Harry是master verification的責(zé)任人,分配需求時(shí),會(huì)生成相應(yīng)的verification_Fred和verification_Harry。之后,F(xiàn)red和Harry只需要分別修改、完善verification_Fred 和 verification_Harry即可。

圖3 分配Requirement

2.3 工程師添加Implementation

根據(jù)需求設(shè)計(jì),工程師進(jìn)行相應(yīng)的Implementation,支持adel、adexl、maestro類(lèi)型的文件。如圖4所示。

圖4 工程師添加Implementation

2.4 工程師建立Mapping

工程師根據(jù)自己分配到的任務(wù),建立testbench,和Requirement建立映射。Requiremment與SPEC之間可以是n:1或者1:n的關(guān)系。

需求的mapping有6種狀態(tài):Pass,F(xiàn)ail,No Results,Mapped,Unmapped,Spec check failed。

Pass是指在requirement的specification與implementation的specification保持一致的前提下,requirement的specification和仿真結(jié)果保持一致。

Fail是指在requirement的specification與implementation的specification保持一致的前提下,requirement的specification和仿真結(jié)果不同。

No Results是指在requirement的specification與implementation的specification保持一致的前提下,implementation沒(méi)有仿真結(jié)果。

Mapped是指requirement的specification與implementation的specification保持一致。

Unmapped是指requirement還沒(méi)有建立mapping。

Spec Check Failed是指如果requirement的specification與implementation的specification不能保持一致。

2.5 工程師加載、提交個(gè)人Result

Verifier提供了兩種加載結(jié)果的方式:直接跑仿真和加載仿真結(jié)果。

Verifier呈現(xiàn)的結(jié)果包括整個(gè)項(xiàng)目的結(jié)果百分比,以及每個(gè)模塊、需求的結(jié)果。需求的結(jié)果狀態(tài)分為兩種:Requirement Status 和Specification Status。Specification Status是根據(jù)spec的結(jié)果而定;Requirement Status是根據(jù)spec結(jié)果以及map結(jié)果而定。加載個(gè)人Results如圖5所示。

圖5 加載個(gè)人Results

2.6 項(xiàng)目管理者查看項(xiàng)目Result

等到工程師提交了個(gè)人結(jié)果之后,項(xiàng)目管理者就可以查看整個(gè)項(xiàng)目的驗(yàn)證進(jìn)展和驗(yàn)證結(jié)果。如圖6所示。

圖6 查看項(xiàng)目Results

3 Hisilicon Verifier

3.1 定制化特性

根據(jù)海思的業(yè)務(wù)需求,在原有ADE Verifier平臺(tái)上,添加了定制化特性,有以下兩點(diǎn):

(1)導(dǎo)入的requirement表格形式:通過(guò)新增列數(shù),直觀地呈現(xiàn)需求之間的Hierachy結(jié)構(gòu);

(2)結(jié)果的保存與呈現(xiàn):通過(guò)收集工程師提交的結(jié)果,保存到數(shù)據(jù)庫(kù)。保存結(jié)果能夠讓現(xiàn)有項(xiàng)目傳承歷史項(xiàng)目的優(yōu)良基因;展示結(jié)果從項(xiàng)目和owner的維度展示數(shù)據(jù),能夠讓項(xiàng)目管理者直觀看到整個(gè)項(xiàng)目的驗(yàn)證進(jìn)展,讓工程師清晰認(rèn)識(shí)到自己模塊的進(jìn)度。Hisilicon Verifier Results如圖7所示。

圖7 Hisilicon Verifier Results

3.2 定制化流程

在工程師提交verification時(shí)候,結(jié)果數(shù)據(jù)就會(huì)被收集。為了適配定制化特性——收集結(jié)果數(shù)據(jù),整理了使用verifier的三種流程,這三種流程都能夠保證收集到數(shù)據(jù)。為了能夠清晰描述三種流程的特點(diǎn),假設(shè)背景如下:工程P,項(xiàng)目經(jīng)理是M,工程師E1,E2,E3。M新建一個(gè)verification,設(shè)置result路徑為Current cellview,這樣結(jié)果文件就在相應(yīng)的verification路徑下。分配任務(wù),生成verification_E1, verification_E2, verification_E3。項(xiàng)目經(jīng)理M check in verification,verification_E1, verification_E2, verification_E3。如圖8~圖11所示。

(1)流程1(如圖8)

圖8 項(xiàng)目背景

Step1:

E1 新建maestre_E1,搭建testbench,跑仿真;

Step2:

E1 Check out verification_E1,和maestre_E1建立Map,加載結(jié)果,check in verification_E1,這樣才能收集到數(shù)據(jù);

Step3:

E1 Check in maestre_E1,這樣M,E2,E3才能看到E1的結(jié)果;

(2)流程2(如圖9)

圖9 流程1

Step1:

E1 新建maestre_E1,搭建testbench,跑仿真;

Step2:

E1 Check out verification_E1,和maestre_E1建立Map,加載結(jié)果,check in verification_E1,這樣才能收集數(shù)據(jù);

Step3:

E1 Check out verification,load E1的結(jié)果,check in verification,這樣M,E2,E3才能看到E1的結(jié)果;

(3)流程3(如圖10)

圖10 流程2

Step1:

E1 新建maestre_E1,搭建testbench,跑仿真;

Step2:

E1 Check out verification_E1,和maestre_E1建立Map,加載結(jié)果,check in verification_E1;

這三個(gè)流程都能夠達(dá)到收集數(shù)據(jù)以及呈現(xiàn)最新結(jié)果的目的,但是流程1和流程2都有其弊端。

流程1中,要想工程師的結(jié)果被其他人看到,必須提交maestre。首先,maestre很大,提交很費(fèi)時(shí)。其次,maestre保存的是過(guò)程配置信息,不適合提交。

流程2中,整個(gè)項(xiàng)目組都需要操作一份文件—verification,很容易產(chǎn)生寫(xiě)沖突,不適合大項(xiàng)目、異地項(xiàng)目的合作。另外,工程師需要操作owner verification 和master verification,職責(zé)不夠分明。

流程3,只需要選擇HISILICON_VERIFIER為yes,這樣加載結(jié)果來(lái)源是結(jié)果的快照文件。提交owner verification,即可收集數(shù)據(jù),也可以保證其他人都能看到結(jié)果。職責(zé)分明,操作簡(jiǎn)單。

所以,Hisilicon Verifier采用流程3。

圖11 流程3

4 驗(yàn)證完備性

4.1 完備性問(wèn)題

以Hisilicon的驗(yàn)證流程進(jìn)行分析,從制定原始需求開(kāi)始,到編寫(xiě)測(cè)試用例,驗(yàn)證完備性的突出問(wèn)題如下。

(1)OR:遺漏、客戶(hù)自己不清楚;

(2)DR:功能/隱形需求遺漏;

(3)DS:內(nèi)部規(guī)格未細(xì)化、規(guī)格條件不合理、非典電路規(guī)格不全。

4.2 Verifier方案

基于Verifier的驗(yàn)證流程,驗(yàn)證完備性問(wèn)題能夠在很大程度上得到解決。

(1)需求設(shè)計(jì)、規(guī)格設(shè)計(jì)、仿真等整個(gè)驗(yàn)證流程都是需求驅(qū)動(dòng)的,保證了需求的可溯性。

(2)從上至下的驗(yàn)證流程,既保證了各個(gè)模塊之間相互獨(dú)立,互不干擾,也保證了各個(gè)子模塊之間無(wú)縫契合。

(3)記錄仿真結(jié)果,自動(dòng)復(fù)現(xiàn)仿真結(jié)果,將仿真過(guò)程變得更加可溯和自動(dòng)化。

(4)當(dāng)工程師改變了某個(gè)設(shè)計(jì)模塊,verifier具有聯(lián)想功能,能夠提示相關(guān)testbench需要重新進(jìn)行仿真,進(jìn)一步確保驗(yàn)證完備性。

5 結(jié)語(yǔ)

通過(guò)使用ADE Verifier工具,我們將在電路設(shè)計(jì)中解決由于驗(yàn)證不完備性的各種問(wèn)題。這種問(wèn)題在很大程度上是可以通過(guò)完善的驗(yàn)證流程去規(guī)避的。在海思的驗(yàn)證設(shè)計(jì)實(shí)踐中,Virtuoso ADE驗(yàn)證工具技術(shù)與Virtuoso ADE組裝工具技術(shù)具備設(shè)計(jì)規(guī)劃能力,讓設(shè)計(jì)團(tuán)隊(duì)更加高效,提升了模擬IP驗(yàn)證效率將近30%,驗(yàn)證發(fā)現(xiàn)的問(wèn)題數(shù)量減少了一半。所以,ADE Verifier是驗(yàn)證設(shè)計(jì)中不可或缺的工具之一。