蔡潔明,魏敬和

(中國電子科技集團公司第五十八研究所,江蘇 無錫 214035)

摘要:提出了一種適用于高速1553總線的分立器件收發(fā)器電路設(shè)計方法,解決了傳統(tǒng)1 MHz 1553收發(fā)器無法與10 MHz協(xié)議處理器接口的問題。與其他方案相比,由于采用的是分立器件搭建,不改變原有的總線結(jié)構(gòu),不用改換線纜及接口方式,節(jié)省了大量成本與時間,實現(xiàn)起來靈活方便,同時具有很好的通用性和強大的可擴展性。

關(guān)鍵詞:分立器件;高速1553總線;LDMOS;濾波器;比較器

中圖分類號:TN710文獻標識碼:ADOI: 10.19358/j.issn.1674 7720.2016.20.009

引用格式:蔡潔明,魏敬和. 高速1553總線分立器件收發(fā)器設(shè)計[J].微型機與應(yīng)用,2016,35(20):34 36.

0引言

MIL-STD-1553數(shù)據(jù)總線因其高可靠性特諸多優(yōu)點被廣泛應(yīng)用于航空、航天等多個領(lǐng)域。在過去的半個多世紀,它實現(xiàn)了傳感器、武器等各種電子裝備的信息共享與傳輸。但隨著更快處理器的誕生以及封裝的小型化和軟件技術(shù)的革新,1553B僅僅1 Mb/s的數(shù)據(jù)傳輸速度無疑成為了信息數(shù)據(jù)傳輸?shù)钠款i,一種更快速度的傳輸方式應(yīng)運而生[1-2]。1553總線歷經(jīng)了1553A、1553B再到1553C的三個重要的發(fā)展階段,傳輸速度也從最先的1 Mb/s變成了10 Mb/s甚至更高。目前國外已經(jīng)有了較為成熟的1553C產(chǎn)品,但我國在高速1553總線方面的研究尚處于起步階段。由于國外在高速1553總線上采取技術(shù)封鎖,因此國內(nèi)只能在研究1553B總線的基礎(chǔ)上開發(fā)自己的1553C產(chǎn)品。

除了支持高速數(shù)據(jù)處理的1553C協(xié)議處理器外,相應(yīng)的高速收發(fā)器電路由于與外部總線相連,其穩(wěn)定性和可靠性至關(guān)重要,因而成為整個1553C總線電路設(shè)計的關(guān)鍵[3]。目前高速1553收發(fā)器的研制開發(fā)單位主要集中在部分科研院所和大學,但由于國內(nèi)尚未出臺針對高速1553收發(fā)器的標準,盡管有高速1553收發(fā)器電路問世,但各家產(chǎn)品的性能指標不盡相同。從實現(xiàn)形式上大致可以把目前開發(fā)出的1553高速收發(fā)器分為兩類:一類是基于原低速1553收發(fā)器進行設(shè)計參數(shù)的調(diào)整,使其工作于10 MHz甚至更高速率;另一類是采用市場上其他通用型收發(fā)器替代1553收發(fā)器,如485總線收發(fā)器等,其速率也可以達到10 MHz[4]。但兩種方案均存在一定的缺陷:采用更改設(shè)計參數(shù)的方式由于受到原電路設(shè)計的局限,調(diào)整幅度不能太大,電路通常需要進行全套改版,需要投入的成本很高。采用其他通用型收發(fā)器的方案盡管芯片本身不用重新設(shè)計,但原來的傳輸介質(zhì)都需要更換,整個系統(tǒng)需要重新布局,投入的成本也不容小覷。

本文設(shè)計的1553總線收發(fā)器克服了上述兩種方案的缺陷,采用市場上常用的分立器件進行搭建,價格較低且容易采購,可以利用原系統(tǒng)進行通信,無需作任何調(diào)整,兼顧了電路設(shè)計與后期重新布局的成本。此外,該設(shè)計還具有很好的可擴展性,當收發(fā)器參數(shù)需要進行調(diào)整時,只需簡單更換型號不同的分立器件即可,既方便了調(diào)試,又降低了成本。

1電路組成及原理

本文設(shè)計的分立器件收發(fā)器的典型工作速率為10 MHz,由發(fā)送器與接收器兩部分組成。

發(fā)送器與協(xié)議處理器銜接,完成10 MHz曼徹斯特碼的發(fā)送,它由電壓轉(zhuǎn)換驅(qū)動器電路、高速功率晶體管LDMOS(NMOS)及一定阻值和容值的電阻電容構(gòu)成。

電壓轉(zhuǎn)換驅(qū)動器電路采用TI公司的SN74LVC2T45,它是一款雙向帶三態(tài)輸出的電壓轉(zhuǎn)換驅(qū)動器[5]。由于協(xié)議處理器送給發(fā)送器的為3.3 V信號,為了保證數(shù)據(jù)高速傳輸時LDMOS的漏端有足夠大的電流,需要將柵極的電壓抬高。SN74LVC2T45可以將10 MHz、3.3 V的電平信號轉(zhuǎn)換為10 MHz、5 V的信號。同時,其中一個電源端口VCCA可以用作發(fā)送器的使能端,用于控制發(fā)送器是否進入工作狀態(tài)。

LDMOS采用NXP公司的高速功率晶體管BLF6G21-10G,其開關(guān)速度可達2 200 MHz,開啟電壓1.9 V,且在柵源電壓達到5.65 V時,漏極電流可達3.1 A,輸入輸出電容在幾pF到十幾pF之間[6],可以滿足發(fā)送器設(shè)計要求。

隔離變壓器采用國內(nèi)某研究所定制的10 MHz變壓器。該變壓器專為高速1553收發(fā)器設(shè)計,經(jīng)過長期的壽命及可靠性試驗,各項參數(shù)指標滿足高速1553總線傳輸要求。要注意的是,由于輸出端采用的是NMOS,變壓器輸入端的中間抽頭(2腳)必須接+5 V的電源。

發(fā)送器的原理框圖如圖1所示。

如圖1所示的分立器件發(fā)送器,協(xié)議處理器產(chǎn)生一對差分信號Txa、Txa_n送至SN74LVC2T45的A1、A2端口,SN74LVC2T45的電源端VCCA通過跳線選擇3.3 V電源或GND,以控制發(fā)送器的開啟與關(guān)斷,電源端VCCB接5.0 V電源,這是由于協(xié)議處理器采用3.3 V標準的端口電壓,為了保證LDMOS有足夠大的電流以驅(qū)動下一級,將協(xié)議處理器輸出的信號經(jīng)過電平轉(zhuǎn)換器件轉(zhuǎn)換至5 V電壓。方向控制端DIR接高電平,使數(shù)據(jù)信號由A端送至B端。接地端GND與電路板的地端相連。經(jīng)過電平轉(zhuǎn)換后的信號通過10 Ω電阻以減少信號反射。接著兩路差分信號被分別送至兩個LDMOS管的柵極(Pin2),源極(Pin3)跟襯底連在一起接到地,漏極(Pin1)作為輸出并串接2 Ω電阻至變壓器的初級端(Pin1、Pin3),LDMOS的柵極與漏極跨接100 pF的反饋電容用于調(diào)整信號的階梯現(xiàn)象。信號經(jīng)過隔離變壓器至次級,負載接于隔離變壓器的引腳5與引腳7之間。發(fā)送器的工作原理如下。

當Txa對應(yīng)的曼碼為高電平時,Txa_n對應(yīng)的曼碼應(yīng)為低電平,這時,圖1中的第一功率MOS管導(dǎo)通,于是變壓器1號抽頭被拉至地,電流從中間抽頭(Pin2)往1號抽頭流,在變壓器輸入端的3號抽頭與中間抽頭之間耦合產(chǎn)生方向相反的電流,這樣1、3號抽頭之間就形成了正負電平的曼碼;同理,當Txa_n對應(yīng)于曼碼為高電平時,Txa對應(yīng)的曼碼應(yīng)為低電平,這時,第二功率MOS管導(dǎo)通,于是變壓器3號抽頭被拉至地,電流從中間抽頭往3號抽頭流。在變壓器輸入端的1號抽頭與中間抽頭之間耦合產(chǎn)生相反的電流,這樣1、3號抽頭之間同樣形成了正負電平的曼碼。

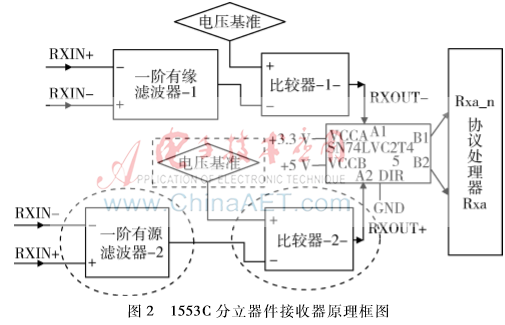

接收器部分從1553總線上接收10 MHz的曼徹斯特碼,通過濾波、比較、電平轉(zhuǎn)換產(chǎn)生與協(xié)議處理器匹配的TTL電平信號。接收器原理框圖如圖2所示。

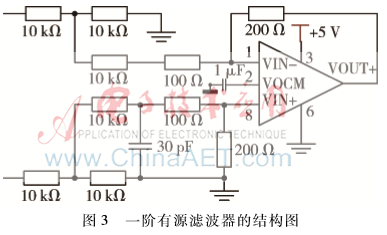

濾波器采用TI公司的高速運算放大器THS4521搭建的一階有源濾波器。THS4521帶寬可以達到145 MHz,轉(zhuǎn)換速率達到490 V/μs[7],可以滿足要求。一階有源濾波器的結(jié)構(gòu)如圖3所示。

發(fā)送器輸出的差分信號經(jīng)1/2分壓后連接至其差分輸入端(Pin1、Pin8),以降低共模電壓信號使運放能夠正常響應(yīng)。電源Vs+(Pin3)接+5 V,Vs-(Pin6)接地,共模電壓輸入端VOCM(Pin2)接0.1 μF電容到地,以降低管腳上的耦合噪聲。

對于一階有源濾波器,其截止頻率為:

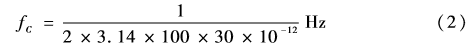

通過選取合適的R、C值可以使一定頻率范圍內(nèi)的信號通過。為了避免高頻噪聲信號對正常曼碼的影響,在這里選取: 代入式(1)有:

代入式(1)有:

計算得到截止頻率為fC=53 MHz,可以滿足五次諧波分量通過,更高頻率的諧波(大多是噪聲)被濾走。

為了能夠使比較器有較高的靈敏度,需要將濾波器的輸出信號進行放大,這里選擇放大倍數(shù)為6。因此,在運算放大器的正輸出VOUT+(Pin4)與負輸入端VIN-(Pin1)跨接反饋電阻RF。

運算放大器的放大倍數(shù)由下式?jīng)Q定:

有源濾波器的輸出被接至比較器,比較器采用ADI公司的超快速比較器AD8611,該器件輸入端的頻率可以達到100 MHz,且在5 V工作電壓下有4 ns的延時[8]。比較器中的電壓基準采用NS的LM4120-1.8,它能提供穩(wěn)定的1.8 V輸出電壓基準[9]。比較器的門限定為1.8 V,因此當濾波器輸出波形的電平高于1.8 V時,輸出電平為高(+5 V),輸出電平低于1.8 V時,輸出電平為低(0 V)。這樣,經(jīng)過總線傳輸之后的曼徹斯特碼就被濾波整形,防止噪聲信號使協(xié)議處理器產(chǎn)生誤操作。

最后,輸出的5 V信號要經(jīng)過電平轉(zhuǎn)換電路,將其轉(zhuǎn)換為協(xié)議處理器可以接收的3.3 V電平信號。輸入端A1、A2分別接RXOUT-、RXOUT+,與發(fā)送器中的電壓轉(zhuǎn)換驅(qū)動器接法不同的是,接收器不需要使能控制,故VCCA接固定的3.3 V電平,DIR接地,以使數(shù)據(jù)信號由B端送至A端。輸出的信號B1、B2被分別送至協(xié)議處理器的Rxa_n、Rxa端口。

2電路驗證及測試結(jié)果

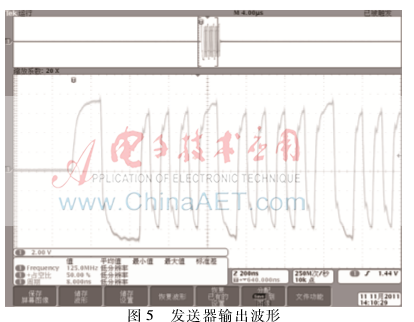

在變壓器的差分輸出端串接55 Ω電阻,再跨接35 Ω負載,如圖4所示。根據(jù)規(guī)范要求,在直接耦合的情況下,負載兩端電壓Vpp值Uout應(yīng)在7~9 V之間[10]。

發(fā)送器的輸出波形如圖5所示。

經(jīng)過比較器之后的波形如圖6所示。

3結(jié)束語

本文提出了一種針對10 MHz 1553總線協(xié)議處理器的接收發(fā)送電路,解決了1 MHz 1553收發(fā)器無法與10 MHz協(xié)議處理器接口的問題。由于采用的是分立器件搭建,省去了昂貴的流片費用,實現(xiàn)起來靈活方便,即便是以后需要更高速度的收發(fā)器,也只需要調(diào)整濾波器的濾波電阻電容就可以滿足要求,具有很好的通用性和強大的可擴展性。它不改變原有的總線結(jié)構(gòu),不用改換線纜及接口方式,節(jié)省了大量成本與時間。隨著更快處理器的誕生、封裝的小型化以及軟件技術(shù)的革新,信息的高速傳輸與實時共享已經(jīng)成為一種必然趨勢,采用分立器件的高速1553收發(fā)器電路無疑將代替?zhèn)鹘y(tǒng)的收發(fā)器以適應(yīng)快速發(fā)展的總線傳輸需求。

參考文獻

[1] 熊華鋼.1553B總線通信技術(shù)的應(yīng)用與發(fā)展[J]. 電子技術(shù)應(yīng)用,1997,23(8):27-28.

[2] 劉士全,黃正,蔡潔明,等. 1553B總線應(yīng)用競爭訪問時序分析[J]. 微型機與應(yīng)用,2015,34(1):69-71.

[3] 李海軍,牟俊杰,孫海文. 高速1553B總線控制器通信管理系統(tǒng)設(shè)計[J]. 現(xiàn)代電子技術(shù),2014,37(17):16-18.

[4] KELLER J. Rebirth of the 1553 databus[EB/OL].(2006-02-01)[2016-04-29]http://www.militaryaerospace.com/index.html.

[5] TI. Dual bit dual supply bus transceiver with configurable voltage translation and 3 state outputs[Z]. 2007.

[6] NXP. BLF6G21 10G, power LDMOS transistor product data sheet[Z]. 2009.

[7] TI. Very low power, negative rail input, rail to rail output, fully differential amplifier[Z]. 2010.

[8] ADI. Ultrafast, 4 ns Single Supply Comparators[Z]. 2006.

[9] NS. Precision micropower low dropout voltage reference[Z]. 2005.

[10] DDC. ACE/mini ACE series BC/RT/MT advanced communication engine integrated 1553 terminal user’s guide[Z]. 2008.