補(bǔ)充:

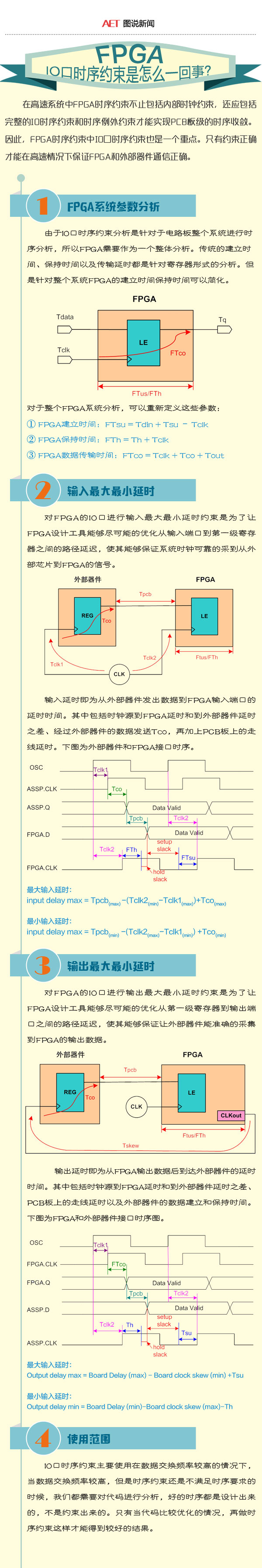

一、參數(shù)定義:

(1) Tdin為從FPGA的IO口到FPGA內(nèi)部寄存器輸入端的延時(shí);

(2) Tclk為從FPGA的IO口到FPGA內(nèi)部寄存器時(shí)鐘端的延時(shí);

(3) Tus/Th為FPGA內(nèi)部寄存器的建立時(shí)間和保持時(shí)間;

(4) Tco為FPGA內(nèi)部寄存器傳輸時(shí)間;

(5) Tout為從FPGA寄存器輸出到IO口輸出的延時(shí);

(6)Tpcb為PCB走向延遲。

二、進(jìn)行輸入最大最小延時(shí)的計(jì)算,我們需要估算4個(gè)值:

(1) 外部器件輸出數(shù)據(jù)通過(guò)PCB板到達(dá)FPGA端口的最大值和最小值Tpcb,PCB延時(shí)經(jīng)驗(yàn)值為600mil/ns,1mm = 39.37mil;

(2) 外部器件接收到時(shí)鐘信號(hào)后輸出數(shù)據(jù)延時(shí)的最大值和最小值Tco;

(3) 時(shí)鐘源到達(dá)外部器件的最大、最小時(shí)鐘偏斜Tclk1;

(4) 時(shí)鐘源到達(dá)FPGA的最大、最小時(shí)鐘偏斜Tclk2。

三、進(jìn)行輸出最大最小延時(shí)的計(jì)算,我們需要估算4個(gè)值:

(1) FPGA輸出數(shù)據(jù)通過(guò)PCB板到達(dá)外部器件輸入端口的最大值和最小值Tpcb,PCB延時(shí)經(jīng)驗(yàn)值為600mil/ns,1mm = 39.37mil;

(2) 時(shí)鐘源到達(dá)外部器件的最大、最小時(shí)鐘偏斜Tclk2;

(3) 時(shí)鐘源到達(dá)FPGA的最大、最小時(shí)鐘偏斜Tclk1;

(4) 外部器件的建立時(shí)間Tsu和保持時(shí)間Th。