王炳文

(中國航空工業(yè)集團(tuán)公司西安航空計(jì)算技術(shù)研究所,陜西 西安 710065)

摘要:針對某精密數(shù)據(jù)采集系統(tǒng)中模擬信號(hào)同步采樣問題,文章研究了多通道同步模擬信號(hào)采集方法,設(shè)計(jì)了一種基于SAR-ADC、使用FPGA控制的16位同步采樣AD轉(zhuǎn)換系統(tǒng)。該系統(tǒng)可實(shí)現(xiàn)模擬信號(hào)的實(shí)時(shí)同步采樣,同時(shí)兼顧多路模擬信號(hào)采樣頻率要求的差異性,最后通過試驗(yàn)測試了該系統(tǒng)的信納比(SINAD)和有效位數(shù)(ENOB)。測試結(jié)果表明,該系統(tǒng)具有良好的動(dòng)態(tài)性能指標(biāo)。

關(guān)鍵詞:SAR-ADC;同步采樣;FPGA

中圖分類號(hào):TP353文獻(xiàn)標(biāo)識(shí)碼:ADOI: 10.19358/j.issn.1674-7720.2017.07.009

引用格式:王炳文.基于SARADC的精密同步數(shù)據(jù)采集系統(tǒng)設(shè)計(jì)[J].微型機(jī)與應(yīng)用,2017,36(7):29-31,34.

0引言

在慣性測量[1]、功率因數(shù)校正[2]、電機(jī)控制等工業(yè)應(yīng)用場合,系統(tǒng)需要采集同一時(shí)刻來自多個(gè)傳感器的模擬信號(hào),并根據(jù)當(dāng)前的狀態(tài)進(jìn)行計(jì)算和控制。有時(shí)候系統(tǒng)的動(dòng)態(tài)范圍可能會(huì)很大,要求的采樣頻率很高,這種情況下如何兼顧系統(tǒng)的快速性和精密性,使之性能最優(yōu),是一個(gè)較為關(guān)鍵的設(shè)計(jì)難點(diǎn)。

1概述

在實(shí)現(xiàn)同步采樣的過程中,有多個(gè)因素需要考慮,這些因素大多都是與時(shí)間及空間相關(guān)的。時(shí)間是指系統(tǒng)所要求的采樣頻率,空間是指系統(tǒng)需采集的通道數(shù)量。

在進(jìn)行設(shè)計(jì)時(shí),首先應(yīng)明確同步采樣的通道數(shù),一般相位敏感信號(hào)往往需要同步采樣,如計(jì)算交流瞬時(shí)功率P時(shí)的電流I和電壓V。很多時(shí)候并不是所有信號(hào)都需要同步采樣;其次,需了解采集信號(hào)的帶寬,信號(hào)帶寬越大,對轉(zhuǎn)換器的轉(zhuǎn)換時(shí)間要求越高;最后,還應(yīng)明確采樣信號(hào)的幅值和精度要求,這關(guān)系到模擬調(diào)理電路和AD轉(zhuǎn)換器電路的設(shè)計(jì),幅值過大的信號(hào)可能需要電氣隔離,由隔離所帶來的精度損失應(yīng)考慮在內(nèi)。

在設(shè)計(jì)同步采樣電路時(shí),往往會(huì)用到同步采樣ADC,一般的同步采樣ADC有兩種結(jié)構(gòu),一種是自帶多個(gè)采樣保持器,內(nèi)置多路模擬開關(guān)和一個(gè)AD轉(zhuǎn)換內(nèi)核,通過采樣保持器進(jìn)行同步采集;另一種是內(nèi)置多個(gè)AD轉(zhuǎn)換內(nèi)核。實(shí)際設(shè)計(jì)時(shí)應(yīng)根據(jù)系統(tǒng)需求、通道個(gè)數(shù)、采樣周期等因素綜合確定系統(tǒng)方案。

2系統(tǒng)方案

在某同步控制系統(tǒng)中,共有42路模擬量需采集,其中8路模擬量需同步采集。這8路模擬量要求具有100 kHz的采樣頻率,其余的模擬量主要都是緩變模擬量,如溫度、壓力、指令等,要求采樣頻率約為1 kHz。

采用2片AD7656共用的方式構(gòu)成AD部分,無需同步采集的模擬量通過外置多路開關(guān)進(jìn)行切換,整個(gè)電路通過FPGA控制時(shí)序,DSP軟件設(shè)置好采樣模式、采樣周期、切換周期后,由邏輯管理AD外設(shè),處理器無需等待,只要定時(shí)去讀寄存器即可,系統(tǒng)架構(gòu)如圖1所示,這里AIN32~AIN42為11路同步采集模擬接口,實(shí)際使用了其中的8路。

3模擬電路設(shè)計(jì)

AD7656是一款逐次逼近型(SAR)ADC,此類ADC雖然不會(huì)在高速和高精度方面做到非常優(yōu)化,但其往往具有精度、速度、功耗和成本的綜合優(yōu)勢[3]。如果要使其發(fā)揮較好的模數(shù)轉(zhuǎn)換效果,應(yīng)特別注意電壓基準(zhǔn)源和模擬調(diào)理電路的設(shè)計(jì)。

3.1電壓基準(zhǔn)源

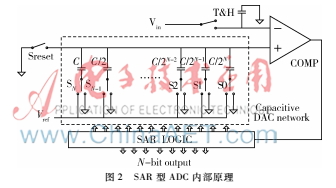

SAR型ADC的內(nèi)部原理簡圖如圖2所示,在采樣過程中輸入引腳AIN要對內(nèi)部采樣電容充電,而在轉(zhuǎn)化過程中,Vref基準(zhǔn)源引腳要對轉(zhuǎn)化電容網(wǎng)絡(luò)進(jìn)行充電。

SAR-ADC的采樣保持和量化過程,也就是對內(nèi)部電容的充電過程。但需要注意的是,在整個(gè)采樣量化周期中,SARADC對模擬輸入電路只抽取一次電荷,而要從基準(zhǔn)源REF中抽取N次電荷(N等于ADC的位數(shù)),而且抽取的周期更短(即一個(gè)轉(zhuǎn)化時(shí)鐘的周期)。基準(zhǔn)源引腳應(yīng)設(shè)計(jì)有儲(chǔ)能電容,在轉(zhuǎn)換的過程中,SAR-ADC不斷從基準(zhǔn)源處抽取電荷,隨著電荷的減少,電容電壓也在降低,由電容公式C=Q/V可知,電荷電壓變化關(guān)系如圖3所示。

在最壞的情況下,前端基準(zhǔn)源沒有及時(shí)給這個(gè)電容充電,這就使得轉(zhuǎn)換開始到結(jié)束基準(zhǔn)源的電壓已經(jīng)發(fā)生了ΔVref的變化。要使這一變化對ADC無影響,就要求ΔVref<1/2 LSB。

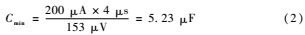

要滿足這一邊界條件,需要評估轉(zhuǎn)換過程中SARADC所需的最大電荷量,這取決于ADC基準(zhǔn)源的最大輸入電流Iref和輸入時(shí)間t。一般最壞情況都是在最高轉(zhuǎn)換速率時(shí)出現(xiàn)的。依據(jù)最大輸入電流和輸入時(shí)間,可得到轉(zhuǎn)換過程所需的總電荷量,再根據(jù)電容定義公式C=ΔQ/ΔV可推導(dǎo)出電壓基準(zhǔn)源處所需儲(chǔ)能電容的最小值為:

為留有一定裕量,進(jìn)行保守設(shè)計(jì),可將C取值為Cmin的2倍。

如果單獨(dú)的外置基準(zhǔn)源不足以及時(shí)補(bǔ)充AD轉(zhuǎn)換過程中消耗的電荷,則要考慮外加運(yùn)放構(gòu)成buffer。這個(gè)buffer不止用來增大基準(zhǔn)源的驅(qū)動(dòng)電流,其更重要的功能是快速給驅(qū)動(dòng)電容充電。因此要求這個(gè)運(yùn)放既具有足夠高的帶寬和響應(yīng)速率,也要具有足夠的驅(qū)動(dòng)能力。

在該數(shù)據(jù)采集系統(tǒng)中,設(shè)置AD7656的量程為±10 V,因此1 LSB=FSR/216=306 μV,1/2的LSB則為153 μV。AD7656的最高采樣速率為250 kb/s,所以t=4 μs。由于AD7656的手冊中并未給出其使用外部基準(zhǔn)源時(shí)的輸入電流指標(biāo),按照此類ADC一般的指標(biāo)估算,當(dāng)Iref=200 μA時(shí),可得出C的理論最小值為:

最終該容值選定為10 μF。由于板面體積空間的限制,在基準(zhǔn)源方面使用AD7656內(nèi)部集成的電壓基準(zhǔn)源,同時(shí)在基準(zhǔn)源去耦管腳處放置10 μF電容。

3.2模擬前端調(diào)理電路

模擬前端的調(diào)理電路基本原理如圖4所示,主要包含RC濾波和運(yùn)放。運(yùn)放相當(dāng)于是一個(gè)在信號(hào)源和AIN輸入之間的buffer。RC濾波則提供信號(hào)濾波,同時(shí)消除采樣抖動(dòng)。

應(yīng)該注意的是,RC電路用于濾除信號(hào)上的高頻噪聲,因此其濾波帶寬越低越有利于抑制高頻噪聲,但同時(shí)該一階慣性環(huán)節(jié)也會(huì)延長系統(tǒng)的建立時(shí)間,帶寬越低延遲越大,其時(shí)間常數(shù)如式(3)所示。

T=R×C(3)

為避免該環(huán)節(jié)過渡過程對后端AD轉(zhuǎn)換器的影響,應(yīng)保證AD采樣時(shí)刻該環(huán)節(jié)輸出誤差在1 LSB之內(nèi),這就與系統(tǒng)需達(dá)到的分辨位數(shù)有關(guān)。表1給出了系統(tǒng)需達(dá)到的位數(shù)與延遲T的關(guān)系。從表中可見要達(dá)到16位的精度,至少需要11倍T的時(shí)間才可以[4]。所以當(dāng)采樣周期較短時(shí)RC帶寬不能太低,要保證AD采樣時(shí)有足夠的建立時(shí)間。

ADC內(nèi)部進(jìn)行模擬信號(hào)采樣時(shí),會(huì)瞬間抽取模擬通道的電荷,產(chǎn)生采樣抖動(dòng),RC電路中的C可用于抑制這種抖動(dòng),這要求C具有一定的儲(chǔ)能特性,容量應(yīng)較大(nF級(jí))。同時(shí)采用無源RC時(shí)應(yīng)考慮R對信號(hào)的分壓作用,所以R應(yīng)盡量小,但如果R過小,則可能引起前端運(yùn)放的不穩(wěn)定。可見RC電路的設(shè)計(jì)是一個(gè)均衡考慮各種指標(biāo)的過程。最終按AD7656理論最高采樣周期4 μs來計(jì)算,R選為33 Ω,C選為10 nF。

4數(shù)字接口設(shè)計(jì)

為兼顧系統(tǒng)中的同步采集模擬量和其他模擬量對采樣頻率要求的差別,同時(shí)避免DSP直接操作AD轉(zhuǎn)換器和模擬多路開關(guān)的等待時(shí)間,在系統(tǒng)中通過FPGA對2片AD7656進(jìn)行接口時(shí)序控制,同時(shí)FPGA內(nèi)設(shè)計(jì)有控制寄存器和數(shù)據(jù)寄存器,DSP設(shè)置好采集模式后只需按時(shí)直接讀取數(shù)據(jù)寄存器即可。采集模式設(shè)計(jì)為單次采集和周期采集兩種。單次采集模式主要用于單路測試,周期采集模式用于應(yīng)用軟件的實(shí)時(shí)控制。FPGA邏輯主要包含兩個(gè)狀態(tài)機(jī):多路開關(guān)切換狀態(tài)機(jī)和同步采集狀態(tài)機(jī)。切換周期和同步采樣周期均通過軟件設(shè)置。FPGA邏輯的狀態(tài)轉(zhuǎn)換圖如圖5所示。

圖5左邊為多路開關(guān)狀態(tài)轉(zhuǎn)換圖,右邊為AD采樣狀態(tài)圖,由于各個(gè)信號(hào)源阻抗各不相同,且模擬多路選擇器具有一定的固有延遲,因此多路開關(guān)每切換一次的建立時(shí)間有所差別,經(jīng)測量,信號(hào)中最長建立時(shí)間約為40 μs,但需同步采集的模擬量又要求至少每10 μs采集一次。因此,在邏輯設(shè)計(jì)時(shí)第1路AD采集結(jié)果應(yīng)考慮多路開關(guān)的延遲狀態(tài),在采集過程中,建立時(shí)間不足40 μs的第1路AD采集數(shù)據(jù)將被丟棄,此時(shí)該路對應(yīng)的數(shù)據(jù)寄存器不更新數(shù)值,在FPGA中,通過信號(hào)量實(shí)現(xiàn)狀態(tài)的傳遞。在實(shí)際使用時(shí)將多路開關(guān)切換周期設(shè)置為100 μs,AD采樣周期設(shè)置為10 μs。

5實(shí)驗(yàn)測試結(jié)果分析

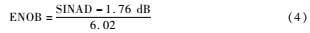

由于該AD轉(zhuǎn)換電路主要用于采集AC信號(hào),因此用戶最為關(guān)心的是該電路的動(dòng)態(tài)指標(biāo)。一般用于定量表示AD轉(zhuǎn)換動(dòng)態(tài)性能的常用指標(biāo)有6個(gè),分別是SINAD、SNR、ENOB、THD、THD+N、SFDR等[5]。其中SINAD(信納比)很好地反映了ADC的整體動(dòng)態(tài)性能,因?yàn)樗ㄋ袠?gòu)成噪聲和失真的成分,同時(shí)ENOB(有效位數(shù))也十分重要,它最直觀地反映了ADC的轉(zhuǎn)換質(zhì)量。

根據(jù)N位ADC的理論SNR計(jì)算公式(SNR=6.02 N+1.76 dB),將SINAD帶入換算可得到ENOB,如式(4)所示:

一般測試動(dòng)態(tài)指標(biāo)的方法是采用固定幅值的標(biāo)準(zhǔn)正弦波信號(hào)接入AD轉(zhuǎn)換電路,在不同激勵(lì)頻率下對采集到的電壓數(shù)據(jù)進(jìn)行FFT分析。需要注意的是,這種分析方法存在的缺點(diǎn)是容易造成頻譜泄漏,因此需要選擇合適的窗函數(shù)使信號(hào)截?cái)噤J角鈍化,可采用加hanning窗的方法[6]。

由于采樣頻率最高時(shí)SINAD指標(biāo)最差,因此進(jìn)行測試時(shí)采樣頻率按照系統(tǒng)使用的最大采樣頻率100 kHz進(jìn)行測試。

在常溫實(shí)驗(yàn)室環(huán)境下,使用HP公司出品的HP33120a型信號(hào)發(fā)生器,發(fā)出5 Vpp標(biāo)準(zhǔn)正弦波激勵(lì)被測通道。為降低FFT點(diǎn)數(shù)帶來的噪底,利用板上256 KB容量NVRAM的存儲(chǔ)功能,將采樣點(diǎn)數(shù)取為218個(gè)。采用ADI公司的Visual Analog分析工具對數(shù)據(jù)進(jìn)行分析。經(jīng)過10次測量,其平均SINAD為76.4 dB,ENOB為12.4。由此可見,由于同步開關(guān)噪聲、電源去耦等原因?qū)е翬NOB指標(biāo)較為一般。這一指標(biāo)在工程上屬可接受范圍,如進(jìn)一步改進(jìn)可考慮使用高精度、高穩(wěn)定度的外部基準(zhǔn)源代替ADC內(nèi)部基準(zhǔn)源,同時(shí)在電源去耦[7]、PCB走線等方面繼續(xù)優(yōu)化。

6結(jié)束語

針對多路模擬量的同步采集問題,本文研究了SAR型ADC的設(shè)計(jì)要點(diǎn)之后設(shè)計(jì)了一種使用FPGA控制AD7656的16位同步AD轉(zhuǎn)換系統(tǒng),該系統(tǒng)可實(shí)現(xiàn)模擬信號(hào)的實(shí)時(shí)同步采樣,F(xiàn)PGA的狀態(tài)機(jī)設(shè)計(jì)兼顧了同步采集量和非同步采集量的采集,可避免處理器過多的操作和等待外設(shè)。經(jīng)測試該系統(tǒng)具有較好的動(dòng)態(tài)指標(biāo),目前已在工程中應(yīng)用,達(dá)到了多路同步精密實(shí)時(shí)采樣的效果。

參考文獻(xiàn)

[1] 馬幸,韓珺禮,劉長順,等.高精度慣導(dǎo)系統(tǒng)信號(hào)處理平臺(tái)的設(shè)計(jì)與實(shí)現(xiàn)[J].電子測量技術(shù),2011,34(8):36-37.

[2] 陳新,WU C,HUTCHINGS W.功率因數(shù)校正的數(shù)字控制技術(shù)應(yīng)用研究[J].南京航空航天大學(xué)學(xué)報(bào),2007,39(2):164-169.

[3] 孫彤,李冬梅.逐次逼近A/D轉(zhuǎn)換器綜述[J].微電子學(xué),2007,37(4):523-525.

[4] WALSH A.Front end amplifier and RC filter design for a precision SAR analogtodigital converter[J].Analog Dialog,2012,46(12):2-3.

[5] KESTER W.The data conversion handbook[M]. Amsterdam:Elsevier,2005.

[6] 李海濤,阮林波,田耕,等.FFT方法在ADC有效位數(shù)測試中的應(yīng)用探討[J].電測與儀表,2013,50(10):15-17.

[7] 宋浩然,趙鐵龍.AD7656的原理及在繼電器保護(hù)產(chǎn)品中的應(yīng)用[J].電子技術(shù)應(yīng)用,2007,33(4):57-58.