據(jù)外媒報道,瑞薩電子推出了全新AI加速器,可高速且低功耗地執(zhí)行CNN(卷積神經(jīng)網(wǎng)絡(luò))處理,向下一代瑞薩嵌入式人工智能(e-AI)邁進(jìn),加速端點設(shè)備智能化。采用該加速器的測試芯片效率達(dá)到業(yè)界最高水平8.8 TOPS/W。瑞薩加速器基于計算存儲一體化(PIM)架構(gòu),即當(dāng)讀取存儲器數(shù)據(jù)時,在存儲器電路中執(zhí)行乘法和累加運算。

瑞薩開發(fā)人工智能加速器測試芯片

為構(gòu)建全新AI加速器,瑞薩推出了以下三種技術(shù)。一是可執(zhí)行大規(guī)模CNN計算的三進(jìn)制(-1,0,1)SRAM結(jié)構(gòu)PIM技術(shù)。二是與比較器配合使用的SRAM電路,可在低功耗下讀取存儲器數(shù)據(jù)。三是能夠防止在制造過程中因工藝變化而導(dǎo)致的計算錯誤。將以上技術(shù)結(jié)合,既能縮短深度學(xué)習(xí)處理中的存儲器訪問時間,又可降低乘法和累加運算所需的功率。因此,當(dāng)通過手寫字符識別測試(MNIST)進(jìn)行評估時,新加速器在保持99%以上準(zhǔn)確率的同時,達(dá)到了業(yè)界最高能效等級。

由于二進(jìn)制(0,1)SRAM結(jié)構(gòu)只能處理值為0或1的數(shù)據(jù),PIM架構(gòu)無法通過單比特計算獲得足夠的大規(guī)模CNN運算精度水平。此外,制造過程中的工藝變化導(dǎo)致這些運算的可靠性降低。針對這些問題,瑞薩現(xiàn)已開發(fā)出攻克這些問題的三大技術(shù),并將其作為實現(xiàn)未來革命性AI芯片的前沿技術(shù)應(yīng)用于下一代e-AI解決方案,例如對性能和功率效率有較高要求的可穿戴設(shè)備及機(jī)器人等。

技術(shù)一:可根據(jù)所需精度調(diào)整計算位數(shù)的三進(jìn)制(-1,0,1)SRAM結(jié)構(gòu)PIM技術(shù)

三進(jìn)制(-1,0,1)SRAM結(jié)構(gòu)PIM技術(shù)采用三元存儲器與簡單數(shù)字計算塊相組合,保證硬件數(shù)量增加的同時將計算誤差降至最低。同時,允許根據(jù)所需精度進(jìn)行位數(shù)切換(如1.5位(三進(jìn)制)和4位計算之間)。可針對不同用戶需求支持不同的精度及運算規(guī)模,用戶可優(yōu)化精度與功耗間的平衡。

技術(shù)二:結(jié)合比較器和復(fù)制單元的高精度/低功耗存儲器數(shù)據(jù)讀取電路

當(dāng)采用PIM架構(gòu)時,通過檢測SRAM結(jié)構(gòu)中的位線電流值以讀取存儲器數(shù)據(jù)。盡管使用A/D轉(zhuǎn)換器進(jìn)行高精度位線電流檢測是有效的,但這種方法功耗高且芯片面積較大。因此,瑞薩將比較器(1位感測放大器)與復(fù)制單元相結(jié)合,方便靈活控制電流,從而開發(fā)出高精度的存儲器數(shù)據(jù)讀取電路。此外,由于神經(jīng)網(wǎng)絡(luò)操作所激活節(jié)點(神經(jīng)元)數(shù)量非常少(約1%),通過關(guān)閉未激活節(jié)點(神經(jīng)元)讀取電路以實現(xiàn)更低的運行功率。

技術(shù)三:消除制造過程中因工藝變化導(dǎo)致計算誤差的規(guī)避技術(shù)

由于制造過程中的工藝變化,導(dǎo)致SRAM結(jié)構(gòu)中位線電流值產(chǎn)生誤差,從而造成存儲器讀取數(shù)據(jù)時出現(xiàn)錯誤。為解決這個問題,瑞薩在芯片內(nèi)部覆蓋了多個SRAM計算電路模塊,由制造工藝變化最小的模塊執(zhí)行計算任務(wù)。由于激活節(jié)點只是所有節(jié)點中的一小部分,因此激活節(jié)點被有選擇地分配給制造過程變化最小的SRAM計算電路模塊執(zhí)行計算。從而將計算誤差降至幾乎可忽略的水平。

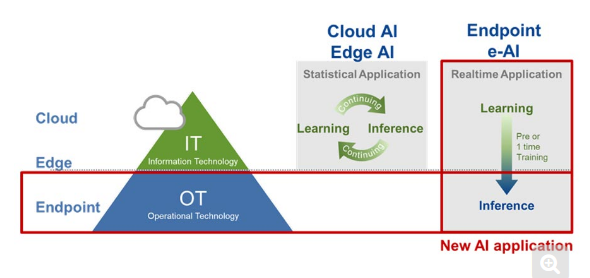

瑞薩電子的e-AI方案

自2015年引入嵌入式AI(e-AI)概念以來,瑞薩一直致力于多個e-AI解決方案的研發(fā)。自2015年引入嵌入式AI(e-AI)概念以來,瑞薩一直致力于多個e-AI解決方案的研發(fā)。憑借靈活可擴(kuò)展的嵌入式人工智能(e-AI)概念,瑞薩電子面向未來提供業(yè)界獨一無二的實時低功耗人工智能處理解決方案,以滿足端點嵌入式設(shè)備人工智能應(yīng)用的特定需求。

瑞薩根據(jù)e-AI的有效性和已實施的應(yīng)用程序定義了“類”,并根據(jù)以下四類開發(fā)出e-AI解決方案:

第1類:判斷信號波形數(shù)據(jù)的正確性或異常。

第2類(100GOPS/W級):通過實時圖像處理判斷正確性或異常。

第3類(1TOPS/W級):實時識別。

第4類(10TOPS/W級):在端點啟用增量學(xué)習(xí)。

瑞薩于2017年推出e-AI開發(fā)環(huán)境,并于2018年發(fā)布RZ/A2M微處理器,該微處理器集成瑞薩獨有DRP技術(shù),為第2類應(yīng)用提供解決方案。同時,為實現(xiàn)第3類應(yīng)用,瑞薩進(jìn)一步提高了DRP技術(shù)的計算性能。

現(xiàn)在,瑞薩正立足此項開發(fā)并推出新型尖端技術(shù)。全新加速器技術(shù)結(jié)合低功耗特性和改進(jìn)的計算性能,可能成為實現(xiàn)第4類應(yīng)用的關(guān)鍵技術(shù)之一。瑞薩致力于通過在物聯(lián)網(wǎng)邊緣及端點采用AI技術(shù)來增強(qiáng)智能,為實現(xiàn)智能社會做出貢獻(xiàn)。