在計(jì)算機(jī)芯片的世界中,許多參數(shù)都是 " 越大越好 "。比如更多的內(nèi)核、更高的 GHz 主頻、以及更大的浮點(diǎn)運(yùn)算能力。不同的是,在工藝制程上,整個(gè)行業(yè)都在極力向更微小的目標(biāo)前進(jìn)。從 10nm 到 7nm,直至 5nm 和更小的尺度。但在深入剖析原因之前,我們得先回顧下處理器的體系結(jié)構(gòu),以及工程師們是如何規(guī)劃和設(shè)計(jì)芯片的。

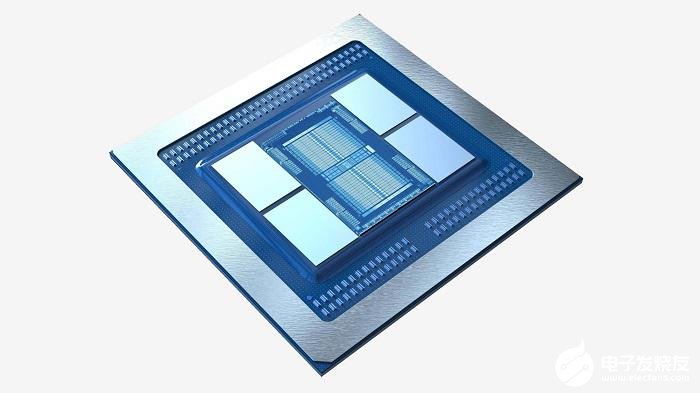

(題圖 來自:TechSpot)

現(xiàn)在前頭:本文主要講述計(jì)算機(jī)芯片是如何被物理組裝的,涉及制造的光刻部分則簡(jiǎn)略帶過。

在芯片行業(yè)里,特征尺寸與制程節(jié)點(diǎn)緊密相關(guān),詳細(xì)內(nèi)容可參考《如何設(shè)計(jì) CPU》的第三章節(jié)內(nèi)容。

芯片內(nèi)部的每個(gè)執(zhí)行單元,都可完成數(shù)學(xué)運(yùn)算和數(shù)據(jù)存儲(chǔ),且性能上相當(dāng)依賴于功效的工藝節(jié)點(diǎn)(特指同一制造商的每一次迭代)。

然而在營(yíng)銷實(shí)踐中,這個(gè)術(shù)語(yǔ)用起來還是相當(dāng)寬松的,取決于制造商愛用晶體管間的最小數(shù)值、或是平均數(shù)值。

在處理器世界中,任何改變都不會(huì)一蹴而就。更大的組件,意味著需要更長(zhǎng)時(shí)間才能變更其狀態(tài)、信號(hào)需要更長(zhǎng)的傳播時(shí)間、以及需要消耗更多的能量,更別提大芯片會(huì)占用更多的物理空間了。

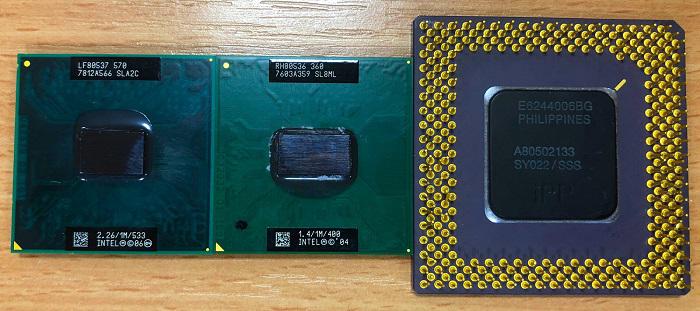

上圖中展示了英特爾的三款舊 CPU,最左邊的是 2006 年的賽揚(yáng)、中間的是 2004 年的奔騰移動(dòng)處理器、最右邊的則是 1995 年的古老崩騰處理器。

三款芯片的制程節(jié)點(diǎn)分別為 65、90、350 nm —— 24 年前的產(chǎn)品,其關(guān)鍵部件的體積是 13 年前產(chǎn)品的五倍。

與此同時(shí),較新的 CPU 內(nèi)部有大約 2.9 億個(gè)晶體管,而老崩騰只有它的百分之一(略超 300 萬(wàn)個(gè))。功耗方面,2006 款賽揚(yáng)處理器的 TDP 約 30W,老奔騰只有 12W 。

熱設(shè)計(jì)功耗的增加,主要是隨著電能在芯片中電路周圍的流動(dòng),能量因各種過程而損耗,且其中大部分以熱量的形式釋放。盡管 30W 數(shù)倍于 12W,但新 CPU 的晶體管更是舊芯片將近百倍。

正因如此,采用較小的工藝節(jié)點(diǎn),可使芯片更小、更快地切換晶體管、提升每秒的運(yùn)算量、并減少能耗(熱量)的散失。

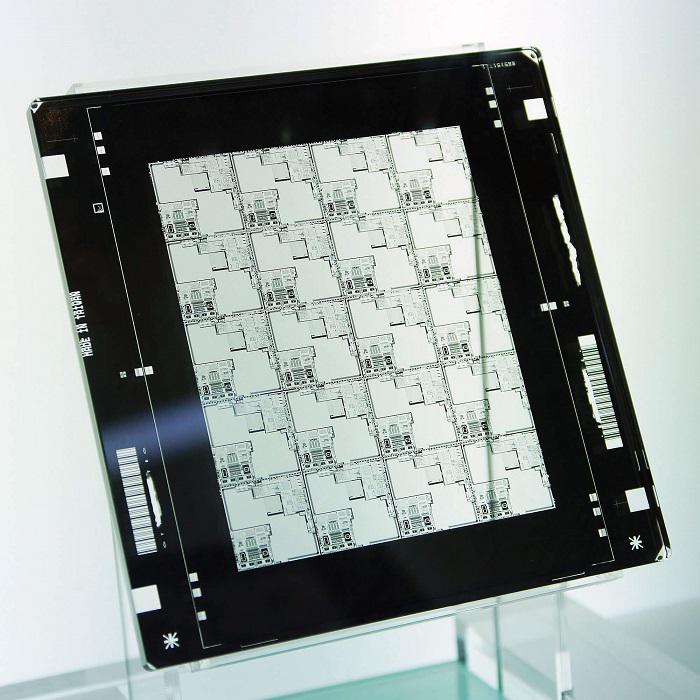

(圖自:Peellden,Wikimedia Commons)

那么,為何我們不 " 一步到位 ",直接讓所有芯片都使用最小的制程呢?說到這,就得提一下被稱作 " 光刻 " 的生產(chǎn)流程了。

光掩膜會(huì)遮擋某些區(qū)域的光線,被允許穿透的光線會(huì)集中在一個(gè)小點(diǎn)上,然后與芯片制造中使用的特殊層發(fā)生反應(yīng),以確定各個(gè)零件的位置。

你可想象給胳膊拍了一張 X 光照片,骨頭擋住了光線(起到了光罩的作用),而肌肉組織允許 X 射線的穿透,從而得出內(nèi)部結(jié)構(gòu)的圖像。而光刻工藝的迭代,與光的波長(zhǎng)有關(guān)。

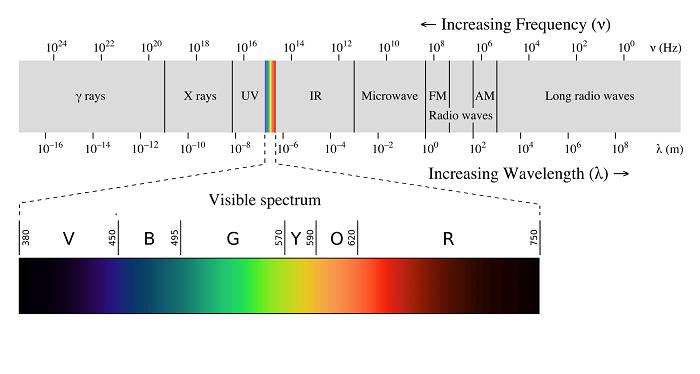

(圖自:Philip Ronan,Gringer)

可見光(380 ~ 750 nm)只是光譜的一部分,其它還有無(wú)線電波、微波、X 射線等。你可從上圖中見到光波的尺寸,大約在 10^-7 米左右(約 0.000004 英寸)。

言歸正傳,我們繼續(xù)聊聊芯片的制造工藝,比如舊賽揚(yáng)采用了 65nm 制程節(jié)點(diǎn)。那么,我們又該如何制造比光波還細(xì)小的零件呢?答案是采用紫外(EV)、甚至極紫外光刻(EUV)。

光譜圖中,UV 始于 380nm 左右,直到 10nm 左右。英特爾、臺(tái)積電、格羅方德等制造商,現(xiàn)在都已經(jīng)摸到了極紫外(190 nm 左右)。

新工藝不僅能夠?qū)⒔M件本身造得更小,且整體品質(zhì)也可能更好,從而將各個(gè)零件緊密封裝到一起,有助于縮小芯片的整體尺寸。

(制造缺陷特寫,圖自:Solid State Technology)

對(duì)于制程節(jié)點(diǎn)的規(guī)模,不同企業(yè)有著不同的宣稱。比如英特爾用 P1274 指代當(dāng)前的 10nm 工藝,而臺(tái)積電稱之為 10FF 。

在將格羅方德售出之后,AMD 現(xiàn)在靠的是臺(tái)積電代工,并且用上了 7nm 的量產(chǎn)工藝。需要指出的是,盡管一些最小特征的跨度僅為 6nm,但其它多數(shù)特征還是略大于此的。

為了讓普通人了解 6nm 到底有多小,就必須提到硅原子本身的直徑為 0.1nm 左右,而構(gòu)成處理器主體的大部分硅原子的間距僅在 0.5nm 。換言之,單個(gè)晶體管在各個(gè)方面都覆蓋了不到 10 個(gè)硅原子。

拋開令人難以置信的事實(shí),EUV 光刻技術(shù)還是引發(fā)了許多嚴(yán)重的工程和制造難題。英特爾一直努力使其 10nm 產(chǎn)能趕上 14nm 的水平,格羅方德更是在去年停止了 7nm 及以下制程的研發(fā)。

問題在于,隨著電磁波長(zhǎng)的越來越短,其攜帶的能量就越來越大,導(dǎo)致有更大的潛在可能性會(huì)損壞正在制造的芯片。此外,小規(guī)模制造對(duì)所用材料的污染和缺陷也高度敏感。

其它問題包括衍射極限和統(tǒng)計(jì)噪聲(EUV 波傳遞的能量在其中沉積到芯片層中的自然變化),導(dǎo)致制造商無(wú)法實(shí)現(xiàn) 100% 完美的芯片制造目標(biāo)。

還有一個(gè)問題是,在怪異的原子世界里,我們無(wú)法再假定電流和能量的傳遞,會(huì)遵循經(jīng)典的物理學(xué)系統(tǒng)規(guī)則。移動(dòng)電子的時(shí)候,遇到的各種棘手的問題也會(huì)更多。

就英特爾和臺(tái)積電而言,想要實(shí)現(xiàn)這一目標(biāo),將變得更加困難,因?yàn)榻^緣層的厚度還遠(yuǎn)遠(yuǎn)不夠。不過目前的生產(chǎn)問題,幾乎都集中在 EUV 光刻技術(shù)的固有缺陷上。

正因如此,我們要繼續(xù)等待多年,才能評(píng)判量子處理方案是否更具優(yōu)勢(shì)。此外出于商業(yè)的考慮,更小的制程可節(jié)省更多的成本。

假如英特爾用 28nm 工藝去制造 Haswell 系列 CPU(如 i7-4790K),其成本將會(huì)翻一番。但通過在單個(gè)晶圓上切割出更多的芯片,能夠在很大程度上抵消多出來的成本。