晶振,老生常談的話題。在往期文章中,小編對(duì)晶振從各大方面進(jìn)行過(guò)講解,如PCB板上配備哪些晶振。而在本文中,將同大家一同探討如何進(jìn)行PCB晶振設(shè)計(jì)。如果你對(duì)本文將要討論的晶振問(wèn)題存在一定興趣,不妨繼續(xù)往下閱讀哦。

我們常把晶振比喻為數(shù)字電路的心臟,這是因?yàn)椋瑪?shù)字電路的所有工作都離不開(kāi)時(shí)鐘信號(hào),晶振直接控制著整個(gè)系統(tǒng),若晶振不運(yùn)作那么整個(gè)系統(tǒng)也就癱瘓了,所以晶振是決定了數(shù)字電路開(kāi)始工作的先決條件。

我們常說(shuō)的晶振,是石英晶體振蕩器和石英晶體諧振器兩種,他們都是利用石英晶體的壓電效應(yīng)制作而成。在石英晶體的兩個(gè)電極上施加電場(chǎng)會(huì)使晶體產(chǎn)生機(jī)械變形,反之,如果在晶體兩側(cè)施加機(jī)械壓力就會(huì)在晶體上產(chǎn)生電場(chǎng)。并且,這兩種現(xiàn)象是可逆的。利用這種特性,在晶體的兩側(cè)施加交變電壓,晶片就會(huì)產(chǎn)生機(jī)械振動(dòng),同時(shí)產(chǎn)生交變電場(chǎng)。這種震動(dòng)和電場(chǎng)一般都很小,但是在某個(gè)特定頻率下,振幅會(huì)明顯加大,這就是壓電諧振,類(lèi)似于我們常見(jiàn)到的LC回路諧振。

作為數(shù)字電路中的心臟,晶振在智能產(chǎn)品中是如何發(fā)揮作用的呢?以智能家居如空調(diào)、窗簾、安防、監(jiān)控等產(chǎn)品來(lái)說(shuō),都需要無(wú)線傳輸模塊,它們通過(guò)藍(lán)牙、WIFI或ZIGBEE等協(xié)議,將模塊從一端發(fā)到另一端,或直接通過(guò)手機(jī)控制,而晶振就是無(wú)線模塊里的核心元件,影響著整系統(tǒng)的穩(wěn)定性,所以選擇好系統(tǒng)使用的晶振,決定了數(shù)字電路的成敗。

由于晶振在數(shù)字電路中的重要性,在使用和設(shè)計(jì)的時(shí)候我們需要小心處理:

1、晶振內(nèi)部存在石英晶體,受到外部撞擊或跌落時(shí)易造成石英晶體斷裂破損,進(jìn)而造成晶振不起振,所以在設(shè)計(jì)電路時(shí)要考慮晶振的可靠安裝,其位置盡量不要靠近板邊、設(shè)備外殼等。

2、在手工焊接或機(jī)器焊接時(shí),要注意焊接溫度。晶振對(duì)溫度比較敏感,焊接時(shí)溫度不能過(guò)高,并且加熱時(shí)間盡量短?

合理的晶振布局可以抑制系統(tǒng)輻射干擾

一、問(wèn)題描述

該產(chǎn)品為野外攝像機(jī),內(nèi)分核心控制板、sensor 板、攝像頭、SD 存儲(chǔ)卡和電池五部分組成,外殼為塑膠殼,小板僅有兩個(gè)接口:DC5V 外接電源接口和數(shù)據(jù)傳輸?shù)腢SB 接口。經(jīng)過(guò)輻射測(cè)試發(fā)現(xiàn)有33MHz 左右的諧波雜訊輻射問(wèn)題。

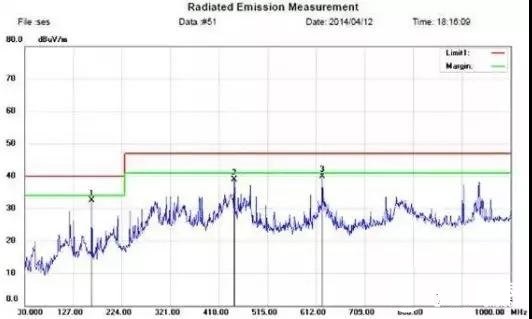

原始測(cè)試數(shù)據(jù)如下:

二、分析問(wèn)題

該產(chǎn)品外殼結(jié)構(gòu)塑膠外殼,是非屏蔽材料,整機(jī)測(cè)試只有電源線和USB 線引出殼體,難道干擾頻點(diǎn)是由電源線和USB 線輻射出來(lái)的嗎?故分別作了一下幾步測(cè)試:

( 1 ) 僅在電源線上加磁環(huán),測(cè)試結(jié)果:改善不明顯;

( 2 ) 僅在USB 線上加磁環(huán),測(cè)試結(jié)果:改善仍然不明顯;

( 3 ) 在USB 線和電源線都加磁環(huán),測(cè)試結(jié)果:改善較明顯,干擾頻點(diǎn)整體有所下降。

從上可得,干擾頻點(diǎn)是從兩個(gè)接口帶出來(lái)的,并非是電源接口或USB 接口的問(wèn)題,而是內(nèi)部干擾頻點(diǎn)耦合到這兩個(gè)接口所導(dǎo)致的,僅屏蔽某一接口不能解決問(wèn)題。

經(jīng)過(guò)近場(chǎng)量測(cè)發(fā)現(xiàn),干擾頻點(diǎn)來(lái)之于核心控制板的一個(gè)32.768KHz 的晶振,產(chǎn)生很強(qiáng)的空間輻射,使得周?chē)淖呔€和GND 都耦合了32.768KHz 諧波雜訊,再通過(guò)接口USB 線和電源線耦合輻射出來(lái)。而該晶振的問(wèn)題在于以下兩點(diǎn)問(wèn)題所導(dǎo)致的:

( 1 ) 晶振距離板邊太近,易導(dǎo)致晶振輻射雜訊。

( 2 ) 晶振下方有布信號(hào)線,,這易導(dǎo)致信號(hào)線耦合晶振的諧波雜訊。

( 3 ) 濾波器件放在晶振下方,且濾波電容與匹配電阻未按照信號(hào)流向排布,使得濾波器件的濾波效果變差。

三、解決對(duì)策

根據(jù)分析得出以下對(duì)策:

(1)晶體的濾波電容與匹配電阻靠近CPU 芯片優(yōu)先放置,遠(yuǎn)離板邊;

(2)切記不能在晶體擺放區(qū)域和下方投影區(qū)內(nèi)布地;

(3)晶體的濾波電容與匹配電阻按照信號(hào)流向排布,且靠近晶體擺放整齊緊湊;

(4)晶體靠近芯片處擺放,兩者間的走線盡量短而直。

可以參考如下圖布局方式:

經(jīng)整改后,樣機(jī)測(cè)試結(jié)果如下:

四、結(jié)論

現(xiàn)今很多系統(tǒng)晶振現(xiàn)今很多系統(tǒng)晶振時(shí)鐘頻率高,干擾諧波能量強(qiáng);干擾諧波除了從其輸入與輸出兩條走線傳導(dǎo)出來(lái),還會(huì)從空間輻射出來(lái),若布局不合理,容易造成很強(qiáng)的雜訊輻射問(wèn)題,而且很難通過(guò)其他方法來(lái)解決,因此在PCB 板布局時(shí)對(duì)晶振和CLK 信號(hào)線布局非常重要。

晶振的PCB設(shè)計(jì)注意事項(xiàng)

(1) 耦合電容應(yīng)盡量靠近晶振的電源引腳,位置擺放順序:按電源流入方向,依容值從大到小依次擺放,容值最小的電容最靠近電源引腳。

(2) 晶振的外殼必須接地,可以晶振的向外輻射,也可以屏蔽外來(lái)信號(hào)對(duì)晶振的干擾。

(3) 晶振下面不要布線,保證完全鋪地,同時(shí)在晶振的300mil范圍內(nèi)不要布線,這樣可以防止晶振干擾其他布線、器件和層的性能。

(4) 時(shí)鐘信號(hào)的走線應(yīng)盡量短,線寬大一些,在布線長(zhǎng)度和遠(yuǎn)離發(fā)熱源上尋找平衡。

(5) 晶振不要放置在PCB板的邊緣,在板卡設(shè)計(jì)時(shí)尤其注意該點(diǎn)。

以上便是此次小編帶來(lái)的“晶振”相關(guān)內(nèi)容,通過(guò)本文,希望大家對(duì)如何進(jìn)行PCB晶振設(shè)計(jì)具備一定的認(rèn)知。如果你喜歡本文,不妨持續(xù)關(guān)注我們網(wǎng)站哦,小編將于后期帶來(lái)更多精彩內(nèi)容。最后,十分感謝大家的閱讀,have a nice day!