SK海力士宣布,已經(jīng)與Xperi Corp旗下子公司Invensas簽訂新的專(zhuān)利與技術(shù)授權(quán)協(xié)議,獲得了后者DBI Ultra 2.5D/3D互連技術(shù)的授權(quán)。

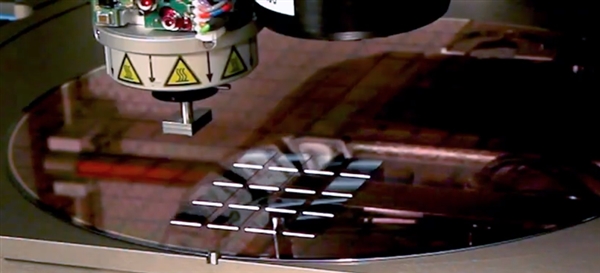

DBI Ultra是一種專(zhuān)利的裸片-晶圓(die-wafer)混合鍵合互連技術(shù),每平方毫米的面積里可以容納10萬(wàn)個(gè)到100萬(wàn)個(gè)互連開(kāi)孔,孔間距最小只有1微米,相比每平方毫米最多625個(gè)互連開(kāi)孔的傳統(tǒng)銅柱互連技術(shù),可大大提高傳輸帶寬。

DBIUltra使用化學(xué)鍵合來(lái)連接不同的互聯(lián)層,也不需要銅柱和底層填充,因此不會(huì)增加高度,從而大大降低整體堆疊高度,釋放空間,可將8層堆疊翻番到16層堆疊,獲得更大容量。

雖然它要使用新的工藝流程,但是良品率更高,也不需要高溫,而高溫正是影響良品率的關(guān)鍵因素。

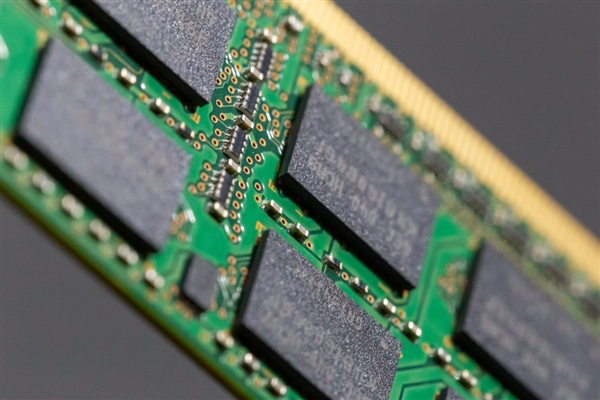

和其他下一代互連技術(shù)類(lèi)似,DBI Ultra也靈活支持2.5D、3D整合封裝,還能集成不同尺寸、不同工藝制程的IP模塊,因此不但可用來(lái)制造DRAM、3DS、HBM等內(nèi)存芯片,也可用于高集成度的CPU、GPU、ASIC、FPGA、SoC。

比如3D堆棧內(nèi)存方案,可以是4層的DRAM,可以是4/8/12/16層的HBM2/HBM3并在底部整合邏輯電路。

比如3D集成方案,可以上方是4-16層堆疊HBM、下方是CPU/GPU/FPGA/SoC等邏輯單元。

比如2.5D集成方案,可以在基板上一邊是4-16層堆疊HBM并通過(guò)邏輯電路接入基板,另一邊則是CPU/GPU/FPGA/SoC等邏輯單元直接以DBI Ultra互連的方式接入基板。

SK海力士還未透露會(huì)將DBI Ultra封裝技術(shù)用在哪里,但是DRAM、HBM顯然是最佳選擇。

作者:上方文Q