最近,臺積電終于公開承認了自己的3nm計劃。最終,半導(dǎo)體制造業(yè)這場決定未來制程走向的關(guān)鍵一役——3nm技術(shù)之戰(zhàn)還是來了。

3nm成為競爭關(guān)鍵點

三星的5nm工藝將作為其7nm LPP的改良面向市場推出,而3nm工藝才被三星視為是能夠超越臺積電的關(guān)鍵節(jié)點,在該節(jié)點中,三星將采用GAA MCFET(多橋通道FET)工藝。為什么三星會將賭注押在3nm節(jié)點上?

從三星和臺積電在過去三年的競爭中看,當年三星將其代工業(yè)務(wù)獨立出來之時,也正值先進工藝即將進入10nm工藝階段。彼時,兩者均推出了10nm工藝的產(chǎn)品。但當年三星10nm大客戶僅有高通,不敵臺積電。

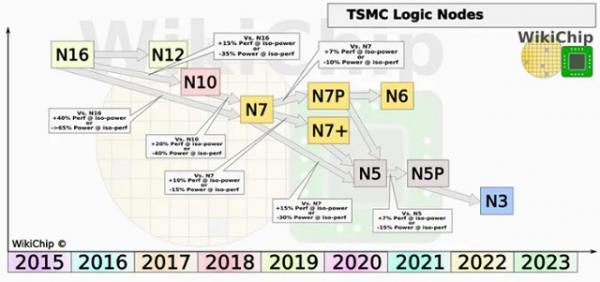

此后三星又在10nm上推出三種不同的改進工藝,以試圖搶奪更多的訂單。而臺積電則在推出10nm以后,轉(zhuǎn)向了更具優(yōu)勢的7nm工藝。7nm對于半導(dǎo)體制造工藝來說是非常重要的里程碑。2018年臺積電宣布其7nm開始量產(chǎn),三星則是選擇在7nm上使用EUV。同年,三星7nm EUV也宣布了量產(chǎn)計劃,但因其7nm EUV工藝技術(shù)不夠成熟,因而未能得到市場的認可。在此期間,華為海思、高通、英特爾和聯(lián)發(fā)科等企業(yè)紛紛投入到臺積電的懷抱。三星錯失了搶奪7nm訂單的最佳時期。

但根據(jù)市場情況來看,7nm在如今的市場中仍然保持著活力,三星7nm EUV技術(shù)也在去年得到了改善。于是,三星憑借低價搶奪了原在臺積電手中的英偉達的訂單。此外,三星還從臺積電手中搶走了IBM Power系列處理器的訂單。但這并不足以支撐三星在7nm上超越臺積電。所以,三星只能放眼下一代先進制程。

雙雄劍指3nm

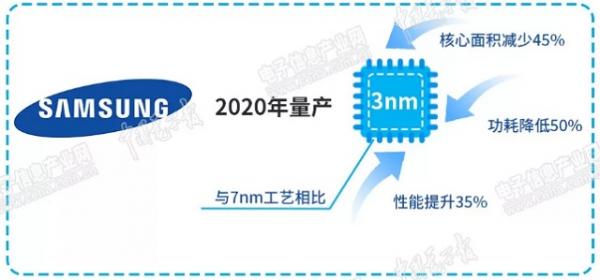

三星已成功研發(fā)出首個基于GAAFET的3nm制程,預(yù)計2022年開啟量產(chǎn)。與7nm工藝相比,3nm工藝可將核心面積減少45%,功耗降低50%,性能提升35%。

按照三星的研發(fā)路線圖,在6nm LPP之后,還有5nm LPE、4nm LPE兩個節(jié)點,隨后進入3nm節(jié)點,分為GAE(GAA Early)以及GAP(GAA Plus)兩代。去年5月,三星的3nm GAE設(shè)計套件0.1版本已經(jīng)就緒,以幫助客戶盡早啟動3nm設(shè)計。三星預(yù)計該技術(shù)將在下一代手機、網(wǎng)絡(luò)、自動駕駛、人工智能及物聯(lián)網(wǎng)等設(shè)備中使用。

以2022年量產(chǎn)為目標的臺積電,也在按計劃推進3nm研發(fā)。臺積電相關(guān)人士表示,臺積電在3nm節(jié)點技術(shù)開發(fā)進展順利,已經(jīng)與早期客戶進行接觸。臺積電投資6000億新臺幣(約合1380億元)的3nm寶山廠也于去年通過了用地申請,預(yù)計2020年動工,2022年量產(chǎn)。

臺積電在7nm節(jié)點取得了絕對優(yōu)勢,在5nm也進展順利,獲得了蘋果A14等訂單。但三星并沒有放松追趕的腳步,計劃到2030年前在半導(dǎo)體業(yè)務(wù)投資1160億美元(約合8000億元),以增強在非內(nèi)存芯片市場的實力。臺積電創(chuàng)始人張忠謀日前對媒體表示,臺積電與三星的戰(zhàn)爭還沒有結(jié)束,臺積電只是贏得了一兩場戰(zhàn)役,可整個戰(zhàn)爭還沒有贏,目前臺積電暫時占優(yōu)。

世界上最燒錢長跑:芯片制程進階之路

什么是芯片制程?制程用來描述芯片晶體管柵極寬度的大小,納米數(shù)字越小,說明晶體管密度越大,芯片性能就越高。

例如,臺積電7nm芯片的典型代表蘋果A13、高通驍龍865和華為麒麟990,每平方毫米約有1億個晶體管。隨后臺積電5nm、3nm芯片進一步將每平方毫米的晶體管數(shù)量進一步提升至1.713億個、2.5億個。

伴隨著制程的進化,5nm比7nm芯片性能提升15%,功耗降低30%;3nm又比5nm芯片性能提升10-15%,功耗降低25-30%。

由于各家對制程工藝的命名法則不同,相同納米制程下,并不能對各廠商的制程技術(shù)進展做直觀比較。比如英特爾10nm的晶體管密度與臺積電7nm、三星7nm的晶體管密度相當。

從制程最新進展來看,一邊是臺積電三星在5nm/3nm等先進制程上你追我趕,另一邊英特爾則韜光養(yǎng)晦循序漸進地走向7nm。

5nm方面,臺積電已經(jīng)拿到蘋果和華為的旗艦手機芯片訂單,下半年開啟量產(chǎn),有望在其2020年營收占比達10%。

三星在5nm制程則相對落后,目前正加速韓國華城5nm生產(chǎn)工廠V1的建設(shè),預(yù)計6月底前完成生產(chǎn)線建設(shè),今年年底前實現(xiàn)量產(chǎn)。

據(jù)外媒報道,三星與谷歌正合作開發(fā)采用三星5nm LPE工藝的定制Exynos芯片組,將搭載于谷歌的Pixel智能手機、Chrome OS設(shè)備甚至數(shù)據(jù)中心服務(wù)器中。

3nm方面,臺積電3nm制程預(yù)計2021年開始試生產(chǎn),并于2022年下半年開始量產(chǎn)。三星原計劃2021年大規(guī)模量產(chǎn)3nm工藝,但受當前疫情影響,不確定量產(chǎn)時間是否會推遲。

為什么挺進先進制程的玩家屈指可數(shù)呢?主要源于兩大門檻:資本和技術(shù)。

制程工藝的研發(fā)和生產(chǎn)成本逐代上漲。根據(jù)相關(guān)數(shù)據(jù),3nm芯片的設(shè)計費用約達5-15億美元,興建一條3nm產(chǎn)線的成本約為150-200億美元。

兩年前臺積電為3nm工藝計劃投資6000億新臺幣,折合近200億美元。單是從資金數(shù)目來看,很多中小型晶圓廠就玩不起。

更高的研發(fā)和生產(chǎn)成本,對應(yīng)的是更難的技術(shù)挑戰(zhàn)。

每當制程工藝逼近物理極限,晶體管結(jié)構(gòu)、光刻、沉積、刻蝕、檢測、封裝等技術(shù)的創(chuàng)新與協(xié)同配合,對芯片性能天花板的突破起到?jīng)Q定性作用。