正如之前外界傳聞的那樣,三星電子今天正式對外宣布,其已開始大規(guī)模生產(chǎn)基于3nm GAA(Gate-all-around,環(huán)繞柵極)制程工藝技術(shù)的芯片,這也使得三星搶先臺積電成為了全球首家量產(chǎn)3nm的晶圓代工企業(yè)。

三星量產(chǎn)3nm GAA制程,上海磐矽為首批客戶

2021年6月,三星就率先宣布其基于GAA技術(shù)的3nm制程成已成功流片(Tape Out)。隨后在2021年10月的“Samsung Foundry Forum 2021”活動上,三星宣布將在2022年上半年搶先臺積電量產(chǎn)3nm GAA制程工藝。

對于在3nm量產(chǎn)上超越臺積電,三星方面也是信心滿滿。三星Device Solution事業(yè)部技術(shù)負(fù)責(zé)人Jeong Eun-seung去年就曾表示,“三星2017年才成立晶圓代工事業(yè)部,但憑借公司在存儲制造方面的專長,超越臺積電指日可待。”他還舉例指出,三星曾領(lǐng)先臺積電開量產(chǎn)采用FinFET技術(shù)的14nm工藝。

雖然之前業(yè)界有很多關(guān)于三星3nm良率過低而導(dǎo)致量產(chǎn)遇阻的傳聞(今年年初有爆料稱,三星3nm GAA制程的良率僅10%~20%),但是三星仍然是在2022年上半年的最后一天(6月30日)正式宣布成功量產(chǎn)3nm GAA工藝,以兌現(xiàn)其之前的承諾。

根據(jù)三星官方公布的聲明顯示,基于其第一代的3nm GAA工藝的芯片與傳統(tǒng)的5nm工藝芯片相比,功耗降低了45%,性能提高了23%,面積可減少16%。

不過,以上公布的數(shù)據(jù)與三星之前透露的數(shù)據(jù)(性能將提升30%,能耗降可低50%,邏輯面積效率提升超過45%)有一定程度的縮水。

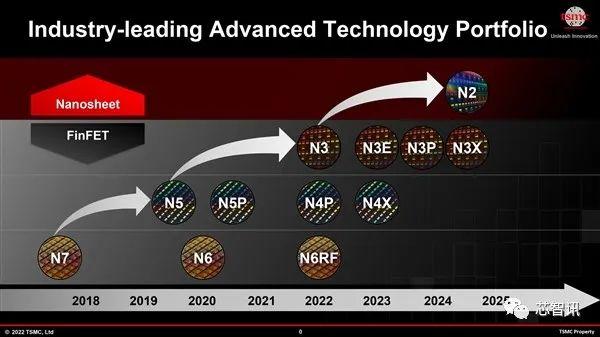

需要強(qiáng)調(diào)的是,除了搶先量產(chǎn)3nm制程工藝之外,三星也是全球第一個成功將GAA技術(shù)應(yīng)用到量產(chǎn)的3nm芯片當(dāng)中的晶圓代工廠商,雖然臺積電將會在今年下半年量產(chǎn)3nm工藝,但是其依然是基于FinFET晶體管架構(gòu),臺積電將會在2nm制程工藝上才會采用GAA技術(shù),量產(chǎn)時間則將會是在2025年。

三星晶圓代工業(yè)務(wù)主管Siyoung Choi表示:“公司將繼續(xù)在有競爭力的技術(shù)開發(fā)方面積極創(chuàng)新。”

中國礦機(jī)芯片廠商上海磐矽或為首批客戶

雖然三星并未公布其3nm GAA制程的客戶名單,但是根據(jù)爆料顯示,三星電子自身以及一家來自中國大陸的礦機(jī)芯片廠商——上海磐矽半導(dǎo)體技術(shù)有限公司將會是首批客戶。另外,三星的大客戶高通可能也下單生產(chǎn)3nm芯片,但會視情況投片。

資料顯示,上海磐矽半導(dǎo)體技術(shù)有限公司成立于2016年3月,注冊資本4500萬元人民幣,總部位于上海,是一家設(shè)計能力為28nm、16nm和10nm ASIC的高科技初創(chuàng)公司,專注于數(shù)字加密貨幣和Al應(yīng)用的ASIC設(shè)計。

三星聯(lián)合首席執(zhí)行官 Kyung Kye-hyun 今年早些時候曾表示,其代工業(yè)務(wù)將在中國尋找新客戶,預(yù)計中國市場將實(shí)現(xiàn)高速增長,因為從汽車制造商到家電產(chǎn)品制造商等公司都爭相確保產(chǎn)能以解決持續(xù)的全球芯片短缺問題。

是“真量產(chǎn)”,還是“真宣傳”?

雖然三星搶先臺積電量產(chǎn)了3nm GAA制程工藝,但是其為了兌現(xiàn)今年上半年量產(chǎn)承諾,在上半年的最后一天6月30日才宣布量產(chǎn),也讓一些分析人士認(rèn)為,其3nm GAA制程工藝量產(chǎn)是“趕鴨子上架”,宣傳意義大于實(shí)際意義。

比如臺灣工研院產(chǎn)科國際所研究總監(jiān)楊瑞臨就表示,GAA相關(guān)的蝕刻及量測問題尚待克服,材料、化學(xué)品等也需要提升,全球GAA生態(tài)系統(tǒng)還未完全到位,三星3nm GAA技術(shù)此時量產(chǎn)是“趕鴨子上架”。

ASML的新一代High-NA EUV光刻機(jī)預(yù)計最快也要2023年底才正式向客戶交付。臺積電和英特爾都選擇采用High-NA EUV光刻機(jī)來生產(chǎn)基于GGA架構(gòu)晶體管的2nm工藝。

楊瑞臨稱,雖然三星采用市場現(xiàn)有方案,可以做到3nm GAA技術(shù)量產(chǎn),但關(guān)鍵是成本會增加、交期會拉長、良率提升速度慢、品質(zhì)不見得好。在成本模型難以建立的情況下,三星難以對客戶報價,預(yù)料三星的3nm GAA技術(shù)應(yīng)僅自用,不會有真正的外部的客戶。

臺經(jīng)院產(chǎn)經(jīng)資料庫研究員暨總監(jiān)劉佩真也表示,三星仍未實(shí)際接獲3nm訂單,今天宣布量產(chǎn)3奈米制程,宣傳意義應(yīng)大于實(shí)質(zhì)意義。

而在此之前,在相同制程工藝節(jié)點(diǎn)上,三星的制程工藝在穩(wěn)定性、良率、發(fā)熱等方面的表現(xiàn)確實(shí)一直都要比臺積電差。此前高通就因為三星4nm代工的驍龍8的散熱問題,轉(zhuǎn)向了采用臺積電4nm代工驍龍8+。

不過,臺灣相關(guān)機(jī)構(gòu)的立場和觀點(diǎn)往往都會偏向本土的臺積電,看衰三星3nm GAA也屬正常。

同樣,韓國半導(dǎo)體分析師的觀點(diǎn)也往往是看好本土的三星。此前,韓國半導(dǎo)體分析師Greg Roh就表示三星3nm制程良率提升速度遠(yuǎn)高于市場預(yù)期,新增客戶速度相當(dāng)快。

GAA架構(gòu)晶體管到底有何優(yōu)勢?

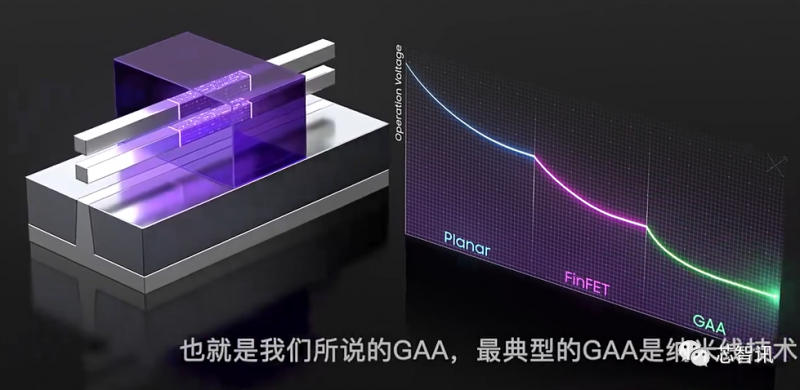

傳統(tǒng)的平面晶體管(Planar FET)通過降低電壓來節(jié)省功耗,然而,平面晶體管的短溝道效應(yīng)限制了電壓的繼續(xù)降低,而FinFET(鰭式場效應(yīng)晶體管)的出現(xiàn)使得電壓得以再次降低,但隨著工藝的繼續(xù)推進(jìn),F(xiàn)inFET已經(jīng)不足以滿足需求。于是,GAA(Gate-all-around,環(huán)繞柵極)技術(shù)應(yīng)運(yùn)而生。

如下圖,典型的GAA形式——GAAFET是(Gate-all-around FETs)采用的是納米線溝道設(shè)計,溝道整個外輪廓都被柵極完全包裹,代表柵極對溝道的控制性更好。相比之下,傳統(tǒng)的FinFET 溝道僅3 面被柵極包圍。GAAFET 架構(gòu)的晶體管提供比FinFET 更好的靜電特性,可滿足某些柵極寬度的需求。這主要表現(xiàn)在同等尺寸結(jié)構(gòu)下,GAA 的溝道控制能力強(qiáng)化,尺寸可以進(jìn)一步微縮。

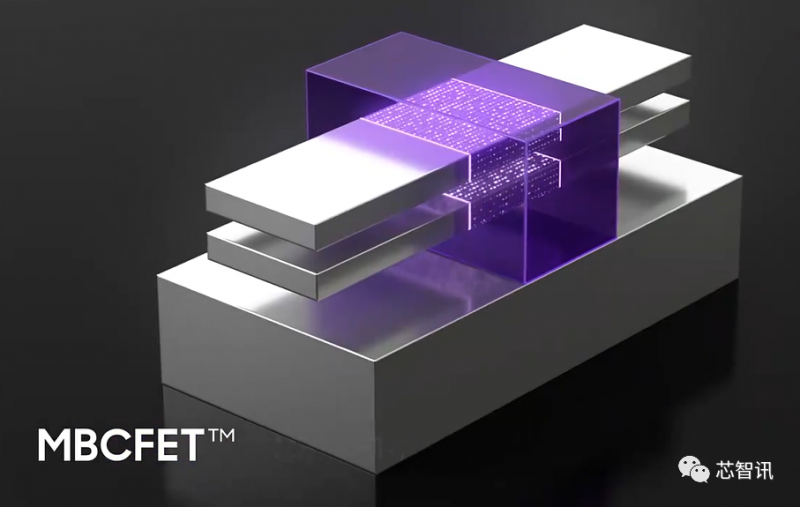

不過,三星認(rèn)為采用納米線溝道設(shè)計不僅復(fù)雜,且付出的成本可能也大于收益。因此,三星設(shè)計了一種全新的GAA形式——MBCFET(Multi-Bridge-Channel FET,多橋-通道場效應(yīng)管),采用多層堆疊的納米片來替代GAAFET中的納米線。這種納米片設(shè)計已被研究機(jī)構(gòu)IMEC當(dāng)作FinFET 架構(gòu)后續(xù)產(chǎn)品進(jìn)行大量研究,并由IBM 與三星和格羅方德合作發(fā)展。

三星表示,MBCFET可以在保留所有GAAFET優(yōu)點(diǎn)的情況下,最小化復(fù)雜度。同時,MBCFET的設(shè)計可以兼容之前的FinFET技術(shù),可以直接將為FinFET的設(shè)計遷移到MBCFET上,在不提升面積的情況下,提升性能。

此外,在制造環(huán)節(jié),此技術(shù)也具高度可制造性,因為其利用約90% FinFET 制造技術(shù)與設(shè)備,只需少量修改的光罩即可。

三星在去年就曾對外表示,MBCFET出色的柵極可控性,比三星原本FinFET 技術(shù)高出了31%,且納米片通道寬度可直接圖像化改變,設(shè)計更有靈活性。

三星的3nm GAA(MBCFET)工藝分為3GAAE (3nm Gate- AlI-Around Early)和3GAAP(3nm Gate- AlI-Around Plus)兩個階段。目前量產(chǎn)的正是3GAAE。

需要指出的是,三星基于GAA技術(shù)的3nm制程不同于臺積電FinFET架構(gòu)的3nm制程,所以三星要成功量產(chǎn)3nm GAA制程工藝,也需要新的設(shè)計和認(rèn)證工具。

據(jù)了解,三星3nm GAA制程工藝采用了新思科技的Fusion Design Platform平臺,來為其GAA 架構(gòu)的生產(chǎn)流程提供高度優(yōu)化參考方法。針對三星3nm GAA制程技術(shù)的物理設(shè)計套件(PDK)早在2019 年5 月就已發(fā)布,并在2020年通過了制程技術(shù)認(rèn)證。

新思科技數(shù)字設(shè)計部總經(jīng)理Shankar Krishnamoorthy當(dāng)時曾表示,GAA 晶體管結(jié)構(gòu)象征著制程技術(shù)進(jìn)步的關(guān)鍵轉(zhuǎn)換點(diǎn),對保持下一波超大規(guī)模創(chuàng)新所需的策略至關(guān)重要。新思科技與三星戰(zhàn)略合作支持提供一流技術(shù)和解決方案,確保發(fā)展趨勢延續(xù),以及為半導(dǎo)體產(chǎn)業(yè)提供機(jī)會。

臺積電與英特爾將在2nm引入GAA技術(shù)

一直以來,為了追趕臺積電,三星在先進(jìn)制程的推進(jìn)上一直都比較激進(jìn)。相比之下,作為業(yè)界龍頭的臺積電則一直比較穩(wěn)健。

臺積電在3nm制程工藝上并沒有選擇GAA架構(gòu)的晶體管,而是依然采用FinFET(鰭式場效應(yīng)晶體管),因為這將會為臺積電帶來更好的穩(wěn)定性,即可以復(fù)用之前成熟穩(wěn)定的技術(shù),同時成本可能也能夠得到更好的控制。并且給臺積電預(yù)留更多的對GAA晶體管架構(gòu)優(yōu)化的時間。

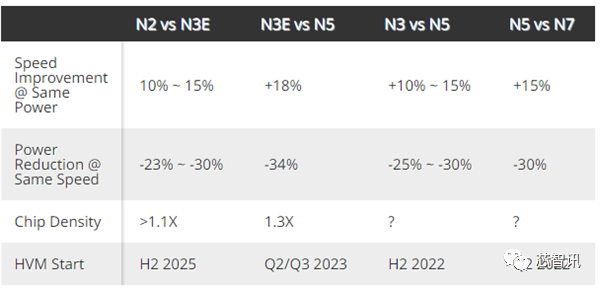

根據(jù)臺積電此前2022年臺積電技術(shù)論壇上公布的數(shù)據(jù)顯示,其即將量產(chǎn)的依然采用FinFET晶體管架構(gòu)的N3E(3nm的低成本版)制程工藝,相比前代的5mm制程工藝,性能將提升18%,功耗可降低34%,晶體管密度可提升30%。

從這個數(shù)據(jù)來看,三星3nm GAA制程工藝的與其前代5nm制程工藝相比所帶來的性能提升幅度和功耗降低的幅度都要比臺積電(3nm VS. 5nm)更高。

而且,需要指出的是,三星3nm GAA制程工藝的晶體管密度只比其前代5nm制程工藝的晶體管密度僅提升了16%(面積可減少16%)。而臺積電3nm的晶體管密度相比其5nm則是提升了30%。也就是說三星3nm GAA制程工藝依靠更少的晶體管密度的提升,達(dá)到了更好的性能提升和功耗降低的幅度,顯然,這與全新的GAA架構(gòu)所帶來的提升直接相關(guān)。

我們從臺積電公布的其2nm GAA制程工藝與其3nm的對比數(shù)據(jù),也同樣能夠看到GAA晶體管架構(gòu)所帶來的直接提升。

臺積電第一代采用納米片晶體管(Nanosheet,就是GAA)架構(gòu)的N2(即2nm)制程相較于其N3E(3nm的低成本版)工藝,在相同功耗下,性能將提升10~15%;而在相同性能下,臺積電2nm工藝的功耗將降低23~30%;晶體管密度僅提升了10%。

也就是說臺積電2nm GAA制程工藝僅用了10%的晶體管密度的提升,就帶來了最多15%的性能提升、最多30%的功耗的降低。已經(jīng)基本達(dá)到了臺積電3nm相比5nm的代際提升的幅度,而且后者還是在晶體管密度提升了30%的情況下實(shí)現(xiàn)的。這也再度反應(yīng)了GAA晶體管架構(gòu)所能夠帶來的提升。

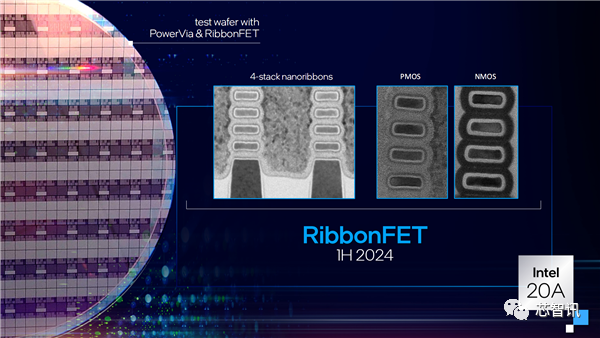

與臺積電一樣,英特爾也選擇了在Intel 3(相當(dāng)于臺積電3nm制程工藝)繼續(xù)采用FinFET技術(shù),預(yù)計在2023年量產(chǎn),相比Intel 4可帶來每瓦性能上約18%的提升。直到Intel 20A(相當(dāng)于臺積電2nm制程工藝)英特爾才會使用RibbonFET(即GAA)技術(shù),預(yù)計將領(lǐng)先臺積電在2024年上半年量產(chǎn),但是具體的細(xì)節(jié)參數(shù)并未公布。

在GAA專利技術(shù)布局方面,之前的一份數(shù)據(jù)顯示,2011~2020年期間,全球有31.4%的GAA專利來自臺積電,20.6%來自三星。

先進(jìn)制程晶圓代工市場的競爭正在加劇

一直以來,三星都希望能夠在晶圓代工業(yè)務(wù)上超越臺積電,其中對于先進(jìn)制程的爭奪更是成為了雙方的焦點(diǎn)。搶先量產(chǎn)更為先進(jìn)的半導(dǎo)體制程工藝,不僅能夠體現(xiàn)自身的技術(shù)實(shí)力,同時也意味著三星能夠為客戶更快的生產(chǎn)更先進(jìn)的芯片,幫助客戶更快的在市場競爭當(dāng)中占據(jù)有利的地位。這也使得三星能夠憑借搶先量產(chǎn)更先進(jìn)的制程工藝搶到更多的客戶。

比如在2014年底,三星就搶先臺積電量產(chǎn)了14nm工藝,而臺積電16nm在2015年年中才開始量產(chǎn)。制程工藝上的領(lǐng)先,也使得三星在當(dāng)時順利拿下了蘋果iPhone 6S系列所采用的蘋果A9處理器的超過半數(shù)訂單。

但是,隨后不論是從用戶的體驗,還是專業(yè)的機(jī)構(gòu)的測試都顯示,基于三星14nm工藝A9處理器的iPhone 6S在體驗與續(xù)航表現(xiàn)上都要弱于臺積電16nm工藝A處理器的iPhone 6S。

而且在此之后,臺積電在10nm-7nm-5nm的量產(chǎn)上均持續(xù)領(lǐng)先于三星,這也使得蘋果從后續(xù)的A10處理器開始全部都交由臺積電獨(dú)家代工。

資料顯示,蘋果近年來一直是臺積電的第一大客戶,特別是隨著蘋果M系列處理器成功,給臺積電帶來的營收也進(jìn)一步大幅增長。在臺積電2021年總營收當(dāng)中,來自蘋果的營收占比或?qū)⑦_(dá)到近26%。

根據(jù)TrendForce的數(shù)據(jù)顯示,在今年一季度的晶圓代工市場,臺積電的市場份額高達(dá)53.6%,而排名第二的三星的市場份額僅有16.3%,份額差距巨大。

因此,對于三星來說,只在最先進(jìn)的制程工藝技術(shù)上領(lǐng)先臺積電,才有機(jī)會獲得蘋果這樣的頭部客戶的訂單,才有機(jī)會在晶圓代工市場獲得更高的市場份額,從而實(shí)現(xiàn)超越臺積電的目標(biāo)。

而為了實(shí)現(xiàn)對臺積電的超越,三星在2017年成立了獨(dú)立的晶圓代工事業(yè)部,對于晶圓代工業(yè)務(wù)的重視程度也提升到了一個新高度,同時也開始持續(xù)加大投入。根據(jù)此前的資料顯示,三星計劃在2030年之前投資133萬億韓元(約合1160億美元),以期成為全球最大的半導(dǎo)體代工企業(yè)。

與此同時,臺積電去年也宣布在未來三年累計資本開支提升到1000億美元。

在三星積極追趕臺積電的同時,市場也迎來了新的“攪局者”——英特爾。

去年3月,英特爾新任CEO基辛格宣布了IDM 2.0戰(zhàn)略,其中關(guān)鍵的一項舉措就是重啟晶圓代工業(yè)務(wù),英特爾還陸續(xù)宣布了龐大的產(chǎn)能擴(kuò)張計劃,以及激進(jìn)的制程工藝路線圖。

首先,在產(chǎn)能方面,自去年以來,英特爾陸續(xù)宣布投資200億美元在美國亞利桑那州建造兩座先進(jìn)制程晶圓廠、200億美元在美國俄亥俄州建造兩座先進(jìn)制程晶圓廠、30億美元擴(kuò)建美國俄勒岡州D1X 晶圓廠、未來10年在歐洲投資800億歐元(包括投資170億歐元在德國馬德堡建兩座先進(jìn)制程晶圓廠;投資約120億歐元,將愛爾蘭萊克斯利普的晶圓廠的制造空間擴(kuò)大一倍)等。

今年2月15日,英特爾還宣布以每股53美元的現(xiàn)金收購全球第十大晶圓代工廠——高塔半導(dǎo)體,交易總價值約為54億美元。英特爾稱,此收購大力推進(jìn)了英特爾的IDM2.0戰(zhàn)略,進(jìn)一步擴(kuò)大英特爾的制造產(chǎn)能、全球布局及技術(shù)組合,以滿足前所未有的行業(yè)需求。

在先進(jìn)制程工藝進(jìn)展方面,去年7月,英特爾就宣布將在2024年上半年量產(chǎn)Intel 20A工藝,并于2025年量產(chǎn)Intel 18A工藝。

隨后在今年3月,摩根士丹利投資者大會上,英特爾CEO基辛格回應(yīng)稱,對英特爾IDM 2.0 戰(zhàn)略計劃非常有信心,且目前英特爾先進(jìn)制程進(jìn)展皆超過預(yù)期。基辛格強(qiáng)調(diào),Intel 7 制程進(jìn)入量產(chǎn)并開始增加產(chǎn)能。接下來四代先進(jìn)制程是由兩個團(tuán)隊同時進(jìn)行研發(fā),一個是負(fù)責(zé)Intel 4 及改良版Intel 3 制程,另一個團(tuán)隊負(fù)責(zé)Intel 20A 及18A 制程。根據(jù)規(guī)劃Intel 20A依舊會在2024年上半年量產(chǎn),而Intel 18A 制程將提前半年在2024年下半年量產(chǎn)。

由于臺積電和三星的2nm計劃的量產(chǎn)時間都是在2025年,因此,英特爾有望在2024年在先進(jìn)制程工藝超越臺積電和三星。

值得注意的是,去年英特爾就已宣布2024年上半年量產(chǎn)的Intel 20A工藝,將與高通達(dá)成合作。今年3月,基辛格也對外表示,未來最先進(jìn)的工藝都會提供晶圓代工服務(wù),其中Intel 3、Intel 18A 制程都已經(jīng)找到客戶,但具體名單未透露。

根據(jù)英特爾對投資人公布的統(tǒng)計數(shù)據(jù)顯示,今年一季度英特爾的晶圓代工業(yè)務(wù)營收年增175%,是旗下主要業(yè)務(wù)中,成長幅度最驚人的業(yè)務(wù),主要來自思科、亞馬遜等30多家客戶的訂單。

顯然,英特爾入局晶圓代工市場,將為本就競爭激烈的先進(jìn)制程晶圓代工市場帶來了新的競爭,臺積電、三星也將面臨新的挑戰(zhàn)。

作者: 芯智訊浪客劍