多級(jí)存儲(chǔ)器與模擬內(nèi)存內(nèi)計(jì)算完美融合,人工智能邊緣處理難題迎刃而解

2020-07-13

作者:Vipin Tiwari ,Microchip嵌入式存儲(chǔ)器產(chǎn)品開發(fā)總監(jiān)

來(lái)源:Microchip

機(jī)器學(xué)習(xí)和深度學(xué)習(xí)已成為我們生活中不可或缺的部分。利用自然語(yǔ)言處理(NLP)、圖像分類和物體檢測(cè)實(shí)現(xiàn)的人工智能(AI)應(yīng)用已深度嵌入到我們使用的眾多設(shè)備中。大多數(shù)AI應(yīng)用通過(guò)云引擎即可出色地滿足其用途,例如在Gmail中回復(fù)電子郵件時(shí)可以獲得詞匯預(yù)測(cè)。

雖然我們可以享受到這些AI應(yīng)用帶來(lái)的益處,但這種方法導(dǎo)致隱私、功耗、延時(shí)和成本等諸多因素面臨挑戰(zhàn)。如果有一個(gè)能夠在數(shù)據(jù)來(lái)源處執(zhí)行部分或全部計(jì)算(推斷)的本地處理引擎,那么這些問(wèn)題即可迎刃而解。傳統(tǒng)數(shù)字神經(jīng)網(wǎng)絡(luò)的存儲(chǔ)器功耗存在瓶頸,難以實(shí)現(xiàn)這一目標(biāo)。為了解決這一問(wèn)題,可以將多級(jí)存儲(chǔ)器與模擬內(nèi)存內(nèi)計(jì)算方法結(jié)合使用,使處理引擎滿足更低的毫瓦級(jí)(mW)到微瓦級(jí)(μW)功率要求,從而在網(wǎng)絡(luò)邊緣執(zhí)行AI推斷。

通過(guò)云引擎提供服務(wù)的

AI應(yīng)用面臨的挑戰(zhàn)

如果通過(guò)云引擎為AI應(yīng)用提供服務(wù),用戶必須將一些數(shù)據(jù)以主動(dòng)或被動(dòng)方式上傳到云,計(jì)算引擎在云中處理數(shù)據(jù)并提供預(yù)測(cè),然后將預(yù)測(cè)結(jié)果發(fā)送給下游用戶使用。下面概述了這一過(guò)程面臨的挑戰(zhàn):

圖1:從邊緣到云的數(shù)據(jù)傳輸

1. 隱私問(wèn)題:對(duì)于始終在線始終感知的設(shè)備,個(gè)人數(shù)據(jù)和/或機(jī)密信息在上傳期間或在數(shù)據(jù)中心的保存期限內(nèi)存在遭受濫用的風(fēng)險(xiǎn)。

2. 不必要的功耗:如果每個(gè)數(shù)據(jù)位都傳輸?shù)皆疲瑒t硬件、無(wú)線電、傳輸裝置以及云中不必要的計(jì)算都會(huì)消耗電能。

3. 小批量推斷的延時(shí):如果數(shù)據(jù)來(lái)源于邊緣,有時(shí)至少需要一秒才能收到云系統(tǒng)的響應(yīng)。當(dāng)延時(shí)超過(guò)100毫秒時(shí),人們便有明顯感知,造成反響不佳的用戶體驗(yàn)。

4. 數(shù)據(jù)經(jīng)濟(jì)需要?jiǎng)?chuàng)造價(jià)值:傳感器隨處可見(jiàn),價(jià)格低廉;但它們會(huì)產(chǎn)生大量數(shù)據(jù)。將每個(gè)數(shù)據(jù)位都上傳到云進(jìn)行處理并不劃算。

要使用本地處理引擎解決這些挑戰(zhàn),必須首先針對(duì)目標(biāo)用例利用指定數(shù)據(jù)集對(duì)執(zhí)行推斷運(yùn)算的神經(jīng)網(wǎng)絡(luò)進(jìn)行訓(xùn)練。這通常需要高性能計(jì)算(和存儲(chǔ)器)資源以及浮點(diǎn)算數(shù)運(yùn)算。因此,機(jī)器學(xué)習(xí)解決方案的訓(xùn)練部分仍需在公共或私有云(或本地GPU、CPU和FPGA Farm)上實(shí)現(xiàn),同時(shí)結(jié)合數(shù)據(jù)集來(lái)生成最佳神經(jīng)網(wǎng)絡(luò)模型。神經(jīng)網(wǎng)絡(luò)模型的推斷運(yùn)算不需要反向傳播,因此在該模型準(zhǔn)備就緒之后,可利用小型計(jì)算引擎針對(duì)本地硬件進(jìn)行深度優(yōu)化。推斷引擎通常需要大量乘-累加(MAC)引擎,隨后是激活層(例如修正線性單元(ReLU)、Sigmoid函數(shù)或雙曲正切函數(shù),具體取決于神經(jīng)網(wǎng)絡(luò)模型復(fù)雜度)以及各層之間的池化層。

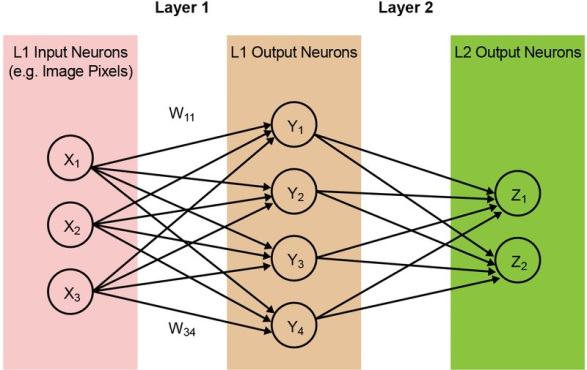

大多數(shù)神經(jīng)網(wǎng)絡(luò)模型需要大量MAC運(yùn)算。例如,即使是相對(duì)較小的“1.0 MobileNet-224”模型,也有420萬(wàn)個(gè)參數(shù)(權(quán)重),執(zhí)行一次推斷需要多達(dá)5.69億次的MAC運(yùn)算。此類模型中的大多數(shù)都由MAC運(yùn)算主導(dǎo),因此這里的重點(diǎn)是機(jī)器學(xué)習(xí)計(jì)算的運(yùn)算部分,同時(shí)還要尋找機(jī)會(huì)來(lái)創(chuàng)建更好的解決方案。下面的圖2展示了一個(gè)簡(jiǎn)單的完全連接型兩層網(wǎng)絡(luò)。輸入神經(jīng)元(數(shù)據(jù))通過(guò)第一層權(quán)重處理。第一層的輸出神經(jīng)元通過(guò)第二層權(quán)重處理,并提供預(yù)測(cè)(例如,模型能否在指定圖像中找到貓臉)。這些神經(jīng)網(wǎng)絡(luò)模型使用“點(diǎn)積”運(yùn)算計(jì)算每層中的每個(gè)神經(jīng)元,如下面的公式所示:

(為簡(jiǎn)單起見(jiàn),公式中省略了“偏差”項(xiàng))。

(為簡(jiǎn)單起見(jiàn),公式中省略了“偏差”項(xiàng))。

圖2:完全連接的兩層神經(jīng)網(wǎng)絡(luò)

在數(shù)字神經(jīng)網(wǎng)絡(luò)中,權(quán)重和輸入數(shù)據(jù)存儲(chǔ)在DRAM/SRAM中。權(quán)重和輸入數(shù)據(jù)需要移至某個(gè)MAC引擎旁以進(jìn)行推斷。根據(jù)下圖,采用這種方法后,大部分功耗都來(lái)源于獲取模型參數(shù)以及將數(shù)據(jù)輸入到實(shí)際發(fā)生MAC運(yùn)算的ALU。從能量角度來(lái)看,使用數(shù)字邏輯門的典型MAC運(yùn)算消耗約250 fJ的能量,但在數(shù)據(jù)傳輸期間消耗的能量超過(guò)計(jì)算本身兩個(gè)數(shù)量級(jí),達(dá)到50皮焦(pJ)到100 pJ的范圍。公平地說(shuō),很多設(shè)計(jì)技巧可以最大程度減少存儲(chǔ)器到ALU的數(shù)據(jù)傳輸,但整個(gè)數(shù)字方案仍受馮·諾依曼架構(gòu)的限制。這就意味著,有大量的機(jī)會(huì)可以減少功率浪費(fèi)。如果執(zhí)行MAC運(yùn)算的能耗可以從約100 pJ減少到若干分之幾pJ,將會(huì)怎樣呢?

消除存儲(chǔ)器瓶頸

同時(shí)降低功耗

如果存儲(chǔ)器本身可用來(lái)消除之前的存儲(chǔ)器瓶頸,則在邊緣執(zhí)行推斷相關(guān)的運(yùn)算就成為可行方案。使用內(nèi)存內(nèi)計(jì)算方法可以最大程度地減少必須移動(dòng)的數(shù)據(jù)量。這反過(guò)來(lái)也會(huì)消除數(shù)據(jù)傳輸期間浪費(fèi)的能源。閃存單元運(yùn)行時(shí)產(chǎn)生的有功功率消耗較低,在待機(jī)模式下幾乎不消耗能量,因此可以進(jìn)一步降低能耗。

圖3:機(jī)器學(xué)習(xí)計(jì)算中的存儲(chǔ)器瓶頸

來(lái)源:Y.-H. Chen、J. Emer和V. Sze于2016國(guó)際計(jì)算機(jī)體系結(jié)構(gòu)研討會(huì)發(fā)表的“Eyeriss: A Spatial Architecture for Energy-Efficient Dataflow for Convolutional Neural Networks”。

該方法的一個(gè)示例是Microchip子公司Silicon Storage Technology(SST)的memBrain?技術(shù)。該解決方案依托于SST的SuperFlash?存儲(chǔ)器技術(shù),這項(xiàng)技術(shù)已成為適用于單片機(jī)和智能卡應(yīng)用的多級(jí)存儲(chǔ)器的公認(rèn)標(biāo)準(zhǔn)。這種解決方案內(nèi)置一個(gè)內(nèi)存內(nèi)計(jì)算架構(gòu),允許在存儲(chǔ)權(quán)重的位置完成計(jì)算。權(quán)重沒(méi)有數(shù)據(jù)移動(dòng),只有輸入數(shù)據(jù)需要從輸入傳感器(例如攝像頭和麥克風(fēng))移動(dòng)到存儲(chǔ)器陣列中,因此消除了MAC計(jì)算中的存儲(chǔ)器瓶頸。

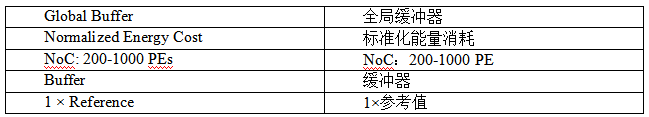

這種存儲(chǔ)器概念基于兩大基本原理:(a)晶體管的模擬電流響應(yīng)基于其閾值電壓(Vt)和輸入數(shù)據(jù),(b)基爾霍夫電流定律,即在某個(gè)點(diǎn)交匯的多個(gè)導(dǎo)體網(wǎng)絡(luò)中,電流的代數(shù)和為零。了解這種多級(jí)存儲(chǔ)器架構(gòu)中的基本非易失性存儲(chǔ)器(NVM)位單元也十分重要。下圖(圖4)是兩個(gè)ESF3(第3代嵌入式SuperFlash)位單元,帶有共用的擦除門(EG)和源線(SL)。每個(gè)位單元有五個(gè)終端:控制門(CG)、工作線(WL)、擦除門(EG)、源線(SL)和位線(BL)。通過(guò)向EG施加高電壓執(zhí)行位單元的擦除操作。通過(guò)向WL、CG、BL和SL施加高/低電壓偏置信號(hào)執(zhí)行編程操作。通過(guò)向WL、CG、BL和SL施加低電壓偏置信號(hào)執(zhí)行讀操作。

圖4:SuperFlash ESF3單元

利用這種存儲(chǔ)器架構(gòu),用戶可以通過(guò)微調(diào)編程操作,以不同Vt電壓對(duì)存儲(chǔ)器位單元進(jìn)行編程。存儲(chǔ)器技術(shù)利用智能算法調(diào)整存儲(chǔ)器單元的浮柵(FG)電壓,以從輸入電壓獲得特定的電流響應(yīng)。根據(jù)最終應(yīng)用的要求,可以在線性區(qū)域或閾下區(qū)域?qū)卧M(jìn)行編程。

圖5說(shuō)明了在存儲(chǔ)器單元中存儲(chǔ)多個(gè)電壓的功能。例如,我們要在一個(gè)存儲(chǔ)器單元中存儲(chǔ)一個(gè)2位整數(shù)值。對(duì)于這種情況,我們需要使用4個(gè)2位整數(shù)值(00、01、10、11)中的一個(gè)對(duì)存儲(chǔ)器陣列中的每個(gè)單元進(jìn)行編程,此時(shí),我們需要使用四個(gè)具有足夠間隔的可能Vt值之一對(duì)每個(gè)單元進(jìn)行編程。下面的四條IV曲線分別對(duì)應(yīng)于四種可能的狀態(tài),單元的電流響應(yīng)取決于向CG施加的電壓。

圖5:ESF3單元中的編程Vt電壓

受訓(xùn)模型的權(quán)重通過(guò)編程設(shè)定為存儲(chǔ)器單元的浮柵Vt。因此,受訓(xùn)模型每一層(例如完全連接的層)的所有權(quán)重都可以在類似矩陣的存儲(chǔ)器陣列上編程,如圖6所示。對(duì)于推斷運(yùn)算,數(shù)字輸入(例如來(lái)自數(shù)字麥克風(fēng))首先利用數(shù)模轉(zhuǎn)換器(DAC)轉(zhuǎn)換為模擬信號(hào),然后應(yīng)用到存儲(chǔ)器陣列。隨后該陣列對(duì)指定輸入向量并行執(zhí)行數(shù)千次MAC運(yùn)算,產(chǎn)生的輸出隨即進(jìn)入相應(yīng)神經(jīng)元的激活階段,隨后利用模數(shù)轉(zhuǎn)換器(ADC)將輸出轉(zhuǎn)換回?cái)?shù)字信號(hào)。然后,這些數(shù)字信號(hào)在進(jìn)入下一層之前進(jìn)行池化處理。

圖6:用于推斷的權(quán)重矩陣存儲(chǔ)器陣列

這類多級(jí)存儲(chǔ)器架構(gòu)模塊化程度非常高,而且十分靈活。許多存儲(chǔ)器片可以結(jié)合到一起,形成一個(gè)混合了權(quán)重矩陣和神經(jīng)元的大型模型,如圖7所示。在本例中,MxN片配置通過(guò)各片間的模擬和數(shù)字接口連接到一起。

圖7:memBrain?的模塊化結(jié)構(gòu)

截至目前,我們主要討論了該架構(gòu)的芯片實(shí)施方案。提供軟件開發(fā)套件(SDK)可幫助開發(fā)解決方案。除了芯片外,SDK還有助于推斷引擎的開發(fā)。SDK流程與訓(xùn)練框架無(wú)關(guān)。用戶可以在提供的所有框架(例如TensorFlow、PyTorch或其他框架)中根據(jù)需要使用浮點(diǎn)計(jì)算創(chuàng)建神經(jīng)網(wǎng)絡(luò)模型。創(chuàng)建模型后,SDK可幫助量化受訓(xùn)神經(jīng)網(wǎng)絡(luò)模型,并將其映射到存儲(chǔ)器陣列。在該陣列中,可以利用來(lái)自傳感器或計(jì)算機(jī)的輸入向量執(zhí)行向量矩陣乘法。

圖8:memBrain? SDK流程

多級(jí)存儲(chǔ)器方法結(jié)合內(nèi)存內(nèi)計(jì)算功能的優(yōu)點(diǎn)包括:

1. 超低功耗:專為低功耗應(yīng)用設(shè)計(jì)的技術(shù)。功耗方面的第一個(gè)優(yōu)點(diǎn)是,這種解決方案采用內(nèi)存內(nèi)計(jì)算,因此在計(jì)算期間,從SRAM/DRAM傳輸數(shù)據(jù)和權(quán)重不會(huì)浪費(fèi)能量。功耗方面的第二個(gè)優(yōu)點(diǎn)是,閃存單元在閾下模式下以極低的電流運(yùn)行,因此有功功率消耗非常低。第三個(gè)優(yōu)點(diǎn)是待機(jī)模式下幾乎沒(méi)有能耗,原因是非易失性存儲(chǔ)器單元不需要任何電力即可保存始終開啟設(shè)備的數(shù)據(jù)。這種方法也非常適合對(duì)權(quán)重和輸入數(shù)據(jù)的稀疏性加以利用。如果輸入數(shù)據(jù)或權(quán)重為零,則存儲(chǔ)器位單元不會(huì)激活。

2. 減小封裝尺寸:該技術(shù)采用分離柵(1.5T)單元架構(gòu),而數(shù)字實(shí)施方案中的SRAM單元基于6T架構(gòu)。此外,與6T SRAM單元相比,這種單元是小得多。另外,一個(gè)單元即可存儲(chǔ)完整的4位整數(shù)值,而不是像SRAM單元那樣需要4*6 = 24個(gè)晶體管才能實(shí)現(xiàn)此目的,從本質(zhì)上減少了片上占用空間。

3. 降低開發(fā)成本:由于存儲(chǔ)器性能瓶頸和馮·諾依曼架構(gòu)的限制,很多專用設(shè)備(例如Nvidia的Jetsen或Google的TPU)趨向于通過(guò)縮小幾何結(jié)構(gòu)提高每瓦性能,但這種方法解決邊緣計(jì)算難題的成本卻很高。采用將模擬內(nèi)存內(nèi)計(jì)算與多級(jí)存儲(chǔ)器相結(jié)合的方法,可以在閃存單元中完成片上計(jì)算,這樣便可使用更大的幾何尺寸,同時(shí)降低掩膜成本和縮短開發(fā)周期。

邊緣計(jì)算應(yīng)用的前景十分廣闊。然而,需要首先解決功耗和成本方面的挑戰(zhàn),邊緣計(jì)算才能得到發(fā)展。使用能夠在閃存單元中執(zhí)行片上計(jì)算的存儲(chǔ)器方法可以消除主要障礙。這種方法利用經(jīng)過(guò)生產(chǎn)驗(yàn)證的公認(rèn)標(biāo)準(zhǔn)類型多級(jí)存儲(chǔ)器技術(shù)解決方案,而這種方案已針對(duì)機(jī)器學(xué)習(xí)應(yīng)用進(jìn)行過(guò)優(yōu)化。

作者簡(jiǎn)介

Vipin Tiwari在產(chǎn)品開發(fā)、產(chǎn)品營(yíng)銷、業(yè)務(wù)開發(fā)、技術(shù)許可、工程管理以及存儲(chǔ)器設(shè)計(jì)方面擁有20多年的豐富經(jīng)驗(yàn)。目前,Tiwari先生在Microchip的子公司Silicon Storage Technology, Inc.擔(dān)任嵌入式存儲(chǔ)器產(chǎn)品開發(fā)總監(jiān)。