IMEC是推動(dòng)半導(dǎo)體技術(shù)前進(jìn)的主要組織之一,日前,他們舉辦了一場(chǎng)線上論壇,談及了對(duì)芯片現(xiàn)狀和未來(lái)的看法。在演講中,ASML總裁則對(duì)光刻的發(fā)展進(jìn)行了演講。從他的PPT中可以看到,浸入式光刻在過去九年中增長(zhǎng)了兩倍。

而ASML計(jì)劃提高所有曝光工具每小時(shí)的晶圓數(shù)量。

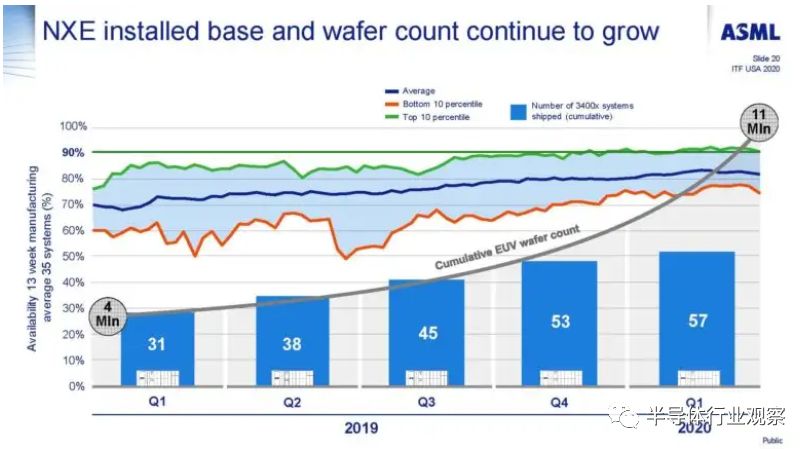

與此同時(shí), 他指出,EUV繼續(xù)為ASML的客戶提高產(chǎn)量,迄今為止,他們的客戶已經(jīng)使用EUV光刻機(jī)曝光了超過1100萬(wàn)個(gè)EUV晶圓,并交付了57個(gè)3400x EUV系統(tǒng)(3400平臺(tái)是EUV生產(chǎn)平臺(tái))。

ASML計(jì)劃繼續(xù)提高EUV吞吐量,同時(shí)減少每個(gè)晶圓的總能量。尤其是2倍的能源節(jié)省,這吸引了大家的高度關(guān)注。他們還期望通過NXE3800系統(tǒng)達(dá)到每小時(shí)30mj / cm2的劑量通量,已達(dá)到最高每小時(shí)225個(gè)晶圓的生產(chǎn)能力!

在演講中,IMEC高管也分享了他們對(duì)行業(yè)的看法。

據(jù)IMEC公司CEO Luc Van Den Hove表示,過去幾年來(lái),即使尺寸縮放速度變慢,但Design Technology Co Optimization(DTCO)也可以實(shí)現(xiàn)連續(xù)縮放。借助DTCO,工藝優(yōu)化已實(shí)現(xiàn)了標(biāo)準(zhǔn)邏輯單元軌道高度的減小。標(biāo)準(zhǔn)單元的高度是M2P( metal 2 pitch)乘以軌道(track)數(shù),而6 track cell 的高度代表了當(dāng)前的最新技術(shù)水平。

在他的演講中,Luc概述了一個(gè)路線圖,其中包括6條軌道的FinFET,讓路給具有埋入式電源軌(buried power rails)的5軌道納米片,然后增加了用于實(shí)現(xiàn)4.5條軌道納米片的叉板(forksheets ),4條軌道CFET以及最終具有2D通道的CFET。

他還強(qiáng)調(diào)了對(duì)功率,性能,面積和成本(PPAC)的需求。多年來(lái),基于功率,性能和面積(PPA)來(lái)表征前沿邏輯過程。例如,在最近的電話會(huì)議上,臺(tái)積電(TSMC)討論了他們的3nm工藝,即在相同功率下提供大約70%的邏輯密度,在相同性能下提高10-15%的速度,在相同性能下降低25-30%的功率。人們?cè)絹?lái)越認(rèn)識(shí)到,成本是新流程定義的必要要素。

Imec CMOS技術(shù)高級(jí)副總裁Sri Samavedan介紹了Imec先進(jìn)的半導(dǎo)體技術(shù)發(fā)展的最新情況。他表示,隨著邏輯縮放繼續(xù)達(dá)到3納米及以下,EUV將不得不過渡到多圖案化,直到可獲得高NA EUV。

他還提出了與Luc Van Den Hove的演講中類似的邏輯縮放路線圖,但有更多細(xì)節(jié),例如,要進(jìn)入5軌道單元,需要將電源導(dǎo)軌作為埋藏式電源導(dǎo)軌(BPR)移入基板。

在3D NAND中,關(guān)鍵挑戰(zhàn)之一是如何繼續(xù)有效地添加更多層。隨著堆棧變得越來(lái)越高,圖案化變得越來(lái)越難。Imec一直在尋找釕(Ru)替代水平字線板的鎢(W)。Imec相信,Ru可以幫助將線材的厚度從目前的大約30nm減小到大約15nm。就個(gè)人而言,我認(rèn)為Ru太昂貴了,無(wú)法在3D NAND中實(shí)現(xiàn),但是替代材料的概念很重要。

他還談到了邏輯的2D材料,并提供了有關(guān)MoS2的一些數(shù)據(jù),這些數(shù)據(jù)可以實(shí)現(xiàn)更細(xì)的通道和更短的通道長(zhǎng)度。

最后,我發(fā)現(xiàn)用于DRAM的低溫沉積銦鎵鋅氧化物(IGZO)的選擇很有趣。在邏輯,NAND和DRAM這三個(gè)主要的半導(dǎo)體產(chǎn)品領(lǐng)域中,DRAM面臨著最未知/最困難的擴(kuò)展挑戰(zhàn)。低溫沉積的低漏電晶體管可以使訪問晶體管和電容器堆疊在外圍邏輯上,從而增加DRAM密度。