老石按:

關(guān)于5G設(shè)備的芯片選擇,很多人陷入了ASIC和FPGA二選一的誤區(qū)。但是,小朋友才做選擇題,成年人根本沒得選。一方面,ASIC和FPGA本就不是有你沒我的正交關(guān)系;另一方面,F(xiàn)PGA的形態(tài)也在不斷演進(jìn)。所謂的異構(gòu)集成,在5G應(yīng)用里也不例外。

ASIC與FPGA的嘴仗打了十幾年

在5G第二波商用浪潮來臨之時

頗有戰(zhàn)況升級的意味

一種聲音是:5G應(yīng)用的復(fù)雜性和標(biāo)準(zhǔn)的不斷演進(jìn),將使FPGA力壓ASIC用量;另一種聲音則是:在成本和功耗壓力之下,5G基站所采用的FPGA平臺需要向ASIC過渡。

5G第二波,誰是絕佳選擇?

在5G發(fā)展初期,技術(shù)不成熟、基站總體數(shù)量并不多,F(xiàn)PGA現(xiàn)場可編程的優(yōu)勢很明顯。不同于FPGA的靈活性,定制化的ASIC一旦制造完成將不能更改設(shè)計,并且初期成本高、開發(fā)周期長。根據(jù)公開數(shù)據(jù),Xillinx認(rèn)為傳統(tǒng)的ASIC設(shè)計周期平均是14個月,通信設(shè)備若過分依賴使用ASIC,會讓設(shè)備商的終端產(chǎn)品晚上市6個月,在5年內(nèi)將少33%的利潤,等于損失14%的市場份額。而FPGA可以幫助設(shè)備商快速發(fā)展原型機(jī),快速交付,開發(fā)時間可以平均降低55%。

2019年末開始,局勢有了些微妙變化。

隨著5G基站數(shù)量進(jìn)入爆發(fā)階段,ASIC方案的規(guī)模經(jīng)濟(jì)效應(yīng)就顯露出來了。

業(yè)界紛紛預(yù)測,從2020年第一季度開始,基站基帶側(cè)會出現(xiàn)ASIC取代FPGA的現(xiàn)象。去年底還有一個標(biāo)志性事件,諾基亞宣布使用SoC來替代FPGA開發(fā)5G芯片組。官方解釋是,之前認(rèn)為FPGA具備可編程能力,更能滿足運(yùn)營商的使用需求。但是由于使用FPGA開發(fā)芯片推高了5G網(wǎng)絡(luò)設(shè)備的單價,并且耗電量也比使用SoC的設(shè)備要高,所以決定取消這一計劃。

種種跡象,對FPGA都不妙。但是ASIC就是絕佳選擇嗎?

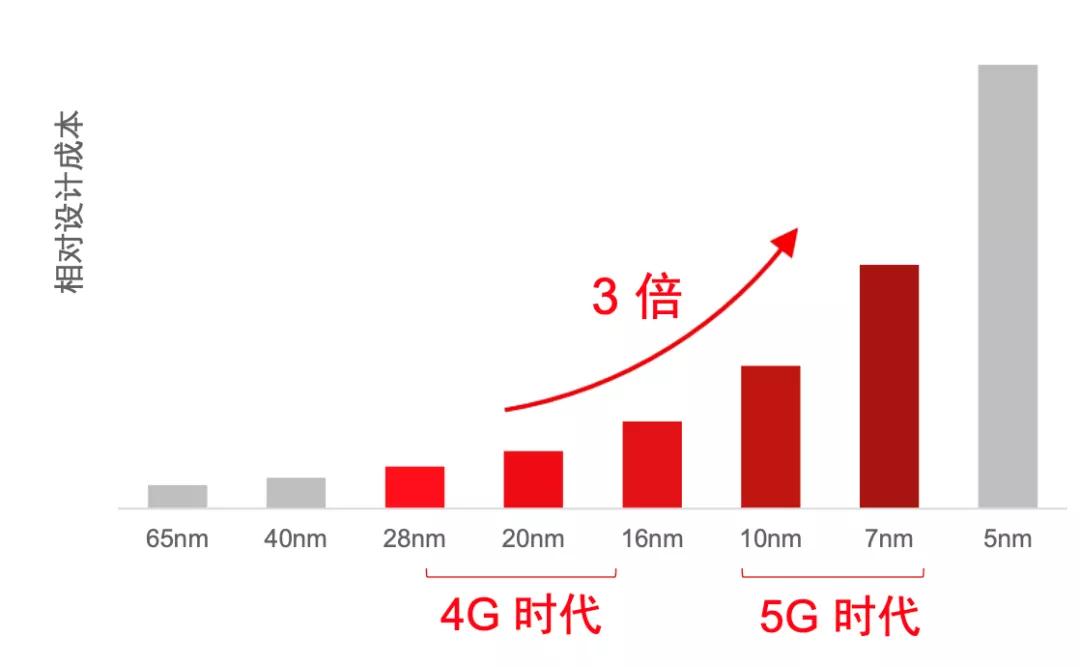

摩爾定律到了舉步維艱的地步,僅從節(jié)點(diǎn)的進(jìn)步來提升處理的效率已經(jīng)越來越困難。而測算4G與5G時代的ASIC NRE成本,卻是幾乎3倍的增加。另外,5G標(biāo)準(zhǔn)仍在持續(xù)演進(jìn)中,兩年以上的開發(fā)周期仍是ASIC一大硬傷,畢竟誰也無法精準(zhǔn)預(yù)判未來。而最為不同的一點(diǎn)是,5G帶來了多樣性的需求,這對于以規(guī)模經(jīng)濟(jì)取勝的ASIC,在某些碎片又量小的應(yīng)用面前,就被縛住了手腳。

5G第二波商用浪潮來臨之際,ASIC經(jīng)濟(jì)學(xué)并不可行,純FPGA方案在成本與功耗方面又有掣肘。還有第三條路嗎?

FPGA的權(quán)衡之道

在第三條道路的探索上,Xilinx進(jìn)行了一次不同以往的嘗試。今日發(fā)布的Zynq RFSoC DFE,將硬化的數(shù)字前端(DFE)模塊與靈活應(yīng)變的可編程邏輯相結(jié)合,這也是Xilinx史上首次推出這樣一款硬化專用IP多于自適應(yīng)邏輯的無線電平臺。

根據(jù)Xilinx有線與無線事業(yè)部高級總監(jiān)Gilles Garcia的解讀,這一創(chuàng)新旨在滿足不斷演進(jìn)的 5G NR 無線應(yīng)用標(biāo)準(zhǔn),為了涵蓋低、中、高頻段頻譜的廣泛用例,Zynq RFSoC DFE在采用硬化模塊的ASIC的成本效益與可編程、自適應(yīng)SoC的靈活性、可擴(kuò)展性及上市時間優(yōu)勢之間,找到了技術(shù)平衡。

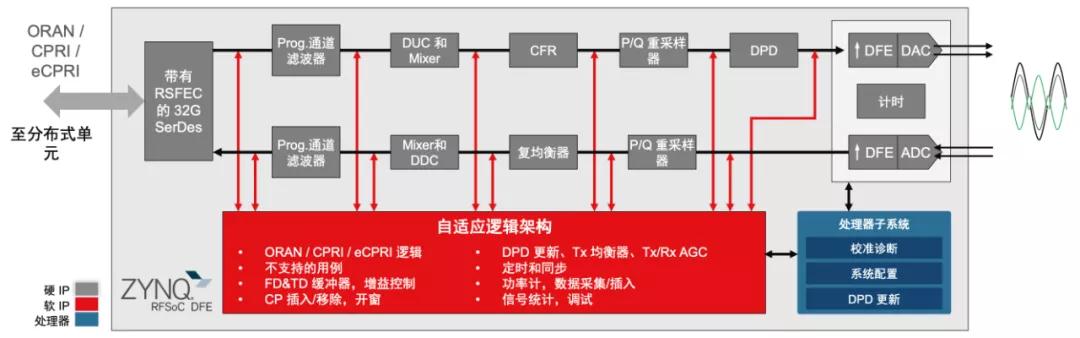

從器件架構(gòu)來看,主要包括處理器子系統(tǒng)(四核Arm Cortex-A53、雙核Arm Cortex-R5F)、少量的可編程邏輯單元、RF和數(shù)字前端子系統(tǒng)。可以看到,在RF和數(shù)字前端子系統(tǒng)硬化的ASIC IP中,包括了一個完整的DFE模塊鏈。

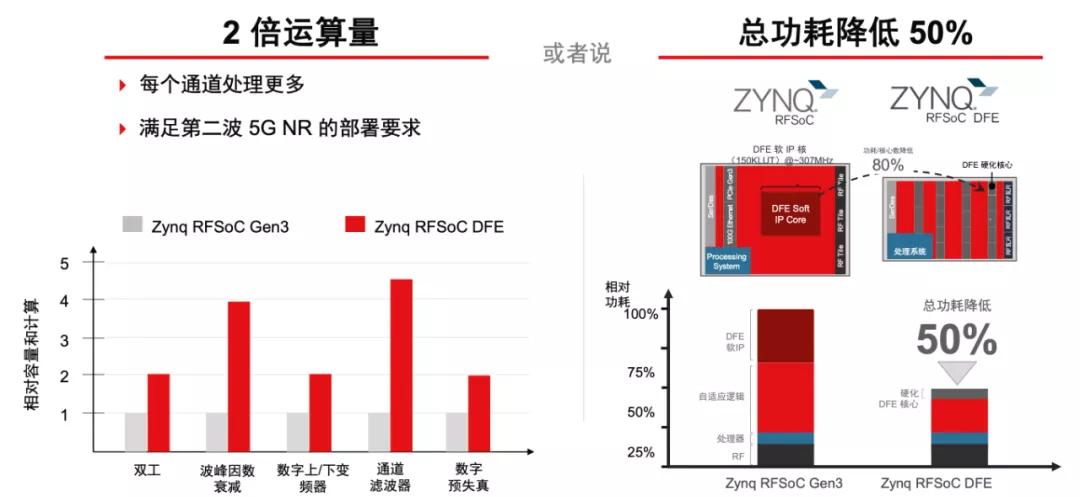

事實(shí)上,Xilinx已經(jīng)推出過三代Zynq RFSoC產(chǎn)品,在前幾代產(chǎn)品中,這些DFE IP以軟IP的形式存在于可編程邏輯單元中。而實(shí)現(xiàn)硬化之后,與上一代產(chǎn)品相比,Zynq RFSoC DFE將單位功耗性能提升高達(dá)兩倍,并且能夠從小蜂窩擴(kuò)展至大規(guī)模MIMO(mMIMO)宏蜂窩。

通過在集成度和靈活性方面的權(quán)衡設(shè)計,該解決方案能夠在所有FR1頻帶和新興頻帶(最高7.125GHz)內(nèi)實(shí)現(xiàn)載波聚合/共享、多模式、多頻帶400MHz瞬時帶寬。當(dāng)用作毫米波中頻收發(fā)器時,Zynq RFSoC DFE可提供1600 MHz的瞬時帶寬。

在靈活性方面,支持用戶繞過或定制硬化的IP模塊,可以利用支持現(xiàn)有和新興GaN Pas的DPD,也可以插入其自有的DPD IP。

5G的多樣化需求和復(fù)雜性

5G與4G相比,不僅是網(wǎng)絡(luò)帶寬方面的升級,在運(yùn)營管理模式上也有許多新的訴求。因此未來的網(wǎng)絡(luò)不再是單一設(shè)備商甚至單一運(yùn)營商包打天下,而是一個豐富的生態(tài)圈,因此開放性、靈活性尤為重要。

就5G無線電而言,所需的解決方案不僅要滿足廣泛部署所提出的帶寬、功耗和成本挑戰(zhàn),還必須適應(yīng)三大關(guān)鍵5G用例:增強(qiáng)型移動寬帶(eMBB)、大規(guī)模機(jī)器類通信(mMTC)以及超可靠低時延通信(URLLC)。此外,解決方案必須能夠隨不斷演進(jìn)的5G標(biāo)準(zhǔn)進(jìn)行擴(kuò)展,如OpenRAN(O-RAN)、全新的顛覆性5G商業(yè)模式。

Gilles Garcia談到,5G正在經(jīng)歷第二波的大規(guī)模部署,每個通道需要處理更多,需要有更高的瞬時帶寬,更高的集成度水平,另外還有降低功耗,有更高的容量和更低的成本,這是設(shè)計這一款新的Zynq RFSoC DFE架構(gòu)的初衷。而新的用例仍在不斷涌現(xiàn),例如虛擬現(xiàn)實(shí)、車聯(lián)網(wǎng)等等,這些應(yīng)用都要求低延時、低錯誤率,只有高度集成的類似ASIC、但同時又可編程的平臺,才可以滿足這些需求。

你中有我、我中有你的新業(yè)態(tài)

在Gilles Garcia看來,ASIC的經(jīng)濟(jì)性和可行性會隨著5G的不斷部署下降,單一方案無法滿足成本、功耗、效率等多方面需求。在百萬量級的無線電單元部署中,即大型的OEM硬件廠商中,ASIC仍然是合適的選擇。不過,5G一個顯著的趨勢就是碎片化應(yīng)用越來越顯著,對于無線電單元量級在50萬以下的應(yīng)用中,RFSoC DFE更有競爭力。預(yù)計5G在未來十年還會不斷地升級,不排除一些原來采用ASIC戰(zhàn)略的用戶,會轉(zhuǎn)向RFSoC DFE,因?yàn)樗傮w置有成本更低,性能、功能更優(yōu)越,還能加速上市速度。

對于未來即將發(fā)生的改變,Xilinx不是唯一做好準(zhǔn)備的FPGA廠商。

Intel繼收購Altera之后,于2018年收購了芯片公司eASIC,該公司提供一種介于FPGA與ASIC中間的技術(shù)。通過半成品的結(jié)構(gòu)化ASIC,能夠節(jié)省NRE費(fèi)用和設(shè)計時間,而芯片的性能和功耗又接近標(biāo)準(zhǔn)單元ASIC。此舉被看作是Intel在FPGA和標(biāo)準(zhǔn)ASIC之間的戰(zhàn)略布局。

相應(yīng)的還有eFPGA的形式,例如Achronix,F(xiàn)lex Logix等廠商,通過將一個或多個FPGA以IP的形式嵌入ASIC或SoC等芯片中,實(shí)現(xiàn)數(shù)字可重構(gòu)的結(jié)構(gòu),從而使芯片實(shí)現(xiàn)更高的靈活性和可重新配置的特性。

ASIC還是FPGA?未來的競爭邊界被模糊,一方面,各自有其存在的空間和必要性,另一方面,你中有我、我中有你的新架構(gòu)在萌發(fā)。如果一定要說出一個贏家,那就是混合架構(gòu)的SoC。

就在昨晚,AMD和Xilinx聯(lián)合宣布,已就AMD以全股票交易收購Xilinx達(dá)成最終協(xié)議,交易總價值350億美元。更強(qiáng)大的產(chǎn)品組合呼之欲出,結(jié)合CPU、GPU、FPGA、自適應(yīng)SoC以及相關(guān)的軟件工具,對于雙方來說,這是不是都是一步好棋?