目前,深度神經網(wǎng)絡技術已經成為人工智能領域的代表性算法,基于深度神經網(wǎng)絡技術的字符識別、圖像分類或語音識別等關鍵技術,已經廣泛應用于搜索引擎和智能手機等產品中。

其中,當前最為有效且應用最為廣泛的神經網(wǎng)絡算法是卷積神經網(wǎng)絡算法,簡稱“卷積運算”。在現(xiàn)有技術中,CNN算法的核心計算單元是乘加運算,乘法累加器陣列常用于矩陣乘法運算,而卷積運算可以轉換為矩陣乘法運算。

因此業(yè)界廣泛采用MAC(乘累加器)陣列為計算核心的專用加速硬件,例如:現(xiàn)場可編程門陣列(FPGA)、專用集成電路(ASIC)等,以加速卷積運算的運算速度。

但是目前卷積計算也存在著一些問題,一方面,當MAC陣列中存在多個卷積窗口同時進行卷積運算時,這些卷積窗口分布在MAC陣列中的不同位置,使得MAC陣列的利用率非常低。另一方面,存在大量重復數(shù)據(jù)被從RAM輸入到MAC陣列,這樣會增加RAM的訪問次數(shù)。

為了解決這樣的問題,華為發(fā)明了將CPU、RAM和卷積運算芯片集成在同一數(shù)據(jù)總線上的AI芯片,2016年12月29日,華為發(fā)明了一項名為“卷積運算芯片和通信設備”的發(fā)明專利(申請?zhí)枺?01611243272.X),申請人為華為機器有限公司。

根據(jù)該專利目前公開的資料,讓我們一起來看看華為的這項新架構AI芯片吧。

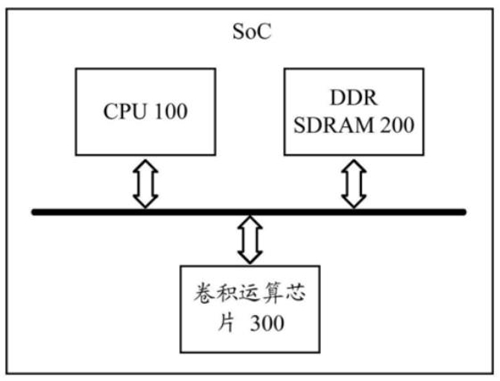

如上圖,為該專利中發(fā)明的硬件設備的示意性框架圖,硬件架構中包括中央處理器100、雙倍速率同步動態(tài)隨機存儲器(DDR SDRAM)200以及卷積運算芯片300。CPU用來控制卷積運算芯片啟動卷積運算,DDR SDRAM用于向卷積運算芯片的數(shù)據(jù)緩存模塊輸入多個卷積數(shù)據(jù)和多個卷積參數(shù),然后卷積運算芯片根據(jù)這些數(shù)據(jù)來完成卷積運算。

當?shù)玫竭\算結果后,就會將運算結果寫回到DDR SDRAM事先設定好的內存地址中,并同時通知CPU完成運算,以從內存地址中提取結果數(shù)據(jù)。

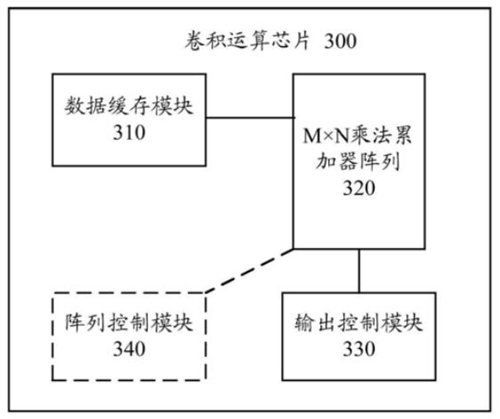

如上圖,為上面框架中的卷積運算芯片的結構示意圖,這種卷積運算芯片包括數(shù)據(jù)緩存模塊310、M*N乘法累加器陣列320、輸出控制模塊330和陣列控制模塊340。

數(shù)據(jù)緩存模塊用于向乘法累加器中的第一乘法累加窗口傳輸用于卷積運算的多個卷積數(shù)據(jù)和卷積參數(shù),卷積參數(shù)由數(shù)據(jù)緩存模塊根據(jù)第一卷積參數(shù)矩陣確定,而該控制器也是通過在運算器內集成這樣的數(shù)據(jù)緩存器,從而減少了RAM的訪問次數(shù),進而減少了RAM的訪問壓力。

其中M*N乘法累加器是該運算芯片的核心運算部件,而這種M*N的結構設計方式也是為了進行卷積運算而特意設計的,其具體結構如下圖所示。

可以看到,這種乘法累加器包括M*N個處理單元,并且每兩行的處理單元之間還存在斜向的數(shù)據(jù)傳輸通道,這相比于傳統(tǒng)的矩陣式數(shù)據(jù)傳輸通道,具有更加靈活的數(shù)據(jù)傳輸方式,可以更好的適用于AI芯片進行多種類型的運算。

第一乘法累加窗口可以將數(shù)據(jù)進行乘法運算,并接著進行加法運算以獲得卷積結果,最后由輸出控制模塊輸出卷積神經網(wǎng)絡的運算結果,進而完成AI芯片中的任務。

在該專利中,為了盡可能地提高MAC陣列的利用率以及卷積運算效率,陣列控制模塊會根據(jù)第一卷積參數(shù)矩陣的行數(shù)和第一卷積數(shù)據(jù)陣列的行數(shù)來確定第一乘法累加窗口的列數(shù)。

華為發(fā)明的卷積運算芯片,這種卷積運算芯片能夠在提高陣列資源利用率的同時降低RAM訪問次數(shù),進而減小RAM的訪問壓力。例如華為發(fā)明的昇騰AI芯片也正是基于這樣的技術之上,才能實現(xiàn)極高的算力,不管多么復雜的模型都可以輕松訓練,且實現(xiàn)極低的功耗。