摘要:芯片制造用到的技術(shù)很多,光刻是芯片制造的靈魂技術(shù),但是開(kāi)始的時(shí)候,光刻并不是所有技術(shù)中最厲害的。現(xiàn)在大眾認(rèn)識(shí)到了芯片的重要性,討論芯片產(chǎn)業(yè)的卡脖子問(wèn)題時(shí),提到最多的是光刻和光刻機(jī)。那么,光刻是如何一步一步變成了芯片制造的卡脖子技術(shù)?本文試圖一探究竟。

光刻技術(shù)是利用光學(xué)和化學(xué)反應(yīng)的原理,以及利用化學(xué)和物理的刻蝕方法,把電路圖形制作到半導(dǎo)體基片、或者下一層介質(zhì)材料之上,經(jīng)過(guò)有序的多次光刻工序疊加,最終把立體的電路結(jié)構(gòu)制作在半導(dǎo)體基片上,形成完整功能的芯片。

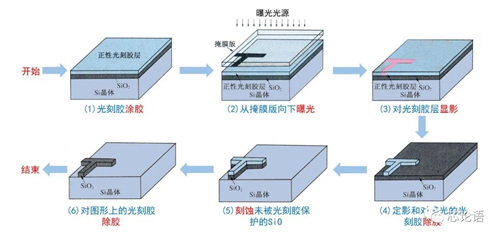

圖1.光刻工藝過(guò)程的示意圖

圖1是光刻工藝過(guò)程的示意圖。假設(shè)要在硅(Si)基片上光刻一個(gè)二氧化硅(SiO2)的T形圖案,大致要經(jīng)過(guò)6個(gè)工序。在光刻之前,首先在Si基片上生長(zhǎng)一層SiO2層,然后從光刻膠的涂膠開(kāi)始,經(jīng)歷涂膠、曝光、顯影、除膠、刻蝕、除膠等步驟。從圖上可以看到,第4步以及之前的過(guò)程為下一步刻蝕SiO2層上要去除的區(qū)域劃定了范圍。第5步是實(shí)際的加工過(guò)程——刻蝕,第6步是收尾過(guò)程,目的是清除SiO2的T形圖案上不需要的光刻膠。因此說(shuō),光刻有兩個(gè)階段,一是劃定范圍,二是針對(duì)劃定范圍進(jìn)行實(shí)際加工。

上述的光刻工藝過(guò)程與傳統(tǒng)照相的曝光和洗相過(guò)程很類似,理解起來(lái)并不困難。但是照相是一個(gè)過(guò)渡性的光學(xué)和化學(xué)反應(yīng)過(guò)程,并且過(guò)渡性的層次越多,照片影像就越細(xì)膩越好。而光刻是一個(gè)突變性的光學(xué)和化學(xué)反應(yīng)過(guò)程,要求突變盡可能快,圖形邊界越清晰越好。為了追求邊界越清晰、線條越細(xì)致的目標(biāo),光刻技術(shù)走過(guò)了漫長(zhǎng)的技術(shù)創(chuàng)新之路。

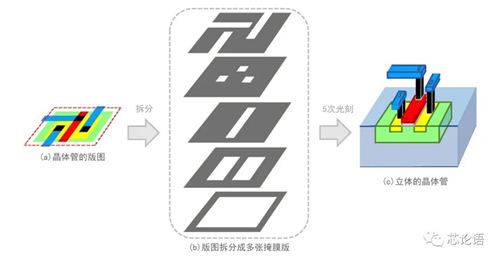

圖2.多次光刻工序“堆疊”形成立體的電路結(jié)構(gòu)

圖2是多次光刻工序“堆疊”形成立體的電路結(jié)構(gòu)的示意圖。圖2(a)是一個(gè)晶體管的版圖。版圖按照制造工藝被拆分為至少5層掩膜版,如圖2(b)所示。芯片制造過(guò)程中要為每一層掩膜版安排一次光刻工序,經(jīng)過(guò)5次光刻工序后,立體的晶體管就“堆疊”而成了,如圖2(c)所示。

通俗地講,芯片制造就是在半導(dǎo)體基片上,用光刻在一層材料上“雕刻”形成特定圖形,一層一層的光刻實(shí)際上是縱向“堆疊”這些圖形,組成立體的晶體管、電路元件和連線等,最終形成具有完整電路功能的芯片。

一、為什么說(shuō)光刻技術(shù)是靈魂技術(shù)?

光刻技術(shù)是芯片制造中的靈魂技術(shù),如果沒(méi)有它的存在,芯片技術(shù)就不可能存在并快速發(fā)展。光刻之所以是靈魂技術(shù),因?yàn)楣饪桃獮槠渌酒庸ぜ夹g(shù)劃定加工范圍,光刻就像槍炮的瞄準(zhǔn)裝置一樣重要。其它加工技術(shù)不論多么復(fù)雜、多么高難度,也只有在光刻存在的前提下才能發(fā)揮作用。例如,要依賴光刻確定晶體管的多晶硅柵(Poly Gate)和金屬連線(Metal)的圖形、位置和走向等;要依靠光刻為擴(kuò)散區(qū)(Diffusion)、注入阱(Implant Well)、上下層過(guò)孔(Via、Contact)打開(kāi)加工窗口等。所以,沒(méi)有光刻技術(shù)其它加工技術(shù)就無(wú)從談起。

從芯片的設(shè)計(jì)數(shù)據(jù)傳導(dǎo)到芯片制造的過(guò)程來(lái)看,傳導(dǎo)路徑非常清晰,那就是芯片設(shè)計(jì)版圖 -> 掩膜版 -> 光刻 -> 加工。一顆芯片的設(shè)計(jì)版圖要按照制造工藝分解為一套多張(層)的掩膜版,每張掩膜版對(duì)應(yīng)著一次光刻和加工過(guò)程。所以,光刻是芯片制造的靈魂技術(shù)。

進(jìn)入二十一世紀(jì),隨著半導(dǎo)體技術(shù)的發(fā)展,光刻的精度不斷提高,已由微米級(jí)、亞微米級(jí)、深亞微米級(jí),細(xì)化到目前的納米級(jí),光刻用的光源也從常規(guī)光源發(fā)展到應(yīng)用電子束、X射線、微離子束、激光等新技術(shù),光刻成為最精密的微細(xì)加工技術(shù),也是芯片制造最為關(guān)鍵的技術(shù)。如果光刻的核心設(shè)備、材料等被個(gè)別國(guó)家壟斷和管控的話,光刻技術(shù)就成了“卡”其他國(guó)家芯片產(chǎn)業(yè)“脖子”的關(guān)鍵核心技術(shù)。

二、芯片制造中還要用到哪些技術(shù)?

芯片制造除了用到光刻技術(shù),還有很多其它技術(shù),例如刻蝕、氧化、擴(kuò)散、淀積、離子注入等。1.刻蝕是用化學(xué)或物理方法有選擇地從半導(dǎo)體材料表面去除不需要的材料的過(guò)程,光刻和刻蝕結(jié)合起來(lái),就可以在半導(dǎo)體材料上正確地復(fù)制掩模版上的圖形;2.氧化是在指定區(qū)域生成一層氧化膜;3.擴(kuò)散是對(duì)指定區(qū)域定量摻入其它元素原子,改變?cè)搮^(qū)域的電性能;4.淀積是在指定區(qū)域沉積一層氧化硅、碳化硅、多晶硅等半導(dǎo)體材料薄層;5.離子注入是向指定區(qū)域定量注入雜質(zhì)的原子或粒子,使該區(qū)域的電性能發(fā)生變化。與擴(kuò)散相比,離子注入沒(méi)有外溢效應(yīng),離子注入深度和注入量比較好控制。

在芯片技術(shù)發(fā)展早期,光刻并不是所有技術(shù)中最厲害的。受制于原始簡(jiǎn)陋的掩膜版制作和制造工藝,芯片工藝采用毫米級(jí)、微米級(jí),因而芯片上集成的晶體管等電路元件的數(shù)量也極其有限。所以,光刻采用人工(或計(jì)算機(jī)輔助)刻紅膜、微縮照相制版、傳統(tǒng)光源曝光等簡(jiǎn)單方式還是可行的。但是刻蝕、氧化、擴(kuò)散、淀積、離子注入等技術(shù)相關(guān)的設(shè)備、材料、控制等技術(shù)問(wèn)題反而更難把握,當(dāng)時(shí)這些技術(shù)成為芯片制造中最受關(guān)注和大力創(chuàng)新的方向。

三、芯片技術(shù)經(jīng)歷了哪些發(fā)展階段

芯片制造技術(shù)伴隨光刻技術(shù)一路走來(lái),大致經(jīng)歷了非常原始的“石器”時(shí)代,走過(guò)了用計(jì)算機(jī)輔助的半自動(dòng)化時(shí)代,隨后進(jìn)入了EDA全自動(dòng)化時(shí)代。我國(guó)芯片技術(shù)與國(guó)外大致同時(shí)起步,由于眾所周知的原因,我們的發(fā)展階段基本落后于國(guó)外約10年的時(shí)間。改革開(kāi)放以來(lái),我們加快了學(xué)習(xí)和趕超的步伐,目前,我國(guó)光刻技術(shù)的應(yīng)用水平基本與國(guó)外保持同步,但核心技術(shù)和設(shè)備基本依賴于國(guó)外。

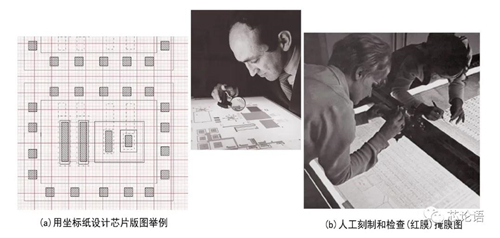

芯片的“石器”時(shí)代(國(guó)外1958~1975年前后,國(guó)內(nèi)1958~1985年前后)。之所以稱為芯片行業(yè)的“石器”時(shí)代,是因?yàn)樾酒O(shè)計(jì)工具和制作光刻掩膜版的方法十分原始。這個(gè)時(shí)期,芯片設(shè)計(jì)時(shí)用到了普通坐標(biāo)紙,如圖3(a)所示,版圖由手工繪制;制作掩膜版時(shí)用到紅膜(Rubylith),如圖3(b)所示。紅膜是透明基片上附有極薄紅膜,紅膜遮光性強(qiáng),如果切開(kāi)紅膜某個(gè)圖形的邊界(不切斷基片),圖形外的紅膜就可以從透明基片上揭掉,圖形外的區(qū)域就變成透明,紅膜保留的地方作為遮光部分,可制成過(guò)渡掩膜版。它再經(jīng)過(guò)微縮照相制版,最終制成工作掩膜版。

圖3.早期用坐標(biāo)紙畫(huà)芯片版圖、人工刻制和檢查過(guò)渡掩膜版(紅膜)

當(dāng)時(shí)人們?cè)O(shè)計(jì)芯片時(shí),首先要在坐標(biāo)紙上畫(huà)出芯片版圖,版圖上不同的圖層采用不同線條或陰影線來(lái)表示,這個(gè)過(guò)程稱為設(shè)計(jì)版圖或者畫(huà)版圖。然后,再把坐標(biāo)紙上的版圖按1:1的比例分層復(fù)制到不同張的紅膜上去,然后手工刻掉紅膜上不需要的部分,只保留版圖上的圖形,這個(gè)過(guò)程稱為刻紅膜。多層紅膜構(gòu)成了芯片的一套過(guò)渡掩膜版。

由于過(guò)渡掩膜版的尺寸較大,要經(jīng)過(guò)多次微縮照相,最后把過(guò)渡掩膜版上的圖形縮小并復(fù)制到工作掩膜版上去。工作掩膜版是用非常平整的石英玻璃板上鍍一層鉻膜制造而成。紅膜上的圖形與鉻膜上的圖形完全相同,比例不同。有鉻膜的地方不透光,沒(méi)有鉻膜的地方透明。工作掩膜版是制造芯片時(shí)在光刻工藝中用到的掩膜版。

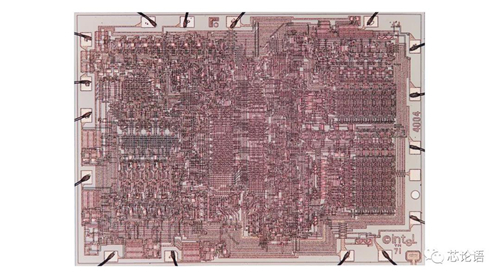

在芯片制造的“石器”時(shí)代,芯片版圖靠手工繪制,紅膜上的圖案靠人工刻出,不可能設(shè)計(jì)和制造出規(guī)模很大的芯片,這種小規(guī)模(SSI)芯片上集成的晶體管數(shù)大約在幾十~幾百只之間。1971年Intel推出全球首個(gè)4位中央處理器(CPU)芯片4004。它集成了2250只晶體管,采用10μm工藝,這已經(jīng)是當(dāng)時(shí)規(guī)模很大的芯片了。4004芯片內(nèi)部照片如圖4所示。該芯片的掩膜版是否是用人工刻紅膜的方式制作,筆者無(wú)法確定。如果是用人工方式刻紅膜,那么它的工作量是十分巨大的,但也是可行的。想想當(dāng)年我國(guó)研制兩單一星時(shí),滿屋子的人打算盤計(jì)算原子彈爆炸數(shù)據(jù)的情景,這都不算事兒!

圖4. Intel4004處理器芯片的內(nèi)部照片(資料來(lái)源:sisite.tw)

2.計(jì)算機(jī)輔助的時(shí)代(國(guó)外1975~1990年前后,國(guó)內(nèi)1985~1995年前后):這個(gè)時(shí)期人們?cè)O(shè)計(jì)芯片時(shí),既可以用坐標(biāo)紙畫(huà)版圖,也可以在電腦上設(shè)計(jì)版圖,坐標(biāo)紙上的版圖要通過(guò)數(shù)字化儀(Digitizer)輸入到計(jì)算機(jī)中,計(jì)算機(jī)中的版圖可以在電腦屏幕上檢查或修改(例如L-EDIT軟件等),或者進(jìn)行晶體管等電路器件的模擬(例如SPICE軟件等)。最后電腦控制繪圖儀繪制版圖以供檢查或存檔,或者通過(guò)刻圖機(jī)刻紅膜,最后經(jīng)過(guò)微縮照相,把過(guò)渡掩膜版轉(zhuǎn)換成工作掩膜版。

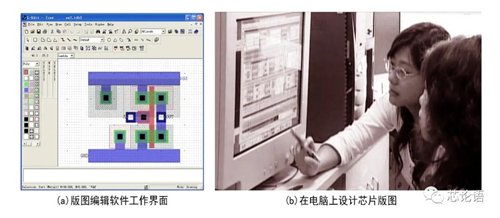

圖5(a)是Tanner Research公司版圖編輯軟件(L-EDIT)的用戶工作界面,版圖中不同的掩膜層用不同的顏色或填充圖案表示。圖5(b)是設(shè)計(jì)人員利用L-EDIT在電腦上繪制和檢查芯片版圖的場(chǎng)景。

圖5.利用L-EDIT軟件在電腦上設(shè)計(jì)版圖

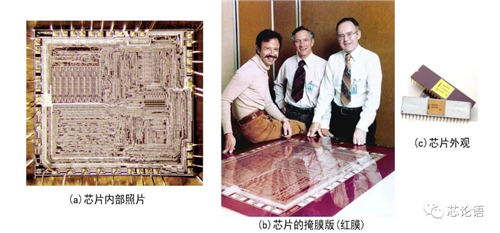

1974年,Intel推出了8位CPU芯片8080,它采用6μm工藝制造,其上集成了6000多個(gè)晶體管。圖6(a)是8080處理器芯片的內(nèi)部照片。圖6(b)是Intel三位創(chuàng)始人與8080CPU的一張掩膜版(紅膜)合影留念。圖6(c)是8080 CPU的封裝外觀圖。

圖6. Intel三位創(chuàng)始人在8080CPU的一張掩膜版(紅膜)后面合影(從左到右是安迪。格羅夫、羅伯特。諾伊斯、戈登。摩爾,資料來(lái)源:sisite.tw)

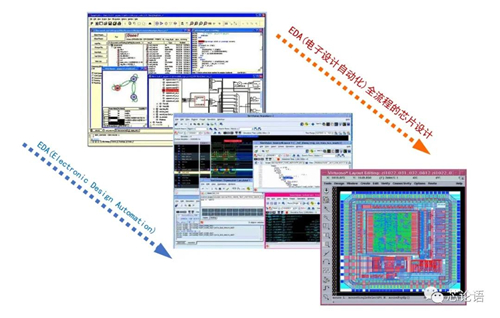

3.設(shè)計(jì)自動(dòng)化時(shí)代(國(guó)外1990年~今天,國(guó)內(nèi)1995年~今天):這個(gè)時(shí)期,人們普遍采用電子設(shè)計(jì)自動(dòng)化(EDA)軟件,在電腦上完成芯片邏輯設(shè)計(jì)、模擬仿真和版圖設(shè)計(jì)等,設(shè)計(jì)數(shù)據(jù)送到制造廠,通過(guò)自動(dòng)化設(shè)備完成芯片掩膜版的制作,最后整套掩膜版將用于芯片制造中的各道光刻工序。

這個(gè)時(shí)期,多家EDA公司通過(guò)不斷整合、兼并和重組,大浪淘沙,形成了目前國(guó)外EDA軟件廠商的三巨頭,出現(xiàn)了Synopsys、Cadence和MentorGraphics三家獨(dú)霸世界EDA軟件市場(chǎng)的局面。他們先后于1990年~1995年進(jìn)入中國(guó)市場(chǎng),加快了中國(guó)芯片設(shè)計(jì)產(chǎn)業(yè)的發(fā)展。這個(gè)時(shí)期的芯片制造工藝沿著摩爾定律快速迭代和升級(jí),工藝特征線寬由0.35μm縮小到今天的5nm。這些進(jìn)展的兩大關(guān)鍵支撐條件一是EDA軟件,二是光刻機(jī)。

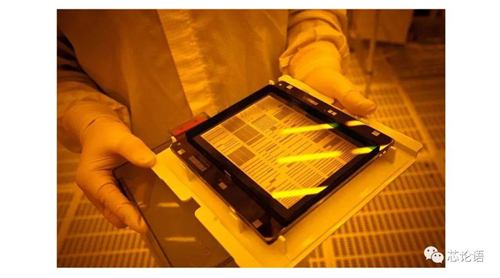

圖7.自動(dòng)化生產(chǎn)線上用的光刻掩膜版

圖8.全流程EDA軟件設(shè)計(jì)芯片的圖例

現(xiàn)在的芯片設(shè)計(jì)過(guò)程,從芯片的功能設(shè)計(jì),到電路結(jié)構(gòu)設(shè)計(jì),再到芯片版圖的物理實(shí)現(xiàn),全部借助于EDA軟件來(lái)完成,其中還包括復(fù)雜而精確的設(shè)計(jì)檢查、模擬仿真等,可以保證容納了上百億只晶體管的芯片設(shè)計(jì)萬(wàn)無(wú)一失。

現(xiàn)代光刻技術(shù)中,掩膜版制作實(shí)現(xiàn)了由EDA軟件輸出數(shù)據(jù)->掩膜版制作的自動(dòng)化,光刻過(guò)程實(shí)現(xiàn)了由光刻機(jī)、刻蝕機(jī)實(shí)現(xiàn)的自動(dòng)化。目前ASML EUV光刻機(jī)已實(shí)現(xiàn)了7nm、5nm工藝,正在研制的新一代EUV光刻機(jī)可實(shí)現(xiàn)1nm工藝。因此,今天的芯片技術(shù)處在一個(gè)全自動(dòng)化的設(shè)計(jì)和制造的時(shí)代。

四、摩爾定律使光刻技術(shù)成為王者

在芯片技術(shù)的三個(gè)發(fā)展階段中,光刻技術(shù)的原理是簡(jiǎn)單明了的,始終保持不變,變化的是光刻線條更細(xì),光刻精度更高。人們對(duì)芯片更小、更快和更好的需求,是推動(dòng)光刻技術(shù)創(chuàng)新發(fā)展的唯一動(dòng)力,而發(fā)展規(guī)律則是摩爾定律。

摩爾定律預(yù)示著每?jī)赡瓴坏降臅r(shí)間里,芯片集成度就要翻倍,在保證芯片面積不變的情況下,制造工藝的特征線寬就要減半或縮小。必然要求光刻精度不到兩年時(shí)間要提高一倍,對(duì)光刻技術(shù)和設(shè)備都提出了嚴(yán)苛的要求。

圖9.芯片制造工藝節(jié)點(diǎn)圖譜(資料來(lái)源:m.sohu.com)

從圖9芯片制造工藝節(jié)點(diǎn)圖譜,大致可以看到光刻機(jī)及光刻技術(shù)逐年進(jìn)步的影子,也可以感受到正是摩爾定律把光刻技術(shù)一步一步推到越來(lái)越重要的地位。進(jìn)入14nm工藝節(jié)點(diǎn)以后,光刻機(jī)技術(shù)難度陡然上升,ASML EUV光刻機(jī)的售價(jià)達(dá)到1.2億美元,光刻機(jī)設(shè)備成本占到所有制造設(shè)備成本的35%,光刻工序占到所有制造工時(shí)的40%左右。光刻技術(shù)成為芯片制造中真正的王者,因而成為芯片制造中最容易被“卡脖子”的技術(shù)。

結(jié)語(yǔ):芯片產(chǎn)業(yè)沿著摩爾定律的規(guī)律一路走來(lái),制造工藝特征線寬跨越當(dāng)前的7nm、5nm、3nm的節(jié)點(diǎn)后,光刻技術(shù)將面臨著物理極限的挑戰(zhàn),光刻技術(shù)成為了芯片產(chǎn)業(yè)中的技術(shù)王者。由于光刻技術(shù)和設(shè)備主要被外國(guó)公司壟斷,光刻成為我國(guó)芯片產(chǎn)業(yè)的卡脖子技術(shù)。如何解決這個(gè)卡脖子問(wèn)題,需要國(guó)家大力扶持和科技人員的艱苦努力。同時(shí),還必不可少地需要較長(zhǎng)時(shí)間的技術(shù)積累。