串行器/解串器(SerDes)電路多年來(lái)一直在幫助芯片間進(jìn)行告訴數(shù)據(jù)通信,但新的工藝技術(shù)正迫使它以意想不到的方式進(jìn)行調(diào)整和改變。

傳統(tǒng)上作為模擬電路實(shí)現(xiàn)的SerDes技術(shù)一直難以進(jìn)一步縮小尺寸,而低電壓、變化和噪聲則使其更難獲得充分的量產(chǎn)。因此,為了保持相關(guān)性,它在架構(gòu)上已經(jīng)轉(zhuǎn)變?yōu)閺?fù)雜的混合信號(hào)電路,它越來(lái)越依賴數(shù)字信號(hào)處理來(lái)處理半導(dǎo)體和通道中的缺陷。

先進(jìn)封裝對(duì)SerDes提出了新的要求,同時(shí)在涉及異構(gòu)芯片時(shí)也提供了新的機(jī)會(huì)。現(xiàn)在,可以將SerDes設(shè)計(jì)與核心設(shè)計(jì)脫鉤,從而為每種工藝提供最佳選擇。但是先進(jìn)的封裝也為芯片之間的通信提出了全新的需求。關(guān)于這是并行通信還是串行通信通道,或者即使電氣通信具有長(zhǎng)期作用,仍需進(jìn)行評(píng)審。

保持不變的一件事是,用于移動(dòng)數(shù)據(jù)的驅(qū)動(dòng)器并未減慢速度。“我們看到了對(duì)高速數(shù)據(jù)傳輸?shù)木薮笮枨螅蔽鏖T子業(yè)務(wù)部門Mentor的模擬Fast-SPICE產(chǎn)品線的高級(jí)產(chǎn)品經(jīng)理Greg Curtis說(shuō)。“每天上傳的照片超過(guò)20億張。視頻大約占下游總流量的60%,尤其是當(dāng)人們?cè)诩夜ぷ鲿r(shí)。然后,這將推動(dòng)自動(dòng)駕駛汽車的發(fā)展。所有這些數(shù)據(jù)都必須從應(yīng)用程序傳輸?shù)娇梢蕴幚頂?shù)據(jù)的內(nèi)容。這必須經(jīng)過(guò)SerDes設(shè)計(jì)的發(fā)送器和接收器。該管道正在成為傳輸所有數(shù)據(jù)的瓶頸,需要更高的帶寬。”

在進(jìn)行單片集成和小芯片之間的權(quán)衡取舍之前,先了解一下SerDes電路中正在發(fā)生的架構(gòu)變化是有益的。“直到幾年前,SerDes還是相對(duì)簡(jiǎn)單的,” Silicon Creations的負(fù)責(zé)人兼聯(lián)合創(chuàng)始人Jeff Galloway說(shuō)。他們現(xiàn)在已經(jīng)發(fā)展成為高端,復(fù)雜的PAM4系統(tǒng)。PCIe rev 5及更低版本以每秒32 Gb的速度運(yùn)行,并且是兩級(jí)SerDes,而高級(jí)進(jìn)程實(shí)際上并沒(méi)有太大幫助。除了每秒32G比特外,大多數(shù)SerDes都是PAM4。這種區(qū)別在架構(gòu)上有很大的不同。“

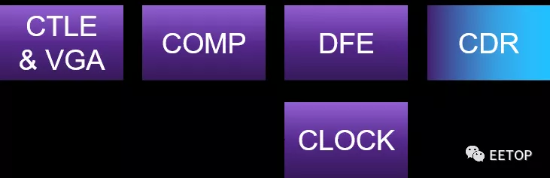

傳統(tǒng)的SerDes如圖1所示。”上一代SerDes曾經(jīng)是模擬的,您具有連續(xù)的時(shí)間線性均衡(CTLE)電路,可以放大和部分均衡信號(hào),“高速SerDes產(chǎn)品營(yíng)銷經(jīng)理Priyank Shukla解釋說(shuō)。Synopsys的IP 。”這之后是一個(gè)比較器,該比較器做出1位判決和判決反饋均衡器(DFE)。時(shí)鐘和數(shù)據(jù)恢復(fù)(CDR)也大多以模擬方式實(shí)現(xiàn)。“

圖1:SerDes的傳統(tǒng)模擬實(shí)現(xiàn)。資料來(lái)源:Synopsys

問(wèn)題是,在最新的節(jié)點(diǎn)中,模擬經(jīng)歷的變數(shù)比過(guò)去多得多。”數(shù)字設(shè)計(jì)比模擬設(shè)計(jì)更容易預(yù)測(cè)。“Mentor的Curtis說(shuō)。”設(shè)計(jì)團(tuán)隊(duì)要盡量向數(shù)字方面轉(zhuǎn)移,但仍有一些功能無(wú)法轉(zhuǎn)化。“

從16nm開(kāi)始,在速度大于56Gbps時(shí),圖2所示的架構(gòu)更有可能被使用。

圖2:混合信號(hào)SerDes框圖。資料來(lái)源:Synopsys

Synopsys的Shukla說(shuō):” SerDes接收器實(shí)質(zhì)上消除了信道損傷。“ ”其中許多現(xiàn)在可以通過(guò)數(shù)字方式完成。接收器只是有一個(gè)模數(shù)轉(zhuǎn)換器(ADC)。可以進(jìn)行時(shí)間交織以獲得更高的數(shù)據(jù)速率。之后,可以獲得數(shù)字樣本,并且可以使用DSP進(jìn)行處理,從而可以很好地?cái)U(kuò)展該技術(shù)。這包括前饋均衡器(FFE)。“

這些設(shè)計(jì)是經(jīng)過(guò)充分驗(yàn)證的。Xilinx技術(shù)市場(chǎng)經(jīng)理Martin Gilpatric表示:”我們的56G和112G收發(fā)器已經(jīng)轉(zhuǎn)向基于ADC/ dsp的接收均衡策略。“這需要大量典型的模擬電路,并將其轉(zhuǎn)換成數(shù)字邏輯。隨著PAM4以如此高的速度移動(dòng),邊際成本極低,我們能夠解決所有的問(wèn)題,并擁有一個(gè)非常強(qiáng)大的數(shù)字接收器。”

架構(gòu)的選擇和大量正在使用的過(guò)程節(jié)點(diǎn)意味著對(duì)于SerDes IP提供商來(lái)說(shuō)是好時(shí)機(jī)。SiliconCreations的Galloway說(shuō):“行業(yè)無(wú)法滿足更多需求。” “例如,TSMC正在添加22nm變體和低功耗變體。當(dāng)開(kāi)發(fā)40nm或開(kāi)發(fā)28nm時(shí),一些較舊的技術(shù)和某些較晚的PCIe標(biāo)準(zhǔn)還不成熟。PCIe 5.0即將到來(lái),我們已經(jīng)遠(yuǎn)遠(yuǎn)超過(guò)16nm。在較舊的技術(shù)上有很多設(shè)計(jì)開(kāi)始,因此基本上需要在較舊的節(jié)點(diǎn)上回填各種標(biāo)準(zhǔn)。”

新挑戰(zhàn)

較新的節(jié)點(diǎn)正在面臨挑戰(zhàn)。Galloway說(shuō):“底層晶體管不斷變得越來(lái)越小,功耗越來(lái)越低,但是互連卻越來(lái)越差。” “互連電阻和電容會(huì)給您帶來(lái)復(fù)雜的布局效果。由于存在額外的寄生效應(yīng),從而導(dǎo)致了速度限制已經(jīng)額外功耗。”

Mentor的Curtis通過(guò)數(shù)字舉例說(shuō)明:“我們的一個(gè)客戶提到,當(dāng)從40nm到5nm時(shí),互連電阻的增加,已經(jīng)上升了7倍以上。這實(shí)際上已經(jīng)限制了線材的性能,遠(yuǎn)遠(yuǎn)超過(guò)了設(shè)計(jì)。”

“GDS層的數(shù)量正在大幅增加,”Curtis補(bǔ)充道。“當(dāng)從180nm下降到5nm時(shí),這增加了9倍。其影響是設(shè)計(jì)規(guī)則檢查(DRC)的運(yùn)行時(shí)間。從180nm降到16nm finFET,運(yùn)行DRC檢查所需的時(shí)間約為10倍。然后你從16降到5,又是10倍。”

另一個(gè)因素是噪音。“與先進(jìn)工藝節(jié)點(diǎn)相關(guān)的噪聲正在成為一個(gè)重大挑戰(zhàn),”Shukla說(shuō)。“噪音是ADC的一個(gè)難題。對(duì)于選擇的結(jié)構(gòu)是逐次逼近寄存器(SAR)型ADC,這是一種模塊化的方法。需要在這個(gè)ADC的許多slices中進(jìn)行交錯(cuò)處理。對(duì)SAR的不同slices進(jìn)行對(duì)齊是有挑戰(zhàn)的,但這可以通過(guò)數(shù)字方式得到補(bǔ)償。所以無(wú)論模擬出現(xiàn)什么挑戰(zhàn),我們都有辦法彌補(bǔ)。這也是很多創(chuàng)新正在發(fā)生的地方。”

Mixel首席執(zhí)行官AshrafTakla表示:“我們知道,有一些巧妙的電路設(shè)計(jì)技術(shù)可以用于模擬設(shè)計(jì),特別是SerDes,在不影響性能的情況下繼續(xù)支持先進(jìn)技術(shù)。”例如,在使用I/O電壓的同時(shí)堆疊薄氧化物晶體管,是繼續(xù)以先進(jìn)技術(shù)設(shè)計(jì)高性能SerDes IP的一種方式。“

新晶體管可能帶來(lái)新挑戰(zhàn)。”在最新的節(jié)點(diǎn)上,如果晶體管技術(shù)切換到全能門(GAA),那么就不可能從經(jīng)濟(jì)角度出發(fā)以合理的方式集成SerDes,“高級(jí)系統(tǒng)集成與集成部門負(fù)責(zé)人Andy Heinig說(shuō)。Fraunhofer IIS自適應(yīng)系統(tǒng)工程部高效電子部門主管。”必要的SerDes面積將不斷增長(zhǎng)或被卡住,但是GAA晶體管的成本更高。僅當(dāng)使用縮放比例時(shí),GAA才有意義。從我們的角度來(lái)看,將SerDes集成到另一個(gè)芯片中的專用技術(shù)系統(tǒng)中,并以先進(jìn)的封裝技術(shù)將其與GAA芯片相結(jié)合是有意義的。“

單片集成的案例

設(shè)計(jì)團(tuán)隊(duì)面臨的一個(gè)新決策是,他們是否應(yīng)該將所有內(nèi)容都集成到單個(gè)單片芯片上還是采用多芯片異構(gòu)解決方案。這兩個(gè)選擇之間的動(dòng)態(tài)關(guān)系幾乎每天都在變化。”如今,多芯片封裝非常昂貴,“ Flex Logix首席執(zhí)行官Geoff Tate說(shuō)。”除非進(jìn)一步降低成本,否則對(duì)成本敏感的應(yīng)用將繼續(xù)青睞整體式Die。即使SerDes可能不是最佳選擇,它當(dāng)然也更便宜。“

轉(zhuǎn)到新節(jié)點(diǎn)的許多好處與PPA收益有關(guān)。”如果設(shè)計(jì)是純模擬的,那么除非電源電壓發(fā)生變化,否則從28nm到16nm再到7nm不會(huì)節(jié)省多少功耗,“ Cadence產(chǎn)品營(yíng)銷總監(jiān)Wudy Wu說(shuō)。”采用基于DSP的設(shè)計(jì),盡管仍然有很大一部分模擬電路,但40%至50%的電路是數(shù)字電路。因此,當(dāng)下降到較小的節(jié)點(diǎn)時(shí),我們可以從面積和功耗中受益。如果我們保持100%的模擬設(shè)計(jì),那么這種動(dòng)力就會(huì)減弱。“

有時(shí),由于某些特定原因,單片集成是唯一可接受的解決方案。賽靈思芯片營(yíng)銷總監(jiān)Manuel Uhm表示:”我們特別選擇了單片解決方案,因?yàn)檫@在降低延遲,降低功耗和散熱方面提供了最佳結(jié)果。“幾年前,我們率先開(kāi)發(fā)了小芯片,例如將高帶寬存儲(chǔ)器耦合到FPGA芯片或?qū)⒍鄠€(gè)FPGA芯片耦合在一起。所有這些選項(xiàng)對(duì)我們來(lái)說(shuō)都是擺在桌面上的,但是我們絕對(duì)不會(huì)離開(kāi)將SerDes集成到芯片上的想法。

小芯片案例

在數(shù)字化設(shè)計(jì)中,只需重新綜合即可將同一設(shè)計(jì)從7nm移至5nm。SerDes混合信號(hào)設(shè)計(jì),如果我們需要移植SerDes混合信號(hào)設(shè)計(jì),則需要更長(zhǎng)的時(shí)間。一個(gè)關(guān)鍵的動(dòng)機(jī)是,通過(guò)使用小芯片方法,將SerDes設(shè)計(jì)周期與核心設(shè)計(jì)周期脫鉤。

在移動(dòng)領(lǐng)域,更重要的問(wèn)題是空間,小芯片方法可以讓芯片垂直堆疊,這樣就可以在可預(yù)見(jiàn)的未來(lái)繼續(xù)集成更多的功能。對(duì)于已經(jīng)有中間件的設(shè)計(jì)來(lái)說(shuō),在電源分配是一個(gè)問(wèn)題的情況下,它提供了成本優(yōu)勢(shì)。因此,SerDes的采用者都可以通過(guò)這類方法獲得一些好處,你可以將裸片隔離開(kāi)來(lái)。”

即使采用新的SerDes架構(gòu),擴(kuò)展速度仍在放緩。Galloway說(shuō):“他們不再在面積或功率上擴(kuò)大規(guī)模。” 從一個(gè)節(jié)點(diǎn)到另一個(gè)節(jié)點(diǎn)的遷移無(wú)助于傳統(tǒng)的32Gbps及以下的SerDes。對(duì)于某些基于DSP的高級(jí)SerDes,縮放在一定程度上有所幫助,但是縮放的速度肯定不及數(shù)字邏輯的縮放速度。“

成本是許多設(shè)計(jì)的重要因素。”根據(jù)我們的經(jīng)驗(yàn),16 / 12nm是非常適合模擬設(shè)計(jì)的工藝,“ Mixel的Ashraf說(shuō)。”與28nm相比,它的Ft / Fmax高得多,而余量比5nm大。“ 我們還考慮到設(shè)計(jì)的復(fù)雜性,工作量和工具成本從16 / 12nm增加到7/6 / 5nm的情況。當(dāng)16nm速度不足以達(dá)到目標(biāo)數(shù)據(jù)速率時(shí),則需要高級(jí)節(jié)點(diǎn)。另外,我們可以看到更多的人采用小芯片。小芯片是使模擬和SerDes模塊能夠使用最合適,最便宜的處理技術(shù),同時(shí)允許數(shù)字模塊使用更高級(jí)節(jié)點(diǎn)的好方法。解決了互連標(biāo)準(zhǔn)化難題之后,我們預(yù)計(jì)小芯片將被廣泛采用。”

設(shè)計(jì)工作可能是造成成本的重要因素。“從縮放角度來(lái)看,從180nm到5nm的數(shù)字芯片面積縮放比例大于1,000倍,” Curtis說(shuō)。“從模擬縮放角度來(lái)看,它的數(shù)量級(jí)大約是10倍。與數(shù)字信號(hào)相比,模擬信號(hào)也很難描述。我并不是說(shuō)您無(wú)法描述它的特征。這更加困難,并且變量更多。這就是為什么在PVT corner分析上花費(fèi)更多時(shí)間的原因。”

結(jié)論

這其中有很多是前瞻性的思考。“裸片到裸片接口是共同設(shè)計(jì)的,今天通常由同一家公司設(shè)計(jì),”Galloway說(shuō)。“它們甚至可能是同一設(shè)計(jì)的不同實(shí)例,所以對(duì)標(biāo)準(zhǔn)化的需求較少,那里的互操作性問(wèn)題較少。我們處于起步階段,還沒(méi)有真正的標(biāo)準(zhǔn)來(lái)解決許多客戶正在嘗試做的事情。這對(duì)客戶來(lái)說(shuō)還好,但對(duì)IP的可用性有影響。”

一直以來(lái),在封裝內(nèi)或封裝外對(duì)速度的需求都在增加。Wu表示:“明顯的趨勢(shì)是聯(lián)合封裝光學(xué)器件。”目的是用光學(xué)器件代替長(zhǎng)距離的SerDes。只要看看從事這項(xiàng)工作的初創(chuàng)公司的數(shù)量即可。我不認(rèn)為61Tb交換機(jī)會(huì)采用共封裝光學(xué)器件進(jìn)行商業(yè)生產(chǎn)。可能會(huì)有一些原型,但可能會(huì)是100Tb。這是三年后的事情。光纖的走線是最大的問(wèn)題,以及如何做到量產(chǎn)。

但業(yè)界并不準(zhǔn)備在必要時(shí)放棄銅纜。“你是轉(zhuǎn)到PAM8電氣連接,還是轉(zhuǎn)到某種學(xué)片外芯片?在如何整合特定技術(shù)方面,這是一個(gè)非常完整的行業(yè)問(wèn)題。”Gilpatric說(shuō)。