2020年對Intel而言實在不是友好的一年。雖然Intel的財報仍未表現(xiàn)出大問題,但Intel在很多領(lǐng)域的前景是不樂觀的。在《2021年十大熱點應(yīng)用趨勢展望》中,我們提到了在PC處理器領(lǐng)域,“AMD將吃下‘半壁江山’”,這源自AMD Zen架構(gòu)處理器的強勢;蘋果M1的問世則為這個趨勢火上澆了一勺油;與此同時,數(shù)據(jù)中心市場顯現(xiàn)出的市場趨勢是,CPU逐漸被邊緣化,英偉達DPU在這方面顯現(xiàn)出的野心是相當顯著的。

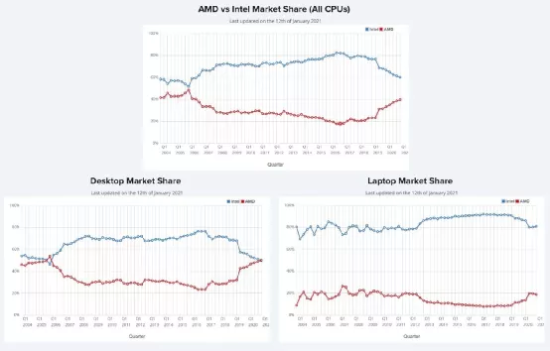

PassMark的CPU市場份額數(shù)據(jù)雖然有幸存者偏差,但在截至今年1月12日的數(shù)據(jù)更新中,AMD的桌面CPU市場份額已經(jīng)達成自2006年以來,首次對Intel的超越——當然兩者的筆記本市場份額仍然相差較大,畢竟OEM客戶是Intel的基本盤。在整個x86 CPU市場,AMD的份額總體剛剛突破了40%(PassMark)。

來源:PassMark,注意這組數(shù)據(jù)帶有明顯的幸存者偏差,僅供參考[1]

Intel十多年來,在PC處理器技術(shù)上的碾壓級優(yōu)勢,似乎在這短短2年內(nèi)便徹底喪失——不僅是Skylake這種年邁架構(gòu)表現(xiàn)的弊端,而且在10nm工藝遲遲無法大規(guī)模量產(chǎn)的情況下,7nm又雙叒叕延后了半年。

AMD Zen架構(gòu)進步在我以往的不少文章里,都有比較詳細的闡述,Zen 3已經(jīng)事實上在單核和多核性能上實現(xiàn)了對Intel處理器的全面趕超——雖然Intel的marketing仍然相當頑強。而蘋果Mac系列在拋棄Intel處理器之后,自研的M1芯片則可以說幾乎讓整個x86陣營汗顏,僅3.2GHz的主頻、低很多的功耗,就能將Intel最高端的Core i9踩在腳下,并徹底無視Intel最新的Tiger Lake(十一代酷睿)。

所以美國西部時間1月13日,英特爾宣布新任CEO Pat Gelsinger的即將上任,換下Bob Swan。事實上在此之前,Intel首席工程官Dr. Venkata (Murthy)的離職就能夠從公司管理層面,顯現(xiàn)Intel對現(xiàn)狀的反思。

本文篇幅較長,這里給出導讀,讀者可根據(jù)自己的興趣,做選擇性閱讀。

● x86處理器做大小核設(shè)計的背景

● 大小核設(shè)計的意義

● Intel的初代大小核處理器Lakefield實際表現(xiàn)

● Lakefield的小核心Tremont(可選讀)

● Lakefield的封裝技術(shù)(可選讀)

● Intel大小核處理器面臨的問題和展望

x86陣營也開始做大小核

有關(guān)M1芯片為何能達到這個程度,我會另外撰文詳述。M1的逆天表現(xiàn)雖然不是本文要談的重點,不過M1的出現(xiàn)卻已經(jīng)向市場證明,Arm在PC高性能領(lǐng)域是大有可為的,與此同時還能兼顧低功耗。從極客灣測試的數(shù)據(jù)來看,日常工作中,M1版MacBook Pro的功耗之低,與整個x86陣營都是有量級差距的:B站看個視頻,M1功耗在0.5-0.7W,而Intel Tiger Lake需要4-4.5W;待機功耗,M1達到了震驚PC處理器市場的0.02W,而Tiger Lake是1.1W。MacBook如今的續(xù)航因此可以達到20小時甚至更高。

這其實并不讓人意外,畢竟Arm平臺的大小核(big.LITTLE)設(shè)計早已是Arm芯片參與者做慣了的事。Arm過去始終在移動平臺活躍,而手機之類移動設(shè)備對功耗是非常敏感的,所以處理器采用大小核心搭配是必須的。

而x86陣營的參與者,如Intel就是自PC處理器起家的,PC對功耗更不敏感(尤其是桌面PC)。所以PC處理器也更傾向于通過提升頻率(而不是增加更多專用單元)來提升性能,自然也不存在“小核”設(shè)計。兩者功耗上的差距顯得相當順理成章。

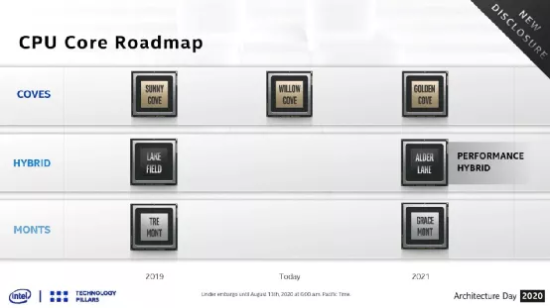

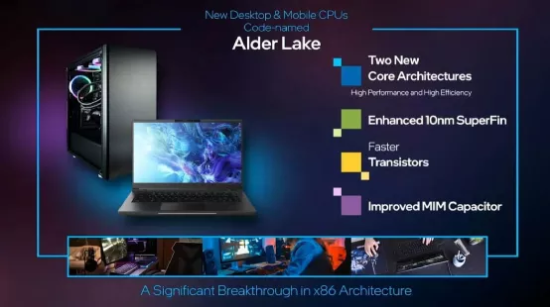

但在持續(xù)提頻的道路上,移動辦公逐漸風行的當下,Intel也一早就意識到了功耗需要有越來越高的優(yōu)先級。這兩天在美國進行的CES大會上,Intel再度提到了規(guī)劃中的“混合x86產(chǎn)品”Alder Lake,也就是x86版的大小核設(shè)計。去年Intel的Architecture Day 2020上,Intel正式宣布Alder Lake路線圖:未來的Alder Lake處理器,會將高性能計算核心(Golden Cove)與“高效率”核心(Gracemont)放到一起。

將其比作Intel版的M1芯片并不合理,畢竟Intel要做此類處理器的意愿也不是M1出現(xiàn)后才有的,不過兩者大方向總算是趨同的。Alder Lake會面向桌面和移動兩個平臺推出(這里的移動主要只是筆記本或同類設(shè)備),這顆規(guī)劃中的芯片也事實上成為x86陣營針對Arm大小核設(shè)計思路的反擊(主要是驍龍8cx和蘋果M1這類芯片)。不過在規(guī)劃上,Alder Lake需要等到今年下半年。而且Intel在這種大小核設(shè)計方案上,也還處在試探期。

在Alder Lake之前,Intel在Architecture Day 2018上展示了其初代“混合x86處理器”產(chǎn)品:Lakefield,也是將Core(酷睿)和Atom(靈動)架構(gòu)處理器核心放到一起,作為Intel版本的大小核。

如今Alder Lake相關(guān)消息仍然很少,本文嘗試以Lakefield為依據(jù),從技術(shù)角度談?wù)剎86陣營推行這種混合處理器,能否在Intel最艱難的歷史時期,幫助Intel重回PC處理器市場巔峰——以及這種“混合”“大小核”設(shè)計究竟有多大價值。

另一方面,Lakefield處理器雖然目前的出貨還非常少,而且由于規(guī)格定義并不面向高端PC(與筆記本)市場,但它幾乎可以認為濃縮了Intel當下最先進的一批技術(shù)。所以對Lakefield剖析,也能更全面地了解Intel如今在PC處理器市場的處境和底牌。

而且Lakefield不僅標志著Intel PC處理器的未來規(guī)劃,也預(yù)示了PC處理器整個市場的未來,即便它本身只是x86指令處理器的試水之作。(要知道AMD這邊到現(xiàn)在其實都還沒有自家的“小”核心設(shè)計,雖然早期架構(gòu)的改款還是可以考慮)

大小核有意義嗎?

從蘋果開始為MacBook采用M1芯片,以及微軟積極擁抱Arm推類似Surface Pro X這樣的Arm筆記本設(shè)備(和Window on Arm)就不難發(fā)現(xiàn),x86在筆記本這樣注重移動性的設(shè)備上顯得不夠高效。拋開兼容性問題不談,Surface Pro X在采用高通處理器以后,續(xù)航就遠高于x86版本的Surface;新版MacBook就更不用說了。

如前文所述,Arm的低功耗與其很早就推big.LITTLE(以及DynamiQ靈活搭配)設(shè)計是有很大關(guān)系的(更多原因我將在M1架構(gòu)分析中闡述)。這種大小核設(shè)計,在面對輕度工作負載時選擇小核心,而在需求高性能時則用大核心去跑任務(wù)。這種方案基于一個事實:兩種核心在不同的性能區(qū)間,其功耗表現(xiàn)是大不一樣的。

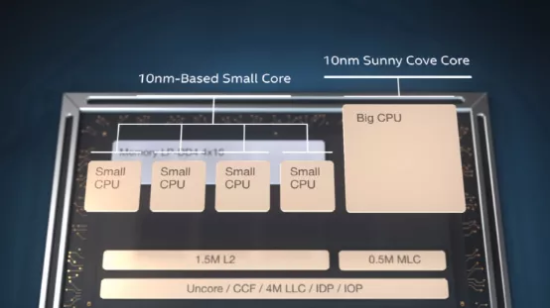

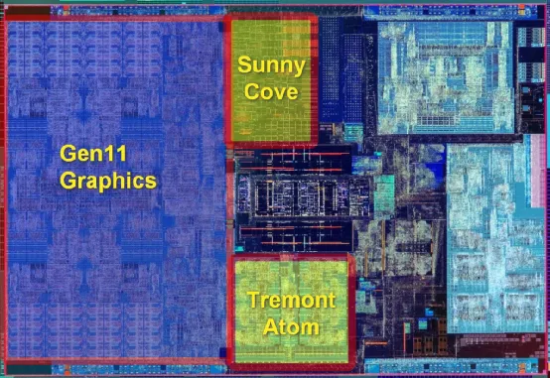

Lakefield“大小核”的整體設(shè)計大致上可以反映這個思路。Lakefield搭配的大小核分別是Sunny Cove(十代酷睿上的核心)和Tremont(最新的Atom核心),具體是1顆Sunny Cove搭配4顆Tremont。Arm陣營如今頗為常見的搭配方法是4+4,或者1+3+4/2+2+4,越來越多的手機芯片傾向于大中小三簇核心的搭配方法。

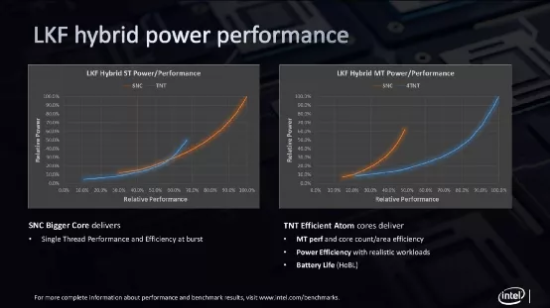

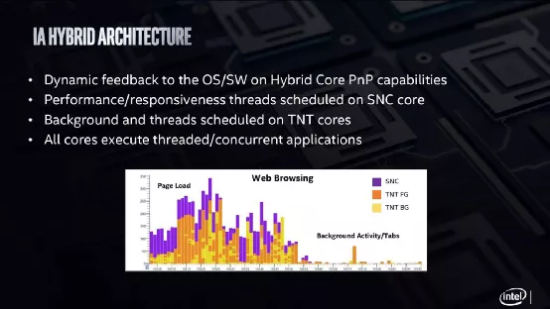

用一張圖大致能夠說明,大小核設(shè)計帶來效率提升的價值:

這張圖是Intel官方提供解釋Lakefield兩種核心,在不同性能下的功耗情況的:橫軸代表相對性能,縱軸代表相對功耗,隨性能提升,功耗也在提升。

左邊這張展示的是單線程下,兩種核心的性能與功耗關(guān)系(橙色代表Sunny Cove-SNC,藍色代表Tremont-TNT);右邊這張圖標識的則是多線程性能與功耗關(guān)系。比較顯然的一個結(jié)論是,僅看單線程情況,在較低性能狀態(tài)下,小核心能夠達成更低的功耗;但到了高性能區(qū)間,小核心的功耗反而會崩,此時大核心的效率會更好。

更具體地說,在相對性能低于58%時,Tremont核心效率高很多,而在性能高于58%時,Sunny Cove顯然是更好的選擇。當然多線程性能又是不同的,畢竟Sunny Cove核心在Lakefield中就只有一個。Intel提供的數(shù)字是,Tremont在能效上打敗Sunny Cove時,最高可以達成Sunny Cove 70%的性能;性能水平介于Sandy Bridge(2-3代酷睿)和Haswell(4代酷睿,2013-2014年)之間——整數(shù)性能與Haswell相近,同時效率會高很多。

事實上,Lakefield并不通過任務(wù)負載性能需求高低來決定用哪種核心工作。在Intel的定義中,Sunny Cove針對需要快速響應(yīng),以及與用戶體驗切身相關(guān)的線程;而Tremont則針對要求多線程性能的相關(guān)任務(wù),以及需要在較高效模式下跑的非用戶相關(guān)后臺任務(wù)。比如視頻編碼工作,通常考慮用四個Tremont核心來跑,Windows后臺任務(wù)也交由Tremont完成;類似用戶點擊開始菜單、滾動網(wǎng)頁這種操作,要求快速響應(yīng),則交給Sunny Cove。

x86初代大小核處理器的性能怎么樣?

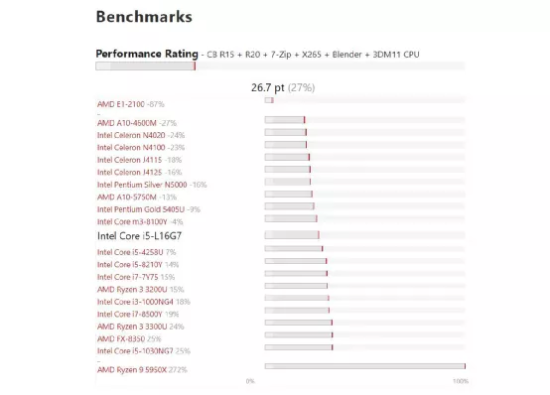

Lakefield(酷睿i5-L16G7)的其他參數(shù)還包括CPU基頻1.4GHz,大核心的最高睿頻3.0GHz(全核最高1.8GHz),不支持超線程,TDP 7W;核顯為Gen11(GT2 64EU,500MHz,頻率遠低于Ice Lake);堆疊了8GB LPDDR4-4267內(nèi)存;計算die部分的工藝為10nm。

從這些配置來看,就知Lakefield在性能表現(xiàn)上可能并不怎么樣,定位的就是低功耗便攜式或者一些二合一設(shè)備。尤其多線程工作基本全部交給Tremont去完成——這讓Lakefield在很多情況下變身Atom處理器——對不起酷睿的名頭。

即便有一顆Sunny Cove大核,也不支持超線程。另外比較重要的一點是,原本Sunny Cove是支持AVX-512指令的,但因為Tremont小核不支持,所以為了達成“混合CPU”的這種大小核設(shè)計,唯有令兩者對支持的指令完全達成一致,所以Sunny Cove也就閹割了對AVX-512指令的支持,另外閹割的還包括了AVX、AVX2,以及Tremont小核心的GFNI、ENCLV、CLDEMOTE等指令。

像這樣異構(gòu)核心方案,在指令方面需要滿足木桶最低板的原則(或者跨所有核心的ISA兼容性),在Arm世界也同樣適用。否則線程在大小核之間遷移時就會出問題。所以Cortex-A55作為Arm處理器的小核心被用了這么多年不動搖,也是這個道理。

來源:AnandTech[2],四顆Tremont核心簇的面積和一顆Sunny Cove相差無幾

無論AnandTech還是WikiChip,都認為從Lakefield的die shot來看,Sunny Cove核心部分的AVX-512相關(guān)的單元并未被實際移除,雖然Intel宣稱是“移除”了的。

Intel宣傳的數(shù)字是,相比Amber Lake i7-8500Y(Intel的超低壓處理器,TDP 5W),Lakefield的多線程性能高24%,單線程則快12%,圖形性能提升70%——這些變化實則都在預(yù)期內(nèi)。以及有大核心的加持,web性能高出33%,效率提升17%——這一點對比的顯然就是單純的四核Atom了。可預(yù)期的是看B站會比以前省電……

另外比較重要的是每瓦性能提升24%(相比Amber Lake),待機功耗“大幅降低”,達到2.5mW左右——這就和前文列出M1的待機功耗數(shù)字差不多了。達成最高的效率原本就是這種設(shè)計的重要目的。蘋果在發(fā)布會上最愛談的就是每瓦性能以表現(xiàn)芯片的高效率。在Architecture Day 2020上,Intel就宣稱Alder Lake將能夠達成Intel有史以來最高每瓦性能——當然這是Lakefield后續(xù)產(chǎn)品了,也是Intel的預(yù)期。

當前針對Lakefield尚無十分系統(tǒng)的性能測試。已經(jīng)上市的Lakefield產(chǎn)品主要包括了聯(lián)想ThinkPad X1 Fold、三星Galaxy Book S以及微軟Surface Book Neo。NotebookCheck的實測數(shù)據(jù)是,Lakefield(i5-L16G7)綜合性能(也包括了核顯性能)弱于超低壓的酷睿i5-8210Y和四代酷睿42 85U。

來源:NotebookCheck[3]

這個數(shù)據(jù)可能并不是很合理,一方面在于NotebookCheck用于跑分測試的Cinebench版本(R15與R20)在多線程性能測試中甚至都無法用上Lakefield的Sunny Cove大核(但卻的確能反映其實際使用情況,因為如前文所述,Lakefield中的Sunny Cove并不像很多人理解的那樣,是簡單用于“高負載”任務(wù)),另一方面和OEM廠商的具體實施方案有關(guān)。

Cinebench R23似乎是目前唯一能夠?qū)崿F(xiàn)5核全開的測試,但網(wǎng)上找不到R23的Lakefield跑分。總之Lakefield大致上也就用來做word或者ppt文檔以及看看網(wǎng)頁和愛奇藝了。

有關(guān)Tremont小核心(選讀)

很多同學抱怨我文章寫太長,所以更全面的微架構(gòu)分析文章,后續(xù)我會發(fā)到我的面包板專欄,感興趣的同學可以前往關(guān)注。本文我只簡單聊聊Lakefield中的小核心Tremont,畢竟大核心的Sunny Cove其實算是非常知名了,Intel十代酷睿的Ice Lake用的就是這個核心。而且Lakefield也實在談不上“高性能”,它本身更重在“低功耗”上。

Tremont相比前代(Goldmont Plus,2017年)主要是提升單線程性能,IPC有超過30%的提升。作為Atom處理器中的一款產(chǎn)品,它重在考量每核功耗與每核面積。所以前文給出的die shot就能看出,Lakefield中的Tremont四核心簇整體尺寸才相當于一個Sunny Cove。

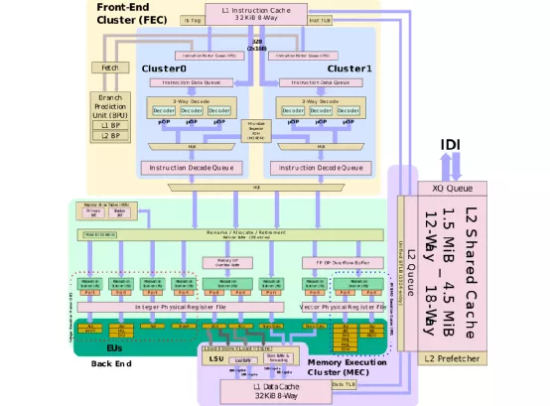

來源:WikiChip[4]

從“小”核心的角度來說,Tremont與知名的Arm Cortex-A55小核心并不是一個量級。Tremont首先是個亂序核心,前端解碼寬度6-wide(雖然是分兩組),這就決定了它比A55這樣的選手還是壯實多了。這一點和蘋果的思路就很像(2019年蘋果A12的Tempest小核心,在性能上幾乎達到了Cortex-A72的程度)。

其余具體的微架構(gòu)可參見上圖,包括allocation 4-wide,re-order buffer增加至208條(+119%),后端有10個執(zhí)行端口,雙load/store管線;L2 cache最高可配置4.5MB,L1-D cache增加33%,L2 TLB(頁表緩存)增加到1024-entry;另外還有新指令引入——不過對Lakefield而言,這一點就不存在了,前文已經(jīng)提到。感覺整體看起來,這都不像是個“小”核心。

其最大的變化在前端,包括分支預(yù)測單元升級——接近于“大”核心級別的精度(兩級結(jié)構(gòu));以及最重要的解碼寬度變化。不過這個所謂的“6-wide”寬度并不是類似酷睿5-wide那類方案(1個復(fù)雜decoder,4個簡單decoder,再加μop cache),實際上是兩組3-way對稱解碼。每一組都有自己的指令流。配合分支預(yù)測器,預(yù)測指令流可以進第二組(上圖的Cluster 1),不打斷第一組(Cluster 0)的工作,兩組并行預(yù)測、讀取、解碼。

這種實際上的3-wide設(shè)計,相比真正的6-wide解碼要節(jié)省面積和功耗,沒有μop cache。Intel宣稱這種設(shè)計能夠平衡資源。Tremont也支持僅開其中一組的模式,預(yù)期實現(xiàn)更低的每核峰值功耗。更多包括re-order buffer加深、執(zhí)行引擎和存儲子系統(tǒng)拓寬等,本文皆不再贅述。還有一些額外的特性,比如RDT技術(shù)支持,可實現(xiàn)帶寬分配、QoS、優(yōu)先級之類的操作(服務(wù)器芯片中常見);Speed Shift技術(shù);信任安全啟動;內(nèi)存加密等。

當大小核遇上3D封裝(選讀)

拋開更微觀的層面不談,Lakefield整體看來還是比較草率的,包括1+4的這種組合方式,及其表現(xiàn)出的實際性能。Lakefield之所以沒有加入更多的Sunny Cove大核心,很大程度應(yīng)該也是受限于Sunny Cove核心的體積和功耗。以Lakefield如今計算die占據(jù)的82mm?來看,及其預(yù)定義的尺寸,它很難再塞入更多CPU核心,何況Sunny Cove的功耗也實在不算低。

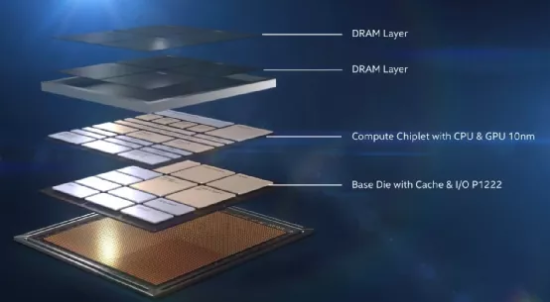

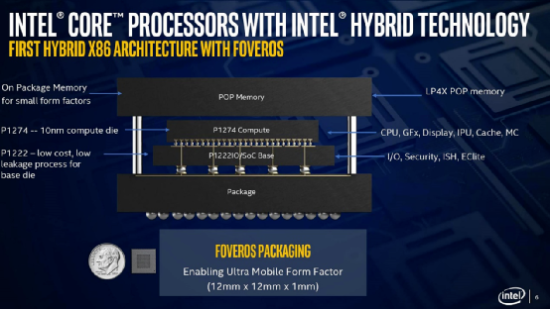

所以我們才說,Lakefield很像Intel針對“混合”或者大小核設(shè)計的一個試水,和打怪升級的必經(jīng)之路。而作為一款實驗性質(zhì)的作品,Lakefield不僅有Intel最新的大小核,而且在封裝上也算是集Intel芯片制造廠的大成了。它用上了傳說中的Foveros 3D芯片堆疊技術(shù),也是Intel首款采用這種封裝方案的芯片。

前面談的這些CPU大小核、GPU等都是Lakefield的計算die(計算die上另外還包括了圖像處理單元IPU、LPDDR4X內(nèi)存控制器、Gen11 Display engines等),采用的是Intel的10nm工藝(與Ice Lake一致,理論上屬于Intel的二代10nm工藝);有關(guān)Intel 10nm工藝本文不再詳述,詳情參見我的面包板專欄文章。

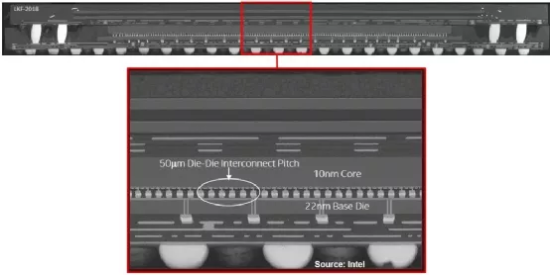

而在計算die之下,還有個base die。下面的這片base die主要是處理器外設(shè)的active interposer(主動中介層)。Active interposer相比傳統(tǒng)passive interposer,不只是用于連接的中介層,本身也發(fā)揮功能邏輯的作用,其上包含各種PCIe 3.0、各種I/O控制、音頻codec、安全等。Base die所用的制造工藝是22FFL——22FFL并不是早期的22nm工藝,而是14nm的功耗優(yōu)化版(更稀疏的版本),針對的就是更高效的IO。22FFL則必然又在成本上顯著低于10nm了,這也屬于典型的chiplet設(shè)計和制造思路。

計算die和base die之間采用50μm間距bump的die-to-die互聯(lián)(Foveros Die to Die Interface),承載信號(數(shù)據(jù))和供電的連接。這種互聯(lián)應(yīng)該是3D堆疊方案上的絕對難點。Intel宣稱其最大傳輸速率是500MT/s(mega-transfers per second),而且每bit數(shù)據(jù)傳輸耗能0.2pJ(皮焦)。0.2pJ在die間數(shù)據(jù)傳輸?shù)暮哪芰考壣峡梢哉J為是非常小的,這應(yīng)該也是實現(xiàn)低功耗的一部分。

值得一提的是,IO部分Lakefield僅給到了PCIe 3.0六條通道支持,這就決定了其IO連接會相當捉襟見肘。ThinkPad X1 Fold為Lakefield配套的SSD,僅拿到PCIe 3.0 x2的通道,帶寬因此大受限制;配獨立GPU什么的,那也是想都不用想的了。[5]從這樣的小細節(jié)也能看出Lakefield試水的本質(zhì)。

最后在Lakefield整個封裝的最上層是內(nèi)存(Package on Package),有4GB和8GB兩種規(guī)格可選,應(yīng)該是來自其他內(nèi)存制造商的定制方案。值得一提的是,內(nèi)存與中間的計算die之間并沒有采用什么黑科技連接方式,與CPU的通訊是需要經(jīng)由最底層的package轉(zhuǎn)道再經(jīng)過base die之后,再到compute die的。它也沒有M1芯片那樣的Unified Memory Architecture特性。

這樣的堆疊方案下,散熱會成為一個大問題,Intel為此似乎還是頗費了一番功夫的,不過現(xiàn)階段主要在不同IP模塊的設(shè)計上做到減少局部的高溫聚集點、互聯(lián)金屬層厚度控制等,所以散熱在設(shè)計上有更高的優(yōu)先級;另外Intel還探討過在兩個die之間采用“流體通道(fluidic channes)”的可行性——這就屬于未來的方向了。有關(guān)Lakefield封裝細節(jié),AnandTech的文章中有比較詳細的闡述[2],我也會在面包板專欄再行刊文。

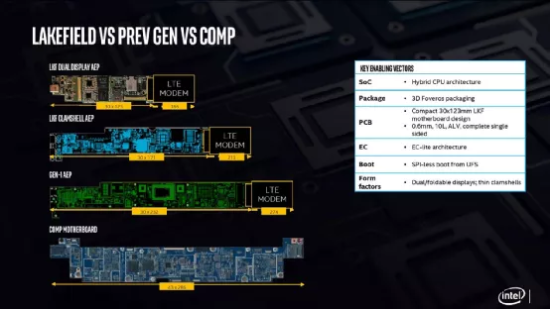

經(jīng)過這種Foveros 3D堆疊后,Lakefield芯片整體達成了12x12x1mm的三圍尺寸。板級設(shè)計也就可以更為緊湊,相比之前的低功耗CPU實施方案,主板可以減少60%的尺寸。加上LTE modem的話,整體主板尺寸總算是可以和高通的設(shè)計比一比了。

Lakefield真的能成嗎?

最后來稍稍總結(jié)一下Intel在Lakefield處理器上現(xiàn)存的問題。首先Lakefield基本上是很難獲得市場大范圍的肯定的,即便它塞入了Intel這么多最尖端的研究成果。不過Lakefield作為Intel首款涉足大小核設(shè)計的處理器產(chǎn)品,其積累經(jīng)驗的作用也明顯大于市場本身。下一代的Alder Lake才是值得觀察的關(guān)鍵。

所以這個問題應(yīng)當換成Intel的大小核設(shè)計能成嗎?

事實上Intel在這種非其傳統(tǒng)強項的處理器產(chǎn)品中,遭遇的問題可能是形形色色的。從具體到抽象總結(jié)這種處理器“能成嗎”的關(guān)鍵:

其一是scheduler(調(diào)度)。Intel此前并沒有設(shè)計大小核處理器的經(jīng)驗,Windows也始終不曾有不同類型的核心間做線程(進程)遷移的scheduler(微軟和高通勾搭上之后,必然有密切合作在不同CPU設(shè)計間管理負載的scheduler,但至少x86是沒有的;不過從Wikichip的介紹來看,Intel似乎也提交過非一致指令集的異構(gòu)核心一起工作,針對操作系統(tǒng)的算法和加強[6][7])。要知道Android和Arm在這方面可是有著比較長期的演進的,包括線程遷移對實際體驗造成的影響;蘋果就更不用說了。

Cinebench更早版本在做Lakefield多核性能測試時,并不會啟用Sunny Cove大核可能就能說明一些問題(但AnandTech猜測這可能是功耗或者熱聚集考量所致)。

傳言未來的Alder Lake預(yù)計會包含8+8的設(shè)計,這其中的線程調(diào)度就不只是Intel如今列出、如上圖這樣Lakefield簡單的網(wǎng)頁瀏覽場景了。那將更考驗Intel的功力。

第二是處理器本身的性能。Lakefield宣傳中似乎的確有著不錯的功耗表現(xiàn),但性能實在是不大夠看。這應(yīng)該并不是什么大問題,一方面在于Lakefield本身就不定位在高性能,另一方面則是這款產(chǎn)品試水和積累經(jīng)驗的成分居多。在Architecture Day 2020之上,Raja Koduri表示Intel從Lakefield身上學到了很多東西,Alder Lake未來會聚焦到性能上。

終極問題大概是,在性能和效率上Intel能否做到蘋果M1那樣的程度。M1芯片表現(xiàn)出的性能和效率,我個人看來是基于三個要素共同構(gòu)成的:其一是超寬的處理器架構(gòu),其二是有針對性地添加一些專用單元,其三則是對自家封閉生態(tài)超乎尋常的掌控力(令其能夠很隨意地做出同一內(nèi)存架構(gòu)這樣的東西)。

這將在未來M1的文章中做詳述。這三要素可認為是僅有蘋果這種掌控從芯片設(shè)計到開發(fā)生態(tài),到消費終端產(chǎn)品銷售全環(huán)節(jié)的企業(yè)才有的資源。比如前兩者,超寬處理器架構(gòu)和專用單元是需要以die面積(即成本)為代價的,蘋果可以這么玩是基于其終端產(chǎn)品的高利潤與高銷量;對于Intel、高通這種單純賺取處理器利潤的廠商,這種玩法非常不經(jīng)濟(x86還存在變長指令不利于解碼寬度拓寬這樣的現(xiàn)實問題)。要達到M1的性能水平不難,但效率就沒那么簡單了。

還有其他的一些妥協(xié),比如說前文提到的為實現(xiàn)指令的對稱性,Lakefield不支持AVX指令——這原本可是Sunny Cove主打的升級特性;再比如3D堆疊的兩層die分別用了兩個PMIC(電源管理IC)。這些其實都表明Lakefield的不成熟,不過這些問題未來都有解決的辦法。

最后更抽象的是,是Intel的速度問題。這里的速度是指Intel行事與決策的響應(yīng)速度。不說Skylake縫縫補補新三年舊三年,最典型的是芯片制造工藝已經(jīng)落后于臺積電,且可預(yù)期的未來,行進速度還將非常緩慢。比如下半年大小核處理器Alder Lake要用上10nm Enhanced SuperFin(應(yīng)該是第四代10nm工藝),這還是預(yù)期中的。屆時的市場格局或許都不好說了,以及7nm工藝遙遙無期(最早一批7nm要等到2022年下半年或2023年上半年)。

若以多年前Intel在PC處理器市場的地位,這些問題或許都不足多慮。AMD推土機推了那么多年,蘋果也還偏安在iPhone上,Intel有的是時間;但在如今這般光景下,情況就相當不樂觀了。

好在2021年下半年也還不算遙遠。Intel即將上任的CEO Pat Gelsinger也有多年技術(shù)背景,這預(yù)計也會加快Intel技術(shù)推進速度,這正是目前Intel最需要的。Intel在去年的ISA Extensions Reference手冊上確認,Alder Lake還將加入新指令支持[8],包括LBR、HLAT、SERIALIZE,其中LBR可用于分支提速,對性能還有價值。從多方面來看,傳說中擁有最高每瓦性能表現(xiàn)的Alder Lake都成為Intel規(guī)劃的產(chǎn)品線中讓人最為期待的處理器,并且真正讓我們看到Intel在大小核設(shè)計上的實力。