圖片在上周周的ISSCC 2021上,六家主要的3D NAND閃存制造商中的四家展示了他們最新的3D NAND技術(shù)。其中三星、SK hynix和Kioxia(+ Western Digital)分享了其最新的3D TLC NAND設(shè)計(jì),而英特爾則展示了其144層3D QLC NAND。美光公司和長(zhǎng)江存儲(chǔ)今年沒(méi)有參加分享。

3D TLC(每個(gè)cell有3位)更新

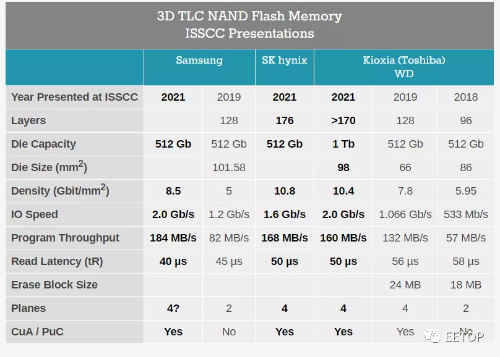

三星、SK hynix和Kioxia / WD介紹了有關(guān)其下一代3D TLC的信息。美光的176L TLC未在此處顯示,因?yàn)樗麄兩形瘁槍?duì)最新一代的3D NAND發(fā)布大部分?jǐn)?shù)據(jù)。

不出所料,看起來(lái)三星很可能再次在性能上處于領(lǐng)先地位,讀取延遲最低、寫(xiě)入速度最快。然而,他們的位密度仍然明顯滯后,即使他們宣稱這一代的位密度躍升了70%。在過(guò)去,它們的密度滯后并不像乍一看那樣是個(gè)缺點(diǎn),因?yàn)槿悄軌虮苊馐褂么B,可以將128層的堆棧作為單層制造,而他們的競(jìng)爭(zhēng)對(duì)手都不得不將堆棧分成兩層,增加了所需的晶圓廠步驟。這可能是三星不可避免地采用串疊的一代,但如果是這樣的話,那么他們揮之不去的密度劣勢(shì)就相當(dāng)令人失望了。另一方面,如果他們成功地將這一轉(zhuǎn)變?cè)偻七t一代,并且僅使用其他技術(shù)的組合(最顯著的是CMOS underArray layout)就實(shí)現(xiàn)了這種密度的提高,那么這是一個(gè)非常令人印象深刻的進(jìn)步,并且可以肯定地說(shuō),在涉及到垂直通道的高寬比蝕刻時(shí),三星已經(jīng)領(lǐng)先競(jìng)爭(zhēng)對(duì)手好幾年了,而垂直通道的高寬比蝕刻是擴(kuò)展3D NAND的最關(guān)鍵的制造步驟。一旦三星披露實(shí)際的層數(shù),我們就會(huì)知道更多,但他們暫時(shí)仍在保密,這暗示著他們并不希望吹噓最高的層數(shù)。

SK hynix和Kioxia / WD所描述的TLC部件看起來(lái)相當(dāng)相似,但區(qū)別在于SK hynix的是512Gb芯片,而Kioxia的容量為1Tb芯片。盡管Kioxia吹捧更高的NAND接口速度,但兩種設(shè)計(jì)都具有相似的性能和密度。Kioxia和Western Digital發(fā)布了一個(gè)新聞稿,宣布了162層3D NAND,因此它們的總層數(shù)落后于SK hynix和Micron。該新聞稿還提到,其cell陣列的水平密度提高了10%,因此Kioxia和Western Digital可能將垂直通道比任何競(jìng)爭(zhēng)對(duì)手都更緊密地排列在一起。

3D QLC(每個(gè)cell有4位)更新

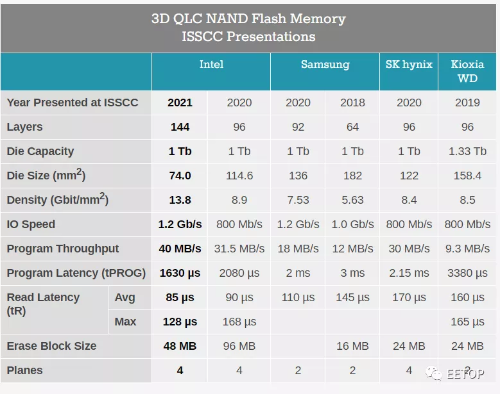

今年唯一在ISSCC上進(jìn)行QLC更新的公司是英特爾。

總的來(lái)說(shuō),英特爾比其他任何競(jìng)爭(zhēng)對(duì)手都更加注重QLC NAND。這款144L QLC是英特爾沒(méi)有與美光科技共同開(kāi)發(fā)的第一代3D NAND,在某些方面它是獨(dú)一無(wú)二的。英特爾將其3D NAND技術(shù)帶向與其他行業(yè)不同的方向,因?yàn)樗鼈儗AND閃存業(yè)務(wù)出售給SK hynix的協(xié)議將產(chǎn)生有趣的影響,但是在短期內(nèi),英特爾似乎正在獲得他們想要的NAND。因?yàn)閮H有144層,英特爾幾乎可以肯定現(xiàn)在是層數(shù)的落后者。與9X層的QLC相比,英特爾具有更好的性能和密度-但是SK hynix和Kioxia描述的新型TLC的QLC版本應(yīng)具有可比的密度。英特爾已經(jīng)放棄使用96L QLC的方式來(lái)描述塊大小,但144層NAND的48MB塊尺寸看起來(lái)也很大。

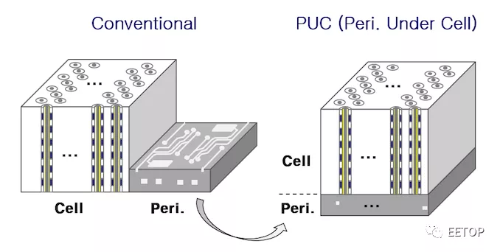

不同廠商的CuA(CMOS-under-array)

英特爾和美光的合資企業(yè)現(xiàn)已解散,是繼三星之后第二家轉(zhuǎn)向3D NAND閃存制造商。英特爾/美光3D NAND帶給業(yè)界的最重大創(chuàng)新是CMOS Under the Array(CuA)設(shè)計(jì)。這項(xiàng)技術(shù)可以將大多數(shù)NAND芯片的外圍電路(頁(yè)面緩沖器、讀取放大器、電荷泵等)置于存儲(chǔ)單元的垂直堆棧之下,而不是并排放置。

這種改變節(jié)省了大量的裸片空間,并允許將超過(guò)90%的裸片面積用于存儲(chǔ)單元陣列。SK hynix是下一個(gè)做出這種改變的廠商,他們稱之為“Periphery under Cell”(PuC)。其余廠商現(xiàn)在也都加入了這一行列。Kioxia(當(dāng)時(shí)的東芝)和西數(shù)在ISSCC 2019上展示了128層的CuA設(shè)計(jì),但他們的第五代BiCS 3D NAND最終以112L設(shè)計(jì)投產(chǎn),沒(méi)有CuA。他們今年的ISSCC展示的是 “170+”層的CuA設(shè)計(jì),他們已經(jīng)發(fā)布了新聞稿,確認(rèn)他們的第六代BiCS 3D NAND將是162層的CuA設(shè)計(jì)。

除了節(jié)省裸片空間,3D NAND的CuA/PuC的設(shè)計(jì)風(fēng)格還允許裸片包含更多的外圍電路,這樣做的成本效益比更高。這使得將裸片的存儲(chǔ)器陣列劃分為更多獨(dú)立的平面,每個(gè)平面都有自己的大部分外圍電路副本。大多數(shù)沒(méi)有采用CuA布局的3D NAND都是每個(gè)裸片只使用兩個(gè)平面,但現(xiàn)在大家都在使用CuA,標(biāo)準(zhǔn)是每個(gè)裸片使用四個(gè)平面。這提供了額外的并行性,提高了每顆晶粒的性能,并抵消了通常因使用較少晶粒達(dá)到相同總?cè)萘慷鴮?dǎo)致的SSD整體性能下降。

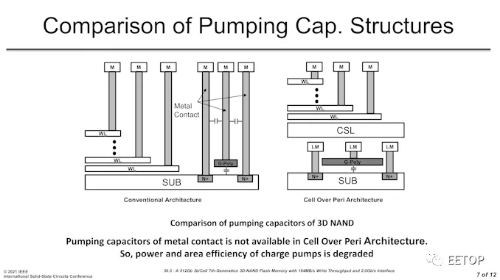

CuA結(jié)構(gòu)并非沒(méi)有挑戰(zhàn)和缺點(diǎn)。當(dāng)制造商首次切換到CuA時(shí),它們會(huì)大大增加外圍電路的可用裸片空間。但是在那之后,每一代相繼增加的層數(shù)意味著管理相同數(shù)量存儲(chǔ)單元的die空間就更少了,因此外圍電路仍然必須縮小。將外圍電路置于存儲(chǔ)單元陣列之下還會(huì)帶來(lái)新的限制。例如,三星在今年的ISSCC演講中提到,當(dāng)電荷泵不再能夠使用易于包含在3D NAND堆棧中的高金屬結(jié)構(gòu)時(shí),這就為電荷泵構(gòu)造大型電容器帶來(lái)挑戰(zhàn)。

更好的On-Die Parallelism:每個(gè)die四個(gè)平面

將NAND閃存管die分為四個(gè)平面可以使該die并行處理更多的操作,但是并不能使其表現(xiàn)得像四個(gè)獨(dú)立的die。因?yàn)椴⑿袌?zhí)行操作受到限制:例如,同時(shí)寫(xiě)入仍必須在每個(gè)平面內(nèi)的同一字線上進(jìn)行。但是隨著閃存芯片數(shù)量的增加,制造商一直在努力放松一些限制。在過(guò)去的幾年中,制造商推出了“獨(dú)立”的多平面讀取,這意味著在不同平面中的同時(shí)讀取對(duì)每個(gè)平面內(nèi)的讀取位置沒(méi)有任何限制,這是隨機(jī)讀取吞吐量的一大勝利。

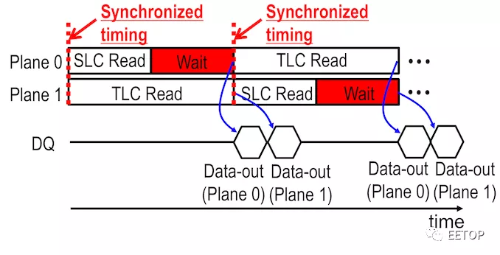

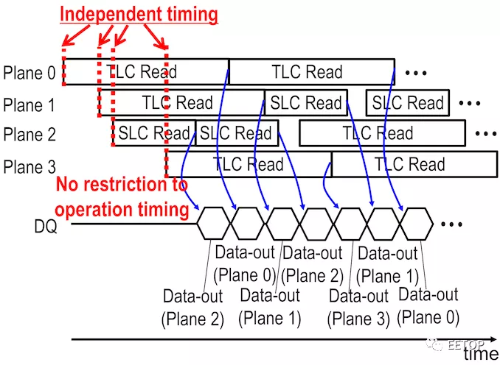

圖片現(xiàn)在,放寬了對(duì)多平面操作的另一個(gè)限制:不需要在不同平面上進(jìn)行讀取操作的時(shí)序。這使得一個(gè)平面可以從SLC頁(yè)面執(zhí)行多次讀取,而另一平面則可以從TLC或QLC頁(yè)面執(zhí)行單個(gè)較慢的讀取。此功能稱為異步獨(dú)立(多)平面讀取。實(shí)際效果是,對(duì)于讀取操作,一個(gè)大的4平面die現(xiàn)在可以匹配四個(gè)較小的1平面die的性能。這可以緩解更高的每個(gè)芯片容量給每個(gè)通道僅具有一個(gè)或兩個(gè)芯片的SSD帶來(lái)的性能下降。

圖片Kioxia和WD報(bào)告說(shuō),要實(shí)現(xiàn)此功能,他們必須停止在平面之間共享電荷泵,以免因讀取操作不同步而導(dǎo)致電壓和電流波動(dòng)不及時(shí)。英特爾還通過(guò)其4平面144L QLC達(dá)到了此功能的一半:將多個(gè)平面配對(duì)為多個(gè)平面組,每個(gè)平面組可以執(zhí)行讀取而無(wú)需與另一個(gè)平面組中的讀取時(shí)序保持一致。

NAND IO加快了對(duì)SSD控制器的支持速度

ISSCC上介紹的新型TLC NAND部件支持NAND閃存die和SSD控制器之間的通信的IO速度范圍為1.6到2.0 Gb / s。目前市場(chǎng)上最快的NAND SSD的運(yùn)行速度為1.2-1.4Gb / s。NAND制造商可以通過(guò)確保將用于其SSD的自己的SSD控制器設(shè)計(jì)準(zhǔn)備好支持這些更高的IO速度而從垂直集成中受益,但是可能會(huì)依賴其他第三方控制器的SSD供應(yīng)商。Phison針對(duì)高端PCIe 4.0 SSD的最新E18 8通道控制器僅支持1.2Gb / s IO速度,而即將推出的E21T 4通道NVMe控制器則支持1.6Gb / s。Silicon Motion的8通道SM2264和4通道SM2267分別支持1.6Gb / s和1.2Gb / s IO速度。

由于以1.2Gb / s的速度運(yùn)行8個(gè)通道已經(jīng)足以使SSD飽和PCIe 4.0 x4連接,因此這些新的更高IO速度在PCIe 5.0到來(lái)之前對(duì)高端SSD并沒(méi)有多大用處。但是,價(jià)格更實(shí)惠的4通道消費(fèi)類SSD控制器將能夠使用這些更高的速度更好地進(jìn)入PCIe 4.0性能領(lǐng)域,達(dá)到或超過(guò)第一個(gè)PCIe 4.0 SSD控制器(Phison E16,8ch @ 800Mb / s)提供的吞吐量。正如諸如SK hynix GoldP31之類的驅(qū)動(dòng)器所展示的那樣,在每個(gè)通道上支持高IO速度的高級(jí)4通道控制器在性能上極具競(jìng)爭(zhēng)力,同時(shí)以比8通道控制器更高的功率效率運(yùn)行。

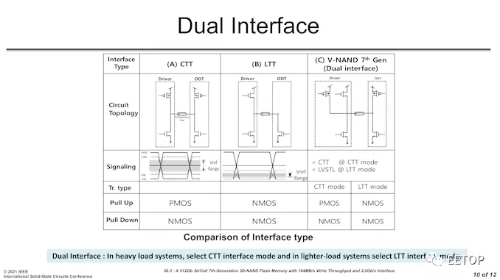

要達(dá)到這些更高的IO速度,就需要對(duì)NAND裸片上的接口邏輯進(jìn)行重大升級(jí),并且正如我們?cè)谄渌咚俳涌冢ㄈ鏟CI Express)中所看到的那樣,增加的功耗是一個(gè)主要問(wèn)題。三星正在通過(guò)使用雙模式驅(qū)動(dòng)程序和終端解決此問(wèn)題。當(dāng)由于總線上的更多負(fù)載而需要更高的驅(qū)動(dòng)強(qiáng)度時(shí)(每個(gè)通道有更多的裸片),將使用PMOS晶體管進(jìn)行上拉,否則,他們可以使用NMOS晶體管并降低驅(qū)動(dòng)器的功耗一半以上。這為三星提供了一個(gè)單一的接口設(shè)計(jì),該設(shè)計(jì)可以很好地適用于小型消費(fèi)類SSD和大型企業(yè)驅(qū)動(dòng)器,每個(gè)通道具有更多的裸片。(過(guò)去,三星已經(jīng)在多芯片封裝中添加了單獨(dú)的重定時(shí)器芯片,這些芯片在相同的一個(gè)或兩個(gè)通道上將許多NAND芯片堆疊在一起。

串堆疊:首款三層串堆疊NAND

串堆疊已被視為將3D NAND擴(kuò)展到更高層數(shù)的必要手段。只有三星能夠一次構(gòu)建超過(guò)100層的3D NAND,并且其他所有人早就轉(zhuǎn)而使用堆疊兩個(gè)具有更合理層數(shù)的decks了。這意味著例如美光公司的176層3D NAND構(gòu)建為88層存儲(chǔ)單元,然后在其頂部再構(gòu)建88層。與一次完成所有層相比,這會(huì)增加成本,并且需要在平臺(tái)之間的接口處仔細(xì)對(duì)齊。但是另一種選擇是使垂直通道更寬,以使縱橫比(寬度與深度)保持在當(dāng)前晶圓廠技術(shù)可以蝕刻的范圍之內(nèi)。

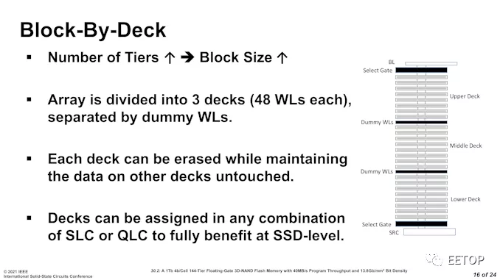

英特爾的144L QLC設(shè)計(jì)最令人驚訝的是它們已經(jīng)轉(zhuǎn)向了3層堆棧:48 + 48 + 48層,而不是我們期望的72 + 72。由于他們的前一代產(chǎn)品是48 + 48層(總共96L)設(shè)計(jì),因此,除了第三次重復(fù)相同的沉積,蝕刻和填充步驟順序外,他們對(duì)于存儲(chǔ)器陣列本身的制造方式幾乎沒(méi)有什么改變。英特爾通過(guò)這種方法影響了工廠的吞吐量,但它可能有助于他們更好地控制從堆棧頂部到底部的通道和單元尺寸的變化,考慮到他們對(duì)QLC及其獨(dú)特性的關(guān)注,這可能是一個(gè)更大的問(wèn)題。決定仍然使用浮柵存儲(chǔ)單元,而不是像其他所有人一樣切換到電荷陷阱單元。

為了與這種三層結(jié)構(gòu)配合使用,英特爾重新組織了它們處理擦除塊的方式,現(xiàn)在三個(gè)平臺(tái)中的每一個(gè)都構(gòu)成了一個(gè)單獨(dú)的擦除塊集合。這意味著現(xiàn)在可以擦除144L字符串的中間三分之一,而不會(huì)干擾存儲(chǔ)在該字符串的其他三分之二中的數(shù)據(jù)。英特爾還可以通過(guò)96L QLC將數(shù)據(jù)塊按卡組劃分,從而將96 MB的數(shù)據(jù)塊大小減小到不太極端的48 MB數(shù)據(jù)塊大小。