最近的一則新聞把一個(gè)原本在學(xué)術(shù)界的詞匯——“后摩爾”拉升到了公眾視野。什么是“后摩爾”?為什么“后摩爾”要提升到國家戰(zhàn)略程度?“后摩爾”技術(shù)包含哪些?本期矽說小編就來談一談我眼中的后摩爾,因?yàn)橐恢鼻分蠹乙黄?a class="innerlink" href="http://forexkbc.com/tags/ISSCC" target="_blank">ISSCC 2021的review,正好有機(jī)會(huì)借著這個(gè)話題來一起討論下。

先插一個(gè)硬廣:第三屆華人芯片設(shè)計(jì)技術(shù)研討會(huì)(ICAC 2021)明天就要在深圳開幕了,屆時(shí)將網(wǎng)羅今年在ISSCC 2021上發(fā)表論文的大部分作者與報(bào)告,不出國門、不倒時(shí)差的ISSCC體驗(yàn)就在5.20,千萬不要錯(cuò)過。

接下來開始正文——

后摩爾定義:尺寸微縮的邊際效應(yīng)遞減

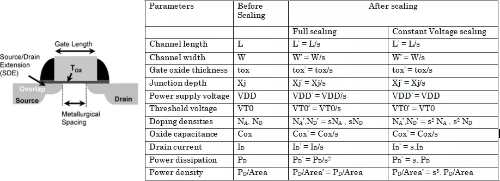

歷史上的摩爾定律,一般分為兩個(gè)階段,第一個(gè)階段是從Gordon Moore提出摩爾定律開始,到2000年前后,這個(gè)階段一般稱為 Full Scaling或者恒定電場微縮階段,這個(gè)階段的摩爾定律是溫馨且甜蜜的童話,所有的性能指標(biāo)都微縮,單位面積上的發(fā)熱量保持不變。PPA(Power/Performance/Area),無論哪個(gè)都在有條不紊提升。也正是這個(gè)時(shí)期開始,芯片廠商們意識到,押注摩爾定律穩(wěn)賺不賠,就像投資北上廣深的房價(jià)。

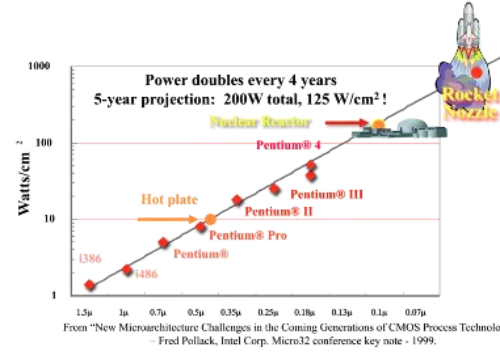

然而好景不長,由于晶體管的閾值電壓在到100nm以后幾乎無法下降,F(xiàn)ull scale的摩爾定律遇到了阻礙。于是一種新的摩爾定律產(chǎn)生——我們一般稱為恒定電壓微縮。雖然尺寸還在變小,速度還在變快,但是恒定電壓微縮下,單位面積下的發(fā)熱量是隨微縮節(jié)點(diǎn)平方率上升。換言之,這樣的摩爾定律一定帶來芯片發(fā)熱的爆炸。如果我們芯片充分利用微縮帶來益處,小小芯片很可能其發(fā)熱密度能趕上核電站甚至是火箭推進(jìn)器。

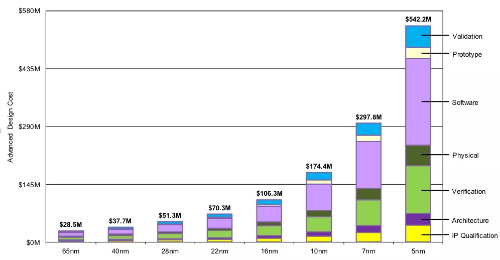

問題來了,20nm以下的工藝發(fā)展,且不論能否造出來,假設(shè)CMOS器件制造無礙,能否繼續(xù)享受摩爾定律器件微縮帶來的芯片性能的上升紅利?由于發(fā)熱宛如小火爐現(xiàn)象,實(shí)際摩爾定律發(fā)展邊際效應(yīng)已然遞減。而且,更現(xiàn)實(shí)的問題是設(shè)計(jì)成本。20nm以下的工藝采用FinFET/GAA等立體結(jié)構(gòu),無論數(shù)字還是模擬電路,設(shè)計(jì)難度指數(shù)級上升,設(shè)計(jì)成本更是讓一般的芯片公司望洋興嘆。一顆5nm SoC的設(shè)計(jì)成本是28nm的10倍之多。相比之下,帶來性能躍遷只有2、3倍。從經(jīng)濟(jì)的角度,除了少部分出貨量超過100KK的芯片,大部分芯片的微縮已經(jīng)停滯在了28nm節(jié)點(diǎn)上下。當(dāng)然,這種停滯還可能源于某些國際政治的因素。比如某西方大國不讓我們的某實(shí)力大廠在某島的代工廠上流14nm以下的工藝等。還有就是,2nm以下的芯片能不能造出來,大家也沒啥譜。畢竟已經(jīng)是十幾個(gè)原子的事情了,現(xiàn)在基于量子力學(xué)的半導(dǎo)體物理理論管不管用還兩說呢。

總而言之,所謂“后摩爾”指的就是當(dāng)摩爾定律對于大部分芯片設(shè)計(jì)公司來說已經(jīng)停滯時(shí),有沒有什么顛覆性技術(shù)可以讓芯片在沒有尺寸微縮的前提下繼續(xù)保持PPA的提升。

簡單而言,可以從器件、架構(gòu)、集成方法的角度來討論后摩爾的關(guān)鍵技術(shù)。

后摩爾器件:CMOS工藝的百尺竿頭

既然CMOS器件在先進(jìn)節(jié)點(diǎn)已經(jīng)如此掙扎,那“后摩爾”時(shí)期,是否可以找一些能和CMOS工藝的兼容的新器件代替?zhèn)鹘y(tǒng)的MOS器件呢?這一想法的率先在存儲器中完成落地。

ISSCC 2021中,中科院微電子所在14nm FinFET工藝節(jié)點(diǎn)上,用憶阻器實(shí)現(xiàn)的阻變RAM(ReRAM)代替了傳統(tǒng)的基于Flash 浮柵MOS管。在CMOS兼容的工藝?yán)铮捎眯略砥骷?shí)現(xiàn)了FinFet工藝的非易失存儲。相比之下,F(xiàn)lash工藝在28nm,甚至40nm就已經(jīng)達(dá)到了工藝微縮的極限。

不僅用于存儲,由于ReRAM的器件具有電阻特性,與電流、電壓可通過歐姆定律、基爾霍夫定律實(shí)現(xiàn)乘和累加的物理關(guān)系,因此可被廣泛用于并行模擬計(jì)算電路中,這種電路也被稱為存算一體。ISSCC 2021中,臺灣清華大學(xué)通過數(shù)模混合的計(jì)算電路,首次基于ReRAM的實(shí)現(xiàn)8位的存算一體電路,且能效保持在11TOPS/W。其電路模塊結(jié)構(gòu)如下所示:

后摩爾架構(gòu):算法與電路的緊耦合契機(jī)

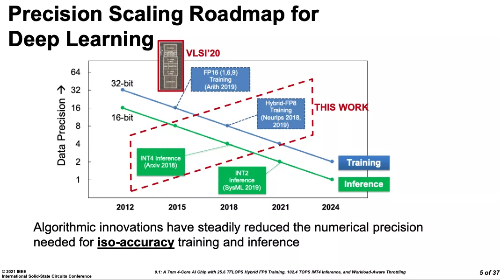

除了器件本身,“后摩爾”的另一潛力的來源是其專用性。傳統(tǒng)的通用電路性能飽和,所以這兩年“領(lǐng)域?qū)S谩钡脑O(shè)計(jì)如火如荼。ISSCC自然也不能缺席。特別是在人工智能芯片領(lǐng)域。目前AI算法發(fā)展速度是每3.4個(gè)月算力翻倍,而摩爾定律最快也得1.5年單位面積上的尺寸翻倍。若要能稍稍趕上這一發(fā)展速度,就得聯(lián)合算法尋找新的契機(jī)。

在ISSCC的AI芯片Session中,幾乎所有芯片設(shè)計(jì)都緊緊擁抱了算法,基于協(xié)同設(shè)計(jì)催化出更好的性能。例如,IBM提出的基于混合8位浮點(diǎn)的AI訓(xùn)練芯片。通過自定義FP8的數(shù)據(jù)格式,完成訓(xùn)練。精度上,和標(biāo)準(zhǔn)32位浮點(diǎn)的訓(xùn)練精度相差不超過1%,同時(shí)功耗又能保持在3TOPS/W以上,避免GPU百瓦級的耗電與發(fā)熱。

還有清華大學(xué)在ISSCC 2021報(bào)告的兩篇存算一體SoC的論文。

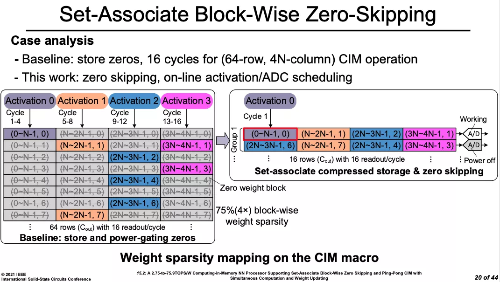

第一篇通過利用傳統(tǒng)Cache一致性機(jī)制中的Set Associative技術(shù),存算一體系統(tǒng)芯片中的再發(fā)明,完成了對稀疏輸入的高效讀寫與計(jì)算,用更小的硬件代價(jià)完成更大規(guī)模的計(jì)算。

第二篇通過利用In-tensor decomposition train算法將最占據(jù)存儲空間的神經(jīng)網(wǎng)絡(luò)權(quán)重最大的三維卷積核 分解為多個(gè)小向量的乘積,通過僅存儲這些小向量的方式,結(jié)合量化和稀疏性優(yōu)化實(shí)現(xiàn)高性能片上存儲空間。

可見,上述方法的性能提升及其背后的新架構(gòu)探索,都不適用于通用計(jì)算,但是通過算法與電路的更緊密結(jié)合,突破目前“摩爾時(shí)期”通用模塊的性能瓶頸的效果顯著。

后摩爾集成:3D視角重新定義芯片與互聯(lián)

摩爾定律的“初心”判斷標(biāo)準(zhǔn)是單位面積上的晶體管數(shù)量的增長速度。在過去的很多年里,摩爾定律關(guān)心的都是二維平面上CMOS器件的尺寸微縮。但在后摩爾時(shí)代,如果二維的增長飽和了,為什么不考慮三維呢?ISSCC 2021上有多篇從3D視角切入的芯片可以提供討論。

首先是來自Sony的智能CIS傳感芯片。由于人工智能應(yīng)用的興起,進(jìn)傳感器側(cè)的AI芯片一直是CIS領(lǐng)域的熱門話題。Sony通過三維封裝與Cu-Cu互聯(lián),將一個(gè)CMOS圖像傳感器陣列與模擬前端、AI芯片集成在一個(gè)封裝內(nèi)。利用Cu-Cu互聯(lián)高帶寬避免了額外的傳感器與處理器數(shù)據(jù)通信瓶頸。

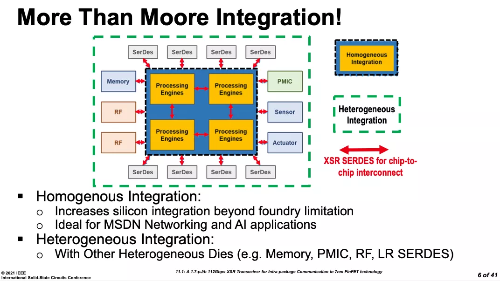

此外,三維封裝的另一個(gè)火熱話題是Chiplet。雖然ISSCC 2021的論文中未有太多的Chiplet paper,但是在forum上,也披露了不少已發(fā)表的Chiplet高性能處理器的設(shè)計(jì)細(xì)節(jié)。

比如AMD 二代EPYC架構(gòu)服務(wù)器處理器芯片中基于Chiplet、無源連接基板和有源硅互聯(lián)芯片的協(xié)同設(shè)計(jì)方法,闡述了其從芯片級到板級到系統(tǒng)級的考慮。

還有Nvidia的Chiplet多AI加速器MCM集成芯片,進(jìn)一步討論了其互聯(lián)與軟件部署算法的系統(tǒng)設(shè)計(jì)考慮。這種場景下,芯片的設(shè)計(jì)視角需要跳脫單芯片的局部優(yōu)化,而走向超大規(guī)模算力集成下的軟硬件協(xié)同優(yōu)化。有可能,我們即將來到一個(gè)3D封裝重新定義單芯片的新格局。

在這一背景下,大廠們也開始積極布局面向Die-to-Die的互聯(lián)電路,Wireline session中Samsung、Cadence都有高性能片間互聯(lián)的新電路設(shè)計(jì)。但目前為止,還是經(jīng)典的Serdes的高能效設(shè)計(jì),能否有顛覆性技術(shù)出現(xiàn)讓我們拭目以待。

其實(shí)還有很多ISSCC 的好paper難以窮舉,你眼中的后摩爾技術(shù)還有什么呢?