在最近的ISSCC會議上,來自英特爾的Mozhgan Mansuri就有線和無線接口設(shè)計中與時鐘有關(guān)的內(nèi)容做了一個很有啟發(fā)性的簡短演講。這次演講非常深入,包括了從基本的時鐘原理到合成和分配時鐘信號的獨特電路設(shè)計策略的回顧。

由于涉及的主題過多,這里將重點介紹基于有線的設(shè)計注意事項。

有線數(shù)據(jù)速率趨勢

描述了幾種接口標(biāo)準(zhǔn)下線纜“每通道數(shù)據(jù)率”的進(jìn)展情況。

摩爾定律的PPA效益與接口數(shù)據(jù)率的增強是并行發(fā)展的,每2-3年翻一番。然而,由于有線鏈接橫跨硅芯片、封裝、電路板互連、連接器和電纜,單單硅技術(shù)的擴展并不能說明所有的數(shù)據(jù)速率提升。封裝/PCB材料的改進(jìn)和仿真工具的進(jìn)步無疑是有幫助的。

這種增長的關(guān)鍵是支持信道Tx和Rx端的接口電路的持續(xù)改進(jìn)。相關(guān)的時鐘生成(和Rx時鐘恢復(fù))技術(shù)一直是這些電路創(chuàng)新的核心,如下圖所示,顯示了數(shù)據(jù)中的嵌入式時鐘和時鐘轉(zhuǎn)發(fā)選項。

時鐘定義

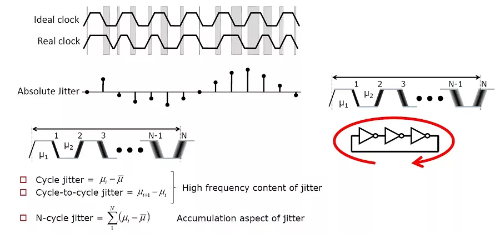

基本時鐘定義如下所示:

時鐘周期

占空比

時鐘漂移(靜態(tài)占空比誤差,半個周期持續(xù)時間之差)

時鐘周期之間的抖動

請注意,在上面的最后一個圖中,抖動可能會隨著時間的推移而累積,正如奇數(shù)逆變器、自由運行的振蕩器時鐘源所描述的那樣。

下圖說明了時鐘分布的兩個關(guān)鍵測量(和規(guī)格)。圖的前半部分說明了電路對抖動頻率內(nèi)容的頻率響應(yīng);后半部分說明了Rx時鐘恢復(fù)電路對抖動的 “容忍度”。

這些數(shù)字包括頻率上的典型規(guī)格“掩模”。上面描述的“理想”抖動傳遞曲線通過時鐘分布組件提供了一個“0分貝,無抖動放大”的目標(biāo)掩碼。抖動容忍掩碼規(guī)范使設(shè)計者能夠開發(fā)Rx時鐘恢復(fù)電路,隨后確保Tx抖動源不超過掩碼限制。

時鐘合成電路

為了在片上產(chǎn)生高頻時鐘,常用的方法是采用兩種主要電路類型之一—PLL(phase-lockedloop)和DLL(delay-locked loop)。它們的主要功能是提供一個由低頻(高質(zhì)量)參考時鐘衍生出來的 “倍增 ”時鐘輸出,如下所述。另一個關(guān)鍵的時鐘合成配置是用一個“注入鎖定振蕩器”(ILO)來對單個時鐘進(jìn)行相位校準(zhǔn)。

PLL

PLL由以下部分組成

一個壓控振蕩器

N分頻計數(shù)器

相位檢測器,它提供的輸出信號與參考時鐘和分頻VCO時鐘之間的前導(dǎo)/后導(dǎo)相位差成正比。

一個低通濾波器,可以有效地阻止來自相位檢測器的短時信號影響VCO的控制輸入。

PLL的頻率帶寬響應(yīng)定義了抖動響應(yīng),這是一個關(guān)鍵的設(shè)計權(quán)衡。例如,較低的帶寬將降低參考時鐘輸入的抖動靈敏度。較高的帶寬將降低對VCO抖動的靈敏度。

DLL

上圖說明了DLL的基本原理。鎖相環(huán)中自由運行的VCO振蕩器被延遲線所取代,延遲線的單個延遲元件由鑒相器和低通濾波器輸出控制-圖中顯示的是一個簡單的變頻延遲鏈。抖DLL時鐘輸出中的抖動通過每N個周期使用參考時鐘邊沿進(jìn)行 “復(fù)位”,使用多路復(fù)用器輸出提供延遲鏈輸入--見圖中時序圖。

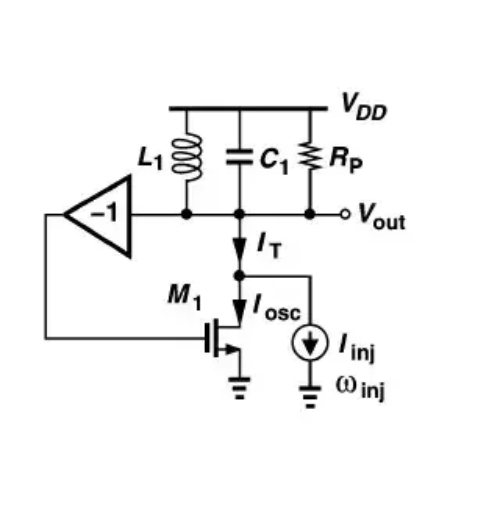

注入鎖定振蕩器(ILO)

時鐘合成的另一種選擇是使用注入電流到振蕩系統(tǒng),以提供輸出時鐘相位調(diào)節(jié)控制。

ILO高層框圖如下所示,有三部分值得注意。

振蕩器(簡單描述為n FET和反相放大器)

一種調(diào)諧槽電路

注入電流源

讓我們回憶一個有趣的物理實驗,在這個實驗中,相同時間段的多個節(jié)拍器是松散耦合的—但隨著時間的推移,它們就會保持到同步。

一個頻率為f的注入電流同樣會使組合系統(tǒng)的輸出電壓同步到這個頻率。然而,由于三個分量的相對阻抗,系統(tǒng)輸出電壓與組成電流I_tank、I_osc和I_inj之間會產(chǎn)生相移,如下圖所示。

簡而言之,Vout = (Z_tank * I_tank),其中I_tank = (I_osc + I_inj)。這些都是具有幅度和相位的復(fù)雜量。ILO的主要特點是,注入電流的大小可以調(diào)整輸出電壓的相位。

因此,ILO是校準(zhǔn)(或“旋轉(zhuǎn)”)時鐘輸出相位的理想方法,相對于基準(zhǔn)-相位差檢測器增加/減少注入電流的大小相應(yīng)。

考慮這樣一種情況,希望從一個振蕩器的多個內(nèi)部階段產(chǎn)生時鐘,每個時鐘通過一個特定的相位移位/對齊。下面的例子顯示了4個相同頻率的時鐘,每個相位偏移了90度。

對這些移位時鐘的邏輯運算產(chǎn)生獨特的脈沖,例如,clock_0和clock_270。當(dāng)提供了與這些移位時鐘的邏輯操作對應(yīng)的轉(zhuǎn)換的數(shù)據(jù)訓(xùn)練模式時,數(shù)據(jù)和時鐘脈沖之間的相位差可以通過注入鎖定電流檢測和校準(zhǔn)。一旦校準(zhǔn),時鐘就可以用于以高數(shù)據(jù)速率- 4X參考時鐘頻率發(fā)送/接收數(shù)據(jù),如上面的例子。

前面的討論提到了時鐘生成電路的框圖--Mozhgan在她的演講中詳細(xì)介紹了這些單元。

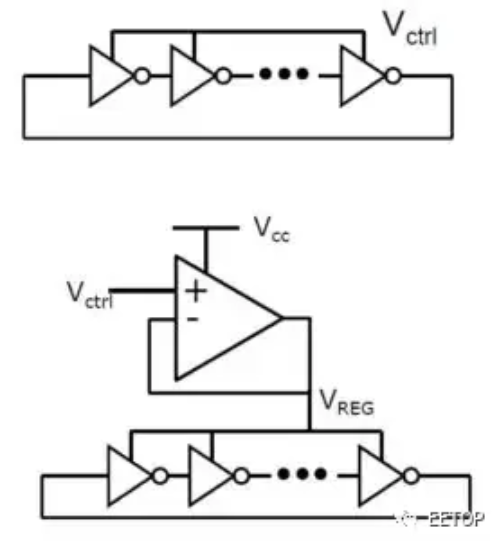

VCO

她演講中的壓控振蕩器的例子如下圖所示。

第一個例子是一個簡單的(奇數(shù))變頻器環(huán)路,提供一個自由運行的振蕩器--每級的延遲由電壓控制信號修改。(也經(jīng)常使用引入延遲控制的其他方法,例如,使用變?nèi)荻O管給每個級增加可變?nèi)菪载?fù)載;使用“電流缺乏”逆變器,在下拉/上拉堆棧中附加一個系列FET/p/FET,其器件門提供電壓控制輸入。)這種自由運行的拓?fù)浣Y(jié)構(gòu)的一個缺點是對電源/控制輸入端的噪聲敏感。

上圖所示的第二個例子包括一個運算放大器/調(diào)節(jié)器作為低通濾波器,以改善電源噪聲抑制。

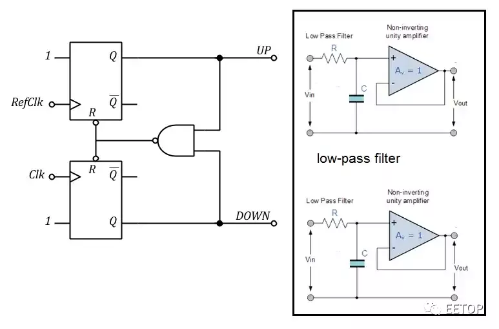

相位差檢測器

將參考時鐘與(分頻)時鐘進(jìn)行比較的時鐘生成電路使用相位差檢測器向VCO提供控制信號。常用的檢測器拓?fù)溆泻芏?-下面是一個簡單的(數(shù)字)實例實現(xiàn)。

這種拓?fù)浣Y(jié)構(gòu)適合于使用兩個輸入--“UP ”和 “DOWN ”來代表參考時鐘和生成時鐘之間的滯后/領(lǐng)先相位差的振蕩器控制電路。(需要一個低通濾波器來消除上升時鐘和異步復(fù)位輸入之間的任何雜散觸發(fā)輸出脈沖。)

時鐘分配

Mozhgan介紹了一些常見的設(shè)計拓?fù)洌糜趯ne-die產(chǎn)生的時鐘分配到(Tx或Rx)扇出。下圖描述了三個例子,適用于單個(全局)時鐘在被分接到一系列總線之前跨越相當(dāng)長距離的情況。

無中繼拓?fù)洌ú罘帧⒌蛿[信令),將互連視為LC傳輸線。

逆變再發(fā)電鏈

電流模式邏輯逆變器驅(qū)動鏈

此外Mozhgan的演講還涵蓋了大量額外的主題,這里沒有重點介紹--例如,有線Rx時鐘-數(shù)據(jù)對齊策略(適用于轉(zhuǎn)發(fā)時鐘和嵌入式SerDes時鐘接口)、無線傳輸/接收機的時鐘生成、時鐘功率優(yōu)化。