縱觀全球,研究人員在內(nèi)存計算(in-memory computing)架構(gòu)上的研究非常活躍。在最近的國際固態(tài)電路會議(ISSCC 2021)上,針對新穎的存儲器陣列技術的多個技術會議專門用于支持機器學習算法的計算需求。

眾所周知,現(xiàn)在將數(shù)據(jù)和權重值從內(nèi)存移動到處理單元,然后再將中間結(jié)果存儲回內(nèi)存的做法效率低下。因為信息傳輸過程中不僅增加了計算延遲,而且相關的功耗是一個主要問題。

如下所示,“無增值”的數(shù)據(jù)移動消耗了大部分的能耗,這個比例甚至可能大于“增值”計算的能量消耗。請注意,實際的計算能耗是與數(shù)據(jù)和權重傳遞到計算單元相關的一小部分。

而存內(nèi)計算的目標是減少這些低效率,這對于在邊緣實施機器學習推理系統(tǒng)尤其重要。

機器學習應用中的存內(nèi)計算的主要重點是優(yōu)化與每個神經(jīng)網(wǎng)絡節(jié)點關聯(lián)的向量乘法累加(MAC)操作。下圖說明了(訓練的)網(wǎng)絡的計算——每個數(shù)據(jù)輸入乘以權重值的乘積,然后提供給偏差和激活函數(shù)。

對于一般網(wǎng)絡,數(shù)據(jù)和權重通常是多位數(shù)。權重向量(對于經(jīng)過訓練的邊緣AI網(wǎng)絡)可以使用有符號,無符號或二進制補碼整數(shù)位表示形式。

對于存內(nèi)計算,最終的MAC輸出是通過添加部分乘法乘積來實現(xiàn)的。節(jié)點中每個(數(shù)據(jù)*權重)弧(arc)的位寬是定義明確的-例如,2n位向量覆蓋2 n位無符號整數(shù)的乘積。但是,將所有弧的(數(shù)據(jù)*權重)乘積累加到高度連接的網(wǎng)絡中可能需要更多的位才能準確表示MAC結(jié)果。

存內(nèi)計算研究的重點領域之一是使用電阻RAM(ReRAM)位單元實現(xiàn)位線電流檢測測量。數(shù)據(jù)輸入(作為活動存儲器行字線)和存儲在ReRAM單元中的權重值的乘積會產(chǎn)生可區(qū)分的位線電流,該電流用于為參考電容充電。后續(xù)的模數(shù)轉(zhuǎn)換器(ADC)將該電容器電壓轉(zhuǎn)換為等效的二進制值,以進行后續(xù)的MAC移位累加。盡管(數(shù)據(jù)*權重)產(chǎn)品基于ReRAM的實現(xiàn)具有區(qū)域效率,但它也有其缺點:

由于電壓范圍,噪聲和PVT的變化,模擬位線電流檢測和ADC的精度受到限制

ReRAM陣列的寫入周期時間長

ReRAM陣列的耐用性嚴重限制了其作為通用內(nèi)存存儲陣列的適用性

這些問題都得出相同的結(jié)論。對于一個相對較小的推理神經(jīng)網(wǎng)絡,其中所有權重都可以加載到內(nèi)存陣列中,并且數(shù)據(jù)矢量表示受到限制(例如8位或更少),基于ReRAM的實現(xiàn)將帶來部門優(yōu)勢。

但是,對于需要網(wǎng)絡大于陣列中存儲的網(wǎng)絡和/或需要重新配置的工作量的機器學習應用,更新權重值通常會阻止使用ReRAM當前檢測方法。在數(shù)據(jù)精度要求很高的情況下,同樣的問題也適用,因此需要更大的輸入向量。

存內(nèi)計算體系結(jié)構(gòu)的替代方法是利用增強的SRAM陣列來支持(數(shù)據(jù)*權重)計算,而不是采用新穎的存儲技術。這允許支持更豐富的機器學習網(wǎng)絡集。

如果層數(shù)很大,則可以將輸入值和權重值加載到SRAM陣列中以進行節(jié)點計算,保存輸出值以及檢索后續(xù)的層值。與通用計算解決方案相比,減少了與數(shù)據(jù)和權重傳遞相關的能耗,并且消除了ReRAM耐久性的問題。

使用擴展SRAM設計的存內(nèi)計算

在最近的ISSCC上,臺積電的研究人員提出了一種基于數(shù)字改良的SRAM設計存內(nèi)計算方案,能支持更大的神經(jīng)網(wǎng)絡。

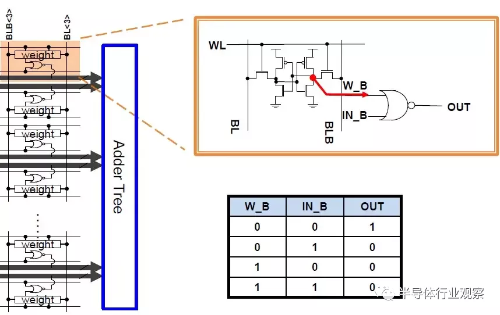

上圖顯示了臺積電用于其測試的擴展SRAM陣列配置——陣列的一部分被圈出。每個切片具有256個數(shù)據(jù)輸入,它們連接到“ X”邏輯(稍后將對此邏輯進行更多介紹)。數(shù)據(jù)輸入向量的連續(xù)位在連續(xù)的時鐘周期中提供給“ X”門。每個切片存儲256個4位權重段,每個數(shù)據(jù)輸入一個權重半字節(jié)。這些權重位使用常規(guī)的SRAM單元,因為它們可能會經(jīng)常更新。存儲在每個權重位中的值連接到“ X”邏輯的另一個輸入。

下圖說明了如何將此邏輯集成到SRAM中。

其中,“ X”是2輸入或非門,具有數(shù)據(jù)輸入和權重位作為輸入。(兩個“一位”值的乘積由“與”門實現(xiàn);通過使用反相信號值和DeMorgan定理,2輸入“或非”門在面積和功率方面都具有效率。)在每個限幅之間,有一個加法器樹和一個加法器樹。集成了部分和累加器邏輯,如下所示。

請注意,上圖中的加權位存儲使用常規(guī)的SRAM拓撲-對于6T的位單元,加權位字線和位線照常連接。每個單元上的存儲值都扇出到或非門的一個輸入。

每個切片的輸出表示每個權重向量的半字節(jié)的部分乘積和。擴展數(shù)組之外的其他邏輯提供了移位和相加計算,以實現(xiàn)更寬的權重值表示。例如,(有符號或無符號整數(shù))16位權重將合并來自四個條帶的累加器結(jié)果。

現(xiàn)場測試結(jié)果

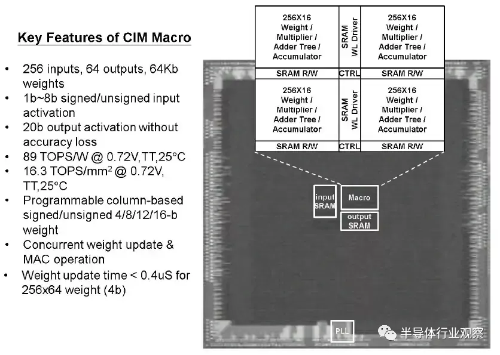

下方顯示的是臺積電基于全數(shù)字SRAM的測試工具的顯微照片,突出顯示了256輸入,16切片(4位重量半字節(jié))的宏設計。

請注意,基于SRAM的Compute-in-Memory宏的關鍵規(guī)范之一是可以在陣列中更新新權重的效率。

相對于電源電壓的測量性能(TOPS)和功率效率(TOPS / W)如下所示。請注意,基于數(shù)字邏輯的MAC的使用可在很寬的電源電壓范圍內(nèi)提供功能。

(從理論上講,通常用于描述神經(jīng)網(wǎng)絡實現(xiàn)功率效率的TOPS / W品質(zhì)因數(shù)可能是一種誤導性度量–它在很大程度上取決于陣列中權重的“密度”和翻轉(zhuǎn)率下圖還有一張圖,說明了此度量如何取決于輸入切換率,假設權重向量中“ 1”值的比率為50%。)

盡管此內(nèi)存計算測試站點是在較舊的22nm工藝中制造的,但將這種設計擴展到5nm節(jié)點時,TSMC研究人員提供了初步的面積和功率效率估算。

總結(jié)

研究人員目前正在進行大量研究活動,以支持用于機器學習的存內(nèi)計算,以減少馮·諾依曼架構(gòu)中數(shù)據(jù)傳輸?shù)男实拖隆Q芯康囊粋€方面是尋求使用新的內(nèi)存存儲技術,例如ReRAM。但ReRAM的有限耐用性將這種方法的范圍限制在權重值不會經(jīng)常更新的應用中。位線電流檢測的有限精度也限制了數(shù)據(jù)輸入向量的寬度。

臺積電(TSMC)展示了如何擴展常規(guī)SRAM陣列以支持大型和/或可重新配置網(wǎng)絡的內(nèi)存計算,并且需要頻繁寫入權重值。在SRAM行和列之間插入2輸入或非門和加法器樹邏輯提供了一種節(jié)省面積和功耗的方法。