“網(wǎng)絡(luò)就是計算機”,這是太陽微系統(tǒng)公司的John Gage在1984年提出的理論,被證明是非常有見地的。如今在SoC領(lǐng)域這個想法再次出現(xiàn)。在一個芯片中,相互通信的功能——不是通過簡單的電線,而是通過如交換機、協(xié)議轉(zhuǎn)換器、封裝器等復(fù)雜的網(wǎng)絡(luò)元件。這與1984年在一個機柜或房間中通過網(wǎng)絡(luò)進行通信的一組計算機沒太大區(qū)別。

在SoC出現(xiàn)之前,為了在一塊板子上從A連接到B,工程師們可以通過一堆電線來傳輸數(shù)據(jù)。最大的擔(dān)憂是管理電線長度,并確保A和B使用完全相同的協(xié)議進行通信,但僅此而已。真正的動作是在計算元素中。在這些珍貴的組件之間連接是一個簡單的設(shè)計任務(wù)。

但在過去的幾十年里,集成電路制造工藝技術(shù)、封裝與測試技術(shù)、設(shè)計方法學(xué)和EDA 工具等微電子相關(guān)技術(shù)始終保持著快速的發(fā)展。根據(jù)國際半導(dǎo)體技術(shù)發(fā)展路線圖(International Technology Roadmap for Semiconductors, ITRS)預(yù)測,到2024年每平方毫米集成的晶體管數(shù)目將達到90 億個。但是,全局互連線的性能提升程度明顯低于晶體管性能提升程度。受到亞閾值漏電流功耗、動態(tài)功耗、器件可靠性以及全局互連線等影響,通過提升單個處理器核的性能來提升系統(tǒng)整體性能已變得非常難以實現(xiàn),同時芯片設(shè)計的難度和復(fù)雜度也在進一步增加。這個時候SoC就誕生了。SoC具有集成度高、功耗低、成本低、體積小等優(yōu)點,已經(jīng)成為超大規(guī)模集成電路系統(tǒng)設(shè)計的主流方向。隨著片上系統(tǒng)SoC 的應(yīng)用需求越來越豐富、越來越復(fù)雜,片上多核MPSoC已經(jīng)成為發(fā)展的必然趨勢,同時MPSoC 上集成的IP核數(shù)量也將會按照摩爾定律繼續(xù)發(fā)展。

從電線到主動總線邏輯

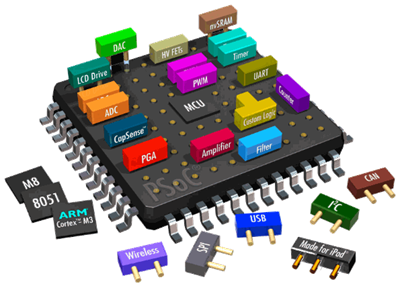

隨著SoC能力的增長,將整個板甚至更大的系統(tǒng)整合到單個芯片上成為可能,所有這些都由一個中央處理單元(CPU)或處理器集群管理。每個CPU運行軟件來協(xié)調(diào)系統(tǒng)以處理需要軟件支持的靈活性的功能。提供處理器的Arm等公司的解決方案迅速興起,其他供應(yīng)商也在跟進,包括CPU以外功能IP供應(yīng)商。首先,通過提供外圍IP來處理許多接口協(xié)議,然后發(fā)展為用于無線通信、圖形處理、音頻、計算機視覺和人工智能(AI)這些專門的處理器。此外,還包括片上工作存儲器、緩存存儲器、到片外或片外DRAM的雙數(shù)據(jù)速率(DDR)接口等。

而且,還有許多很棒的功能可以集成到高級SoC中,但是它們?nèi)绾瓮ㄐ拍兀窟@里不能通過直接連接,因為整個芯片會被電線覆蓋。CPU和內(nèi)存在確定下一步要服務(wù)什么方面會慢得無法想象。相反,“所有的交通都必須通過高速公路,并設(shè)有計量入口匝道。”如果一個IP想要與中央處理器通信,它必須等待輪到它進入高速公路。

現(xiàn)在的Bus總線不再只是一種愚蠢的電線。監(jiān)視正在進行的操作和下一步要允許的操作,二者是有邏輯的,此外,隊列支持的數(shù)據(jù)在以不同速度運行的域之間流動。流水線寄存器幫助跨越很大的距離,同時滿足時間限制。我們將其稱為“總線結(jié)構(gòu)”,通過控制邏輯、多路復(fù)用技術(shù)、寄存器和先入先出的通信順序?qū)⑦B接編織起來。

總線體系結(jié)構(gòu)的發(fā)展

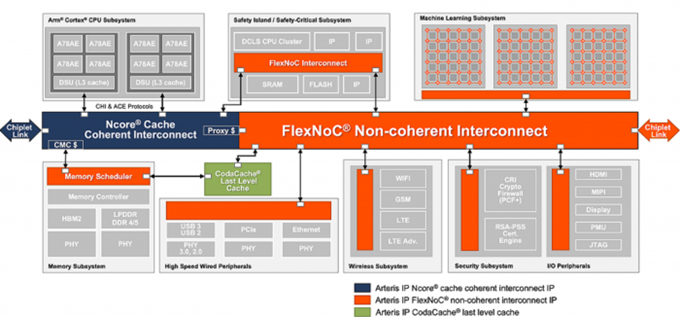

既然有了總線結(jié)構(gòu)的架構(gòu),就可以為不同的目的設(shè)想不同的架構(gòu)了。高級微控制器總線體系結(jié)構(gòu)(AMBA)家族本身就有多種風(fēng)格,每一種都有自己的優(yōu)勢和限制。很可能,在一個復(fù)雜的SoC中需要幾個。但是還有另一種非常不同的技術(shù)——芯片上網(wǎng)絡(luò)(NoC),它在概念上非常不同,NoC并沒有緊密地耦合互連通信和物理傳輸,而是開辟了新的架構(gòu)選項。

Noc的發(fā)展是以SoC為基礎(chǔ)。SoC通常是指在單一芯片上實現(xiàn)的數(shù)字計算機系統(tǒng),通過總線完成其中各模塊之間的交互,但隨著半導(dǎo)體工藝和需求的快速發(fā)展,總線的寬度已經(jīng)成為SoC發(fā)展的瓶頸,大大限制了SoC內(nèi)部通信的速度。90年代NoC技術(shù)的提出也是因為借鑒了并行計算機的互聯(lián)網(wǎng)絡(luò)和以太網(wǎng)絡(luò)的分層思想,二者的相同點有:支持包交換、路由協(xié)議、任務(wù)調(diào)度、可擴展等。NoC更關(guān)注交換電路和緩存器的面積占用,在設(shè)計時主要考量的方面也是這些。

還有另一個重要的考慮因素。典型的SoC現(xiàn)在將圍繞眾多第三方IP和一些集成商具有定制優(yōu)勢的自有IP構(gòu)建。這其中優(yōu)勢有多大呢?競爭對手可以購買相同的第三方產(chǎn)品,這就稀釋了可能的差異化。然后,挑戰(zhàn)就變成了設(shè)計團隊如何有效地集成SoC。

我們確實有這樣做的空間。帶寬、吞吐量、服務(wù)質(zhì)量(QoS)、功率、安全性和成本都由集成方案所決定。這些因素都受到已實現(xiàn)的通信架構(gòu)的影響,很可能是一個NoC。最終,使芯片具有競爭力的是對IP和片上通信架構(gòu)的謹慎選擇。