2021年5月5日,加利福尼亞州圣克拉拉——應(yīng)用材料公司今天宣布推出一系列材料工程解決方案,為存儲客戶提供三種全新進(jìn)一步微縮DRAM的方法,并加速改善芯片性能、功率、面積、成本和上市時間(即:PPACt)。

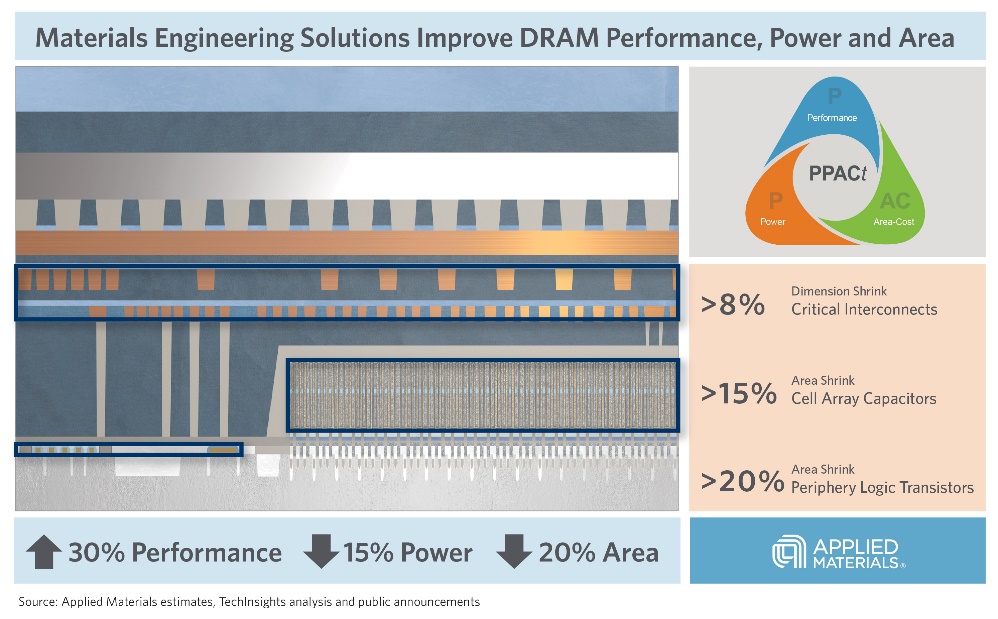

應(yīng)用材料公司全新的材料工程解決方案可助力DRAM性能提升30%、功率降低15%、面積減少20%

全球經(jīng)濟(jì)的數(shù)字化轉(zhuǎn)型正在催生對DRAM創(chuàng)紀(jì)錄的需求。物聯(lián)網(wǎng)創(chuàng)造了數(shù)千億臺新的邊緣計算設(shè)備,推動著數(shù)據(jù)上云處理的指數(shù)級增長。因而,行業(yè)迫切需要在DRAM微縮領(lǐng)域取得突破,以減少芯片面積和成本,同時提高運(yùn)行速度、降低功率。

應(yīng)用材料公司正與DRAM客戶合作,將三種材料工程解決方案商業(yè)化。這三種解決方案不僅創(chuàng)造了新的微縮方式,也提升了性能和功率。這些解決方案針對的是DRAM芯片的三個方面:存儲電容器、互連布線和邏輯晶體管。這些解決方案現(xiàn)已投入大規(guī)模量產(chǎn),預(yù)計未來幾年將為應(yīng)用材料公司的DRAM業(yè)務(wù)帶來顯著營收增長。

推出應(yīng)用于電容器微縮的Draco?硬掩模

在DRAM芯片中,超過55%的晶粒面積被存儲陣列占據(jù),提高存儲陣列的密度是降低每比特成本的最有效手段。數(shù)據(jù)以電荷形式存儲在垂直排列的圓柱形電容器中,要想容納足夠數(shù)量的電子,電容器需具備盡可能大的表面積。DRAM制造商在縮小電容器直徑的同時也會拉長其高度,以將電容器表面積最大化。而這也給DRAM微縮帶來了新的技術(shù)挑戰(zhàn):電容器深孔的刻蝕可能會超過“硬掩模”材料的極限。硬掩模作為確定每個孔洞位置的模板,如果因為太薄被蝕穿,圖案就會被毀壞。可是較厚的硬掩模也不適用,因為當(dāng)硬掩模和電容器孔洞的總體深度超出一定限度時,刻蝕副產(chǎn)品會殘留,導(dǎo)致彎曲、扭曲和深度不均。

為此,應(yīng)用材料公司推出了Draco?解決方案。這是一種新型硬掩模材料,已經(jīng)過協(xié)同優(yōu)化可與應(yīng)用材料公司的Sym3? Y刻蝕系統(tǒng)在其PROVision? 電子束測量和檢測系統(tǒng)監(jiān)控的流程中配合使用,其中PROVision? 電子束系統(tǒng)每小時可進(jìn)行近50萬次測量。Draco硬掩模將刻蝕選擇比提高了30%以上,使得掩模更薄。Draco硬掩模和Sym3 Y的協(xié)同優(yōu)化包括先進(jìn)的射頻脈沖優(yōu)化,可使刻蝕與副產(chǎn)品去除同步進(jìn)行,從而令成像孔洞呈完美圓柱形且筆直均勻。PROVision 電子束系統(tǒng)可為客戶提供硬掩模關(guān)鍵尺寸均勻性的大量、即時可執(zhí)行數(shù)據(jù),這正是電容器均勻性的關(guān)鍵所在。應(yīng)用材料公司的解決方案為客戶提供了50%的局部關(guān)鍵尺寸均勻性提升,并將橋連缺陷降低了100倍,從而提升了良率。

應(yīng)用材料公司半導(dǎo)體產(chǎn)品事業(yè)部集團(tuán)副總裁Raman Achutharaman博士表示:“與客戶攜手快速解決材料工程挑戰(zhàn)的最佳方法是協(xié)同優(yōu)化相鄰步驟,并使用大量測量和人工智能來優(yōu)化工藝變量。”

將Black Diamond?低k介電引入DRAM市場

DRAM微縮的第二個關(guān)鍵方法是減少互連布線所需的晶粒面積,互連布線用于在存儲器陣列間來回傳遞信號。每條金屬線被絕緣介電材料環(huán)繞,以防止數(shù)據(jù)信號之間產(chǎn)生干擾。在過去25年里,DRAM制造商一直將兩種硅氧化物——硅烷或四乙氧基硅烷(TEOS)中的一種用作介電材料。盡管介電層不斷減薄使得DRAM晶粒尺寸縮小,但這也帶來了新的技術(shù)挑戰(zhàn):如今,介電層太薄,無法防止金屬線之間發(fā)生電容耦合,信號產(chǎn)生相互干擾,導(dǎo)致功率升高、性能降低、熱量提升和可靠性風(fēng)險增加。

為此,應(yīng)用材料公司提出了Black Diamond?解決方案,這是一種首先被用于先進(jìn)邏輯器件的低k介電材料。伴隨DRAM設(shè)計面臨同樣的微縮挑戰(zhàn),應(yīng)用材料公司正在著力使Black Diamond?適應(yīng)DRAM市場,并將其搭載在生產(chǎn)效率極高的Producer? GT平臺上。適用于DRAM的Black Diamond?使得互連線更加纖小緊湊,能以數(shù)千兆赫的速度在芯片中傳輸信號,不受干擾并且功率更低。

高k金屬柵極晶體管可優(yōu)化DRAM的性能、功率、面積和成本

DRAM微縮的第三個關(guān)鍵方法是提升芯片外圍邏輯器件中使用的晶體管的性能、功率、面積和成本,幫助驅(qū)動高性能DRAM(如基于新DDR5規(guī)范的DRAM)所需的輸入輸出(I/O)操作。

直至今日,DRAM仍使用基于多晶硅和氧化硅介電層的晶體管,這種晶體管在邏輯器件代工中為28納米節(jié)點所淘汰,因為柵極介電層的極度減薄會導(dǎo)致電子泄漏,從而浪費(fèi)功率并限制性能。邏輯芯片制造商采用高k金屬柵極(HKMG)晶體管,用金屬柵極代替多晶硅,用氧化鉿代替氧化硅介電層(氧化鉿是一種可改善柵極電容、漏電流和器件性能的材料)。如今,存儲器制造商正在將HKMG晶體管設(shè)計用于先進(jìn)的DRAM,以優(yōu)化性能、功率、面積和成本。如邏輯器件一樣,在DRAM中,HKMG將隨著時間的推移而取代多晶硅晶體管。

這種DRAM的技術(shù)變革為應(yīng)用材料公司創(chuàng)造了增長機(jī)遇。制造更復(fù)雜、更精細(xì)的HKMG材料堆疊頗具挑戰(zhàn),使用應(yīng)用材料公司的Endura? Avenir? RFPVD系統(tǒng)對相鄰的工藝步驟進(jìn)行不破真空的連續(xù)處理已成為行業(yè)首選解決方案。HKMG晶體管還受益于應(yīng)用材料公司的外延沉積技術(shù),如:Centura? RP Epi和薄膜處理技術(shù)(包括RadOx? RTP、Radiance? RTP和DPN,這些技術(shù)用于微調(diào)晶體管特性以獲得最佳性能)。

Achutharaman博士補(bǔ)充道:“Draco硬掩模和Black Diamond低k介電材料已被全球多個領(lǐng)先DRAM客戶采用,第一批HKMG DRAM現(xiàn)已問市。隨著這些DRAM解決方案成為主流,應(yīng)用材料公司預(yù)計未來幾年的營收將增長數(shù)十億美元。”

關(guān)于這些技術(shù)增長前景的更多信息已在美國時間5月5日舉行的應(yīng)用材料公司2021年存儲大師課上提供。