style="text-align: justify;"> 2021年5月18日,IEEE給BCD工藝開創(chuàng)者意法半導(dǎo)體(STM)頒發(fā)IEEE里程碑獎(jiǎng)(IEEE Milestone),旨在表彰意法半導(dǎo)體在超級(jí)集成硅柵半導(dǎo)體工藝技術(shù)方面的開創(chuàng)性研究成果。

該牌匾將放置在意法半導(dǎo)體在意大利米蘭市近郊曾經(jīng)承擔(dān)BCD開發(fā)工作的Agrate工廠Castelletto工廠的大門口。牌匾上寫著:

IEEE里程碑

單片多硅技術(shù)Multiple Silicon Technologies on a Chip,1985年

SGS(現(xiàn)為意法半導(dǎo)體)率先采用單片集成Bipolar-CMOS-DMOS器件(BCD)的超級(jí)集成硅柵極工藝,解決復(fù)雜的、大功率需求的應(yīng)用設(shè)計(jì)難題。首個(gè)BCD超級(jí)集成電路L6202可以控制最高60V/5A的功率,開關(guān)頻率300kHz。隨后的汽車、計(jì)算機(jī)和工業(yè)自動(dòng)化廣泛采用了這項(xiàng)工藝技術(shù),讓芯片設(shè)計(jì)人員能夠靈活、可靠地單片集成功率、模擬和數(shù)字信號(hào)處理電路。

SGS(now STMicroelectronics) pioneered the super-integrated silicon-gate process combining Bipolar, CMOS, and DMOS (BCD) transistors in single chips for complex, power-demanding applications. The first BCD super-integrated circuit, named L6202, was capable of controlling up to 60V-5A at 300 kHz. Subsequent automotive, computer, and industrial applications extensively adopted this process technology, which enabled chip designers flexibly and reliably to combine power, analog, and digital signal processing.

IEEE里程碑獎(jiǎng)充分肯定了BCD技術(shù)的歷史貢獻(xiàn),對(duì)單片集成大功率器件、精確模擬功能和復(fù)雜數(shù)字邏輯控制的開創(chuàng)性研究成果表示高度認(rèn)可(IEEE Milestone plaque recognizes the pioneering work that enabled engineers to combine high-power components, precise analog functions, and the complex digital logic to control them onto a single piece of silicon, a capability that has now been sold in 40 billion chips)。

什么是BCD?

BCD(Bipolar-CMOS-DMOS)技術(shù)是一種單片集成工藝技術(shù),能夠在同一芯片上制作Bipolar、CMOS和DMOS器件,1985年由意法半導(dǎo)體率先研制成功。隨著集成電路工藝的進(jìn)一步發(fā)展,BCD工藝已經(jīng)成為PIC的主流制造技術(shù)。

來(lái)自ST官網(wǎng)

1950年代出現(xiàn)了適合生產(chǎn)模擬功能器件的雙極(Bipolar)工藝,雙極器件一般用于功率稍大的電路中,具有截止頻率高、驅(qū)動(dòng)能力大、速度快、噪聲低等優(yōu)點(diǎn),但其集成度低、體積大、功耗大。1960年代,出現(xiàn)了適合生產(chǎn)數(shù)字功能電路的CMOS(互補(bǔ)金屬氧化物半導(dǎo)體)工藝,CMOS器件具有集成度高、功耗低、輸入阻抗高等優(yōu)點(diǎn),驅(qū)動(dòng)邏輯門能力比其他器件強(qiáng)很多,也彌補(bǔ)了雙極器件的缺點(diǎn)。1970年代,出現(xiàn)了適合生產(chǎn)功率器件的DMOS(雙擴(kuò)散金屬氧化物半導(dǎo)體)工藝,DMOS功率器件具有高壓、大電流的特點(diǎn)。

BCD工藝把Bipolar器件、CMOS器件、DMOS功率器件同時(shí)制作在同一芯片上,綜合了雙極器件高跨導(dǎo)、強(qiáng)負(fù)載驅(qū)動(dòng)能力和CMOS集成度高、低功耗的優(yōu)點(diǎn),使其互相取長(zhǎng)補(bǔ)短,發(fā)揮各自的優(yōu)點(diǎn);同時(shí)DMOS可以在開關(guān)模式下工作,功耗極低。不需要昂貴的封裝和冷卻系統(tǒng)就可以將大功率傳遞給負(fù)載。低功耗是BCD工藝的一個(gè)主要優(yōu)點(diǎn)之一。BCD工藝可大幅降低功率耗損,提高系統(tǒng)性能,節(jié)省電路的封裝費(fèi)用,并具有更好的可靠性。

經(jīng)過(guò)35年的發(fā)展,BCD工藝已經(jīng)從第一代的4微米發(fā)展到了第九代的0.11微米,線寬尺寸不斷減小的同時(shí),也采用了更加先進(jìn)的多層金屬布線系統(tǒng),使得BCD工藝與純CMOS工藝發(fā)展差距縮小,目前的BCD工藝中的CMOS與純CMOS可完全兼容。另一方面,BCD工藝向著標(biāo)準(zhǔn)化模塊化發(fā)展,其基本工序標(biāo)準(zhǔn)化,混合工藝則由這些基本工序組合而成,設(shè)計(jì)人員可以根據(jù)各自的需要增減相應(yīng)的工藝步驟。

BCD首創(chuàng)者-意法半導(dǎo)體

1987年6月,意大利SGS微電子(SGS Microelettronica,始于1957年)和法國(guó)湯姆森半導(dǎo)體(Thomson Semiconducteurs,始于1962年)合并成立了意法半導(dǎo)體(SGS-Thomson Microelectronics),1998年5月英文名稱更名為STMicroelectronics。

1980年代初期,當(dāng)時(shí)的SGS微電子(SGS Microelettronica)的工程師為了解決各種電子應(yīng)用問(wèn)題,提出了一個(gè)革命性的構(gòu)想:

1)創(chuàng)造一種將晶體管和二極管集成在一顆芯片上的技術(shù),并能夠提供數(shù)百瓦功率;

2)用邏輯控制功率,實(shí)現(xiàn)方式需要遵循摩爾定律;

3)最大限度地降低功耗,從而消除散熱器;

4)支持精確的模擬功能;

5)以可靠的實(shí)現(xiàn)方式滿足廣泛的應(yīng)用需求。

1984年SGS的工程師成功將Bipolar/CMOS/DMOS/Diodes通過(guò)硅柵集成在一起。BCD首個(gè)器件是L6202電動(dòng)機(jī)全橋驅(qū)動(dòng)器,采用4微米技術(shù),12層光罩,工作電壓60V,電流1.5A,開關(guān)頻率300kHz,達(dá)到所有設(shè)計(jì)目標(biāo)。這個(gè)新的可靠工藝技術(shù)讓芯片設(shè)計(jì)人員能夠在單個(gè)芯片上靈活地集成功率、模擬和數(shù)字信號(hào)處理電路。

圖片來(lái)自ST官網(wǎng)

經(jīng)過(guò)35年的發(fā)展,意法半導(dǎo)體開發(fā)了一系列對(duì)全球功率IC影響深遠(yuǎn)的BCD工藝,如BCD3(1.2微米)、BCD4(0.8微米)、BCD5(0.6微米)。

意法半導(dǎo)體目前提供三種主要的BCD技術(shù),包括BCD6(0.35微米)/BCD6s(0.32微米)、BCD8(0.18微米)/BCD8s(0.16微米和BCD9(0.13微米)/BCD9s(0.11微米),其第十代BCD工藝將采用90納米。

BCD6和BCD8還提供SOI工藝選項(xiàng)。

據(jù)悉,意法半導(dǎo)體從1985年BCD推出工藝,至今已經(jīng)過(guò)去35年并經(jīng)歷了九次技術(shù)迭代,產(chǎn)出500萬(wàn)片晶圓,售出400億顆芯片,僅2020年就售出近30億顆芯片,第十代BCD技術(shù)即將開始投產(chǎn)。

國(guó)內(nèi)各晶圓制造公司BCD工藝情況

華虹半導(dǎo)體

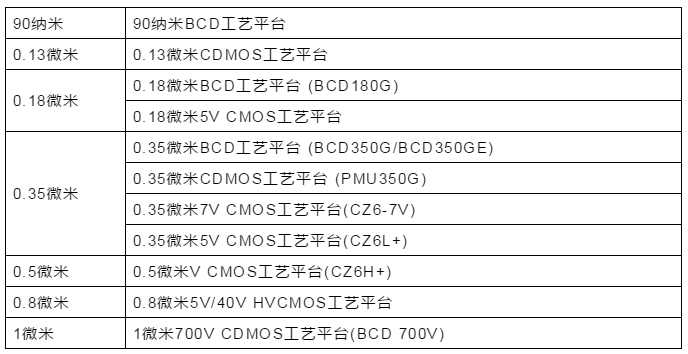

華虹半導(dǎo)體基于成熟的CMOS工藝平臺(tái),目前提供的BCD工藝平臺(tái)電壓涵蓋1.8V到700V,工藝節(jié)點(diǎn)涵蓋90納米/0.13微米/0.18微米/0.35微米/0.5微米/0.8微米/1.0微米,在0.5微米、0.35微米、0.18微米節(jié)點(diǎn)上積累了豐富的量產(chǎn)經(jīng)驗(yàn)。未來(lái),華虹半導(dǎo)體將繼續(xù)發(fā)揮在BCD和eNVM特色工藝上的技術(shù)優(yōu)勢(shì),提供二者的集成方案,為智能化電源產(chǎn)品,打造高端電源管理系統(tǒng)級(jí)芯片(SoC)。

2007年華虹半導(dǎo)體推出BCD350工藝平臺(tái)(0.35微米);2009年推出非外延PMU350工藝平臺(tái);2010年推出BCD180工藝平臺(tái)(0.18微米);2013年700V BCD工藝平臺(tái);2018年第二代BCD180工藝平臺(tái)推出;2020年5月90納米BCD工藝平臺(tái)在華虹無(wú)錫12英寸生產(chǎn)線順利實(shí)現(xiàn)產(chǎn)品投片,其LDMOS涵蓋5V至24V電壓段,也為未來(lái)65/55納米的12英寸工藝技術(shù)的研發(fā)與市場(chǎng)拓展打開了空間。

華虹半導(dǎo)體還將持續(xù)8英寸生產(chǎn)線的研發(fā)創(chuàng)新,優(yōu)化升級(jí)現(xiàn)有滿足車規(guī)要求的180納米BCD技術(shù),在相同的擊穿電壓下,導(dǎo)通電阻平均降低約25%,技術(shù)性能顯著提升,達(dá)到業(yè)界先進(jìn)水平,未來(lái)180納米BCD技術(shù)中的LDMOS的最高電壓由40V擴(kuò)展至100V。

華潤(rùn)微

華潤(rùn)微基于自有的主流工藝平臺(tái),在功率模擬工藝技術(shù)方面推出的BCD工藝解決方案,廣泛應(yīng)用于各新興市場(chǎng),包括電源管理、LED驅(qū)動(dòng)、汽車電子以及音頻電路等。

華潤(rùn)微的BCD工藝平臺(tái)始于2007年推出的700V CDMOS工藝,2011年推出700V HV BCD工藝,2013年完成600V HVIC工藝平臺(tái)研發(fā),到2020年一共完成了五代硅基700V HV BCD工藝的研發(fā)和量產(chǎn)。華潤(rùn)微BCD工藝平臺(tái)電壓涵蓋5V到700V,工藝節(jié)點(diǎn)涵蓋0.18微米/0.25微米/0.8微米/1.0微米,可滿足高電壓、高精度、高密度不同應(yīng)用的全方位需求,同步提供200-600V SOI基BCD工藝選項(xiàng)。

士蘭微

在BCD工藝技術(shù)平臺(tái)研發(fā)方面,士蘭微依托于5/6英寸、8英寸和12英寸晶圓生產(chǎn)線,建立了新產(chǎn)品和新工藝技術(shù)研發(fā)團(tuán)隊(duì)。

基于士蘭集成的5/6英寸生產(chǎn)線開發(fā)0.8微米和0.6微米的BCD電路工藝平臺(tái)已經(jīng)穩(wěn)定運(yùn)行15年,2007年1月士蘭微發(fā)布首款采用士蘭集成BCD工藝制造的高效率功率LED驅(qū)動(dòng)電路。

基于士蘭集昕8英寸生產(chǎn)線的0.25微米的BCD電路工藝平臺(tái)和0.18微米的BCD電路工藝平臺(tái)相繼建成,開始批量產(chǎn)出。

基于士蘭集科12英寸生產(chǎn)線BCD電路工藝平臺(tái)也在研制中。

中芯國(guó)際

中芯國(guó)際有超過(guò)10年的模擬芯片/電源管理芯片大規(guī)模生產(chǎn)經(jīng)驗(yàn),技術(shù)涵蓋了0.35微米到0.15微米。除了保持面向手機(jī)和消費(fèi)類電子的低壓BCD工藝平臺(tái)持續(xù)升級(jí)外,針對(duì)工業(yè)和汽車應(yīng)用的中高壓BCD平臺(tái)和車載BCD平臺(tái)也在開發(fā)中,同時(shí)開展了90納米BCD工藝平臺(tái)開發(fā),為高數(shù)字密度和低導(dǎo)通電阻的電源管理芯片提供解決方案。