近來,IMEC CMOS 器件技術(shù)總監(jiān) Naoto Horiguchi 和 imec 研究員兼 imec 納米互連項目總監(jiān) Zsolt Tokei 接受了采訪,談到了他們對1nm等先進(jìn)工藝實(shí)現(xiàn)方式的看法。

沿著擴(kuò)展路徑,他們展示了邏輯器件開發(fā)需要如何與在生產(chǎn)線后端引入創(chuàng)新并在越來越大的程度上在生產(chǎn)線中間引入創(chuàng)新齊頭并進(jìn)。

問:您如何看待未來幾年邏輯設(shè)備的擴(kuò)展?

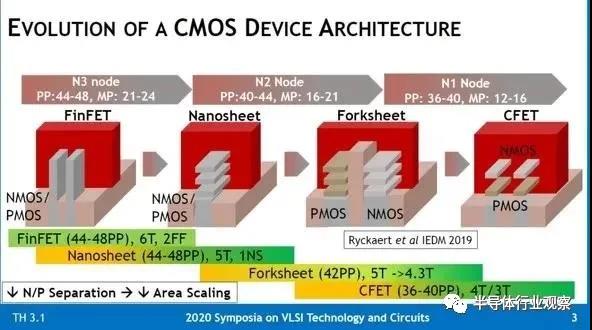

Naoto Horiguchi:大多數(shù) IDM 和代工廠最近都宣布從主流 FinFET 過渡到用于其 3nm 或 2nm 邏輯技術(shù)世代的環(huán)柵 (GAA) 納米片 FET 架構(gòu)。imec 的一項發(fā)明forksheet 結(jié)構(gòu)則可以延長這種納米片的生成。在forksheet之后,我們預(yù)計互補(bǔ) FET (CFET) 將進(jìn)入邏輯擴(kuò)展路線圖。“

”這些轉(zhuǎn)變將使我們能夠逐步推動標(biāo)準(zhǔn)單元在 4T 以下的軌道高度縮放,同時仍然提供功率性能優(yōu)勢。

除了 CFET,二硫化鎢 (WS 2 )等二維單層晶體材料有望替代 CMOS 溝道中的 Si,為進(jìn)一步縮小柵極長度提供機(jī)會。“

問:這些創(chuàng)新將如何影響B(tài)EOL?后端和MOL需要哪些發(fā)展才能跟上FEOL的擴(kuò)展?

Zsolt Tokei:”FEOL)的高級擴(kuò)展需要與BEOL)的創(chuàng)新齊頭并進(jìn),這就需要無縫連接到底層設(shè)備結(jié)構(gòu)的互連網(wǎng)絡(luò)。隨著 forksheet 架構(gòu)進(jìn)入路線圖,單元高度被推到 5T 以下,關(guān)鍵 BEOL 層中的金屬間距將變得小到 20nm 及以下。從電容、電阻(通孔和導(dǎo)線)以及成本、可印刷性和可靠性的角度來看,這都極具挑戰(zhàn)性——需要在設(shè)計、模塊和材料層面進(jìn)行創(chuàng)新。這推動了新互連集成方案的發(fā)展,例如混合通孔金屬化(解決通孔電阻增加)和半鑲嵌工藝流程——作為當(dāng)今主流銅雙鑲嵌工藝的替代品。半鑲嵌涉及金屬的直接蝕刻以獲得更高縱橫比的線條,并且可以包括間隙填充。

Naoto Horiguchi:“為了加強(qiáng)先進(jìn)邏輯器件縮放和互連開發(fā)之間的協(xié)同作用,MOL)活動開始發(fā)揮越來越重要的作用。將 BEOL 和 FEOL 連接在一起的 MOL 長期以來一直被組織為源極、漏極和柵極的單層接觸。

但向低于 5T 電池架構(gòu)的過渡推動了向多層 MOL 結(jié)構(gòu)的演變,其中添加了額外的層和通孔——類似于過去 BEOL 的演變方式。”

問:您的團(tuán)隊最近取得了哪些突破?

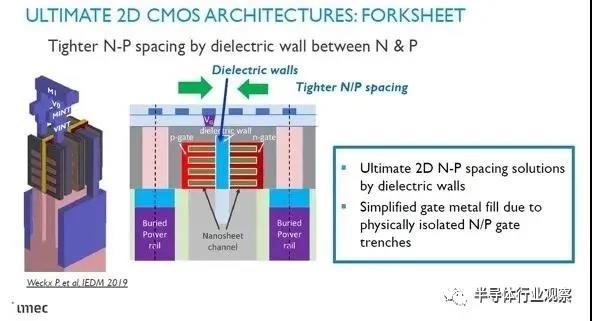

Naoto Horiguchi:“雖然forksheet器件架構(gòu)的面積和性能優(yōu)勢已經(jīng)通過 TCAD 模擬顯示出來,但我們現(xiàn)在首次展示了功能集成 forksheet的FET 器件的電氣特性——這一突破性成果將在 2021 VLSI 上得到強(qiáng)調(diào)。我們已經(jīng)展示了該架構(gòu)的關(guān)鍵模塊,包括介電壁和 17nm np 間距的替代金屬柵極圖案。盡管forksheet設(shè)備是三門設(shè)備架構(gòu),但在我們的工作中沒有觀察到靜電性能下降。”

問:從納米互連的角度來看,imec 正在探索哪些途徑來補(bǔ)充這一成就?

Zsolt Tokei:forksheet等擴(kuò)展納米片架構(gòu)需要新的 BEOL 集成方案,例如半鑲嵌,以實(shí)現(xiàn)低于 20 納米的金屬間距。同時,我們正在開發(fā)新的多層 MOL 布線方案,例如垂直-水平-垂直 (VHV) 方案。結(jié)合縮放增強(qiáng)器(例如自對準(zhǔn)觸點(diǎn)和埋入式電源軌 (BPR)),這些多層 MOL 方案將為在更小單元高度上實(shí)現(xiàn)更高效的單元內(nèi)布線鋪平道路。“

Naoto Horiguchi:”在 MOL 中實(shí)施多層工藝流程,結(jié)合諸如埋入式電源軌 (BPR) 之類的縮放助推器,這將在很大程度上增強(qiáng)我們基于forksheet的電池設(shè)計的可擴(kuò)展性,將軌道高度從 5T 推到 4T。因此,在 MOL 中引入semi-damascene是 FEOL、MOL 和 BEOL 活動之間cross-fertilization所帶來好處的另一個例子。“

問:您期望實(shí)現(xiàn)的下一個重要里程碑是什么?

Naoto Horiguchi:”在 forksheet 關(guān)鍵模塊和設(shè)備演示之后,我們的計劃重點(diǎn)將逐漸從 forksheet 轉(zhuǎn)移到 CFET。

CFET 架構(gòu)由于其許多自由度而很復(fù)雜。Imec 將量化功率性能面積 (PPA) 優(yōu)勢和 CFET 工藝流程的復(fù)雜性,并向我們的合作伙伴推薦最佳選擇。雖然納米片、forksheet和 CFET 架構(gòu)將逐漸將單元軌道高度降低到 4T 及以上,但我們正在探索替代器件架構(gòu),以解決接觸多節(jié)距 (CPP) 縮放速度放緩的問題,該接觸多節(jié)距 (CPP) 測量從一個晶體管的柵極接觸到相鄰設(shè)備上的柵極。“

Zsolt Tokei:”向 1nm CFET 系列邏輯器件的發(fā)展推動了新 BEOL 和 MOL 解決方案的開發(fā)。在 BEOL 中,我們早些時候提出了一種新的金屬化結(jié)構(gòu),稱為“零通孔混合高度”。在這個結(jié)構(gòu)中,每個金屬層現(xiàn)在被分成三個獨(dú)立的子層,這允許根據(jù)它們的應(yīng)用需要調(diào)整金屬線的高度和縱橫比(因此,電容的交換電阻)。

我們很高興報告第一次 SRAM 評估,確認(rèn)讀取速度(30%)和寫入余量(50%)顯著提高。目前,我們正在努力實(shí)現(xiàn)真正的邏輯單元布局。“

”從長遠(yuǎn)來看,我們需要通過引入新的導(dǎo)體來補(bǔ)充這些集成方案。感興趣的是具有比 Ru 或 Mo 更好的品質(zhì)因數(shù)的有序二元或三元化合物。我們已經(jīng)通過第一次 ab initio 模擬和初步實(shí)驗開拓了這一領(lǐng)域,現(xiàn)在我們正在與 imec 的材料研發(fā)小組密切合作,加強(qiáng)我們的活動。“

問:您希望芯片行業(yè)記住的關(guān)鍵信息是什么?

Naoto Horiguchi:”近年來,有一些人聲稱傳統(tǒng)的 CMOS 縮放已經(jīng)走到了盡頭。但是隨著許多創(chuàng)新的進(jìn)行,我們相信我們可以在至少未來十年內(nèi)繼續(xù)擴(kuò)大 CMOS 規(guī)模。Imec 是實(shí)現(xiàn)這一目標(biāo)的好地方。與合作伙伴的密切合作幫助我們應(yīng)對行業(yè)最大的挑戰(zhàn),并將邏輯器件擴(kuò)展到 1nm 技術(shù)之外——利用與 imec 的納米互連、Insite 和材料開發(fā)活動的緊密合作。“

Zsolt Tokei:”同樣從 BEOL 的角度來看,我們有許多有趣且有效的選擇,使我們能夠在未來十年解決 RC 延遲瓶頸和流水線互連。我們可以為我們的合作伙伴提供一個全面的路線圖,其中包含與未來邏輯器件縮放相關(guān)的廣泛選項,其中的元素可以重新用于存儲器開發(fā)。我們正在通過新的見解、改進(jìn)的集成方案和新材料不斷豐富這一路線圖——其中一些還將在 7 月份即將舉行的 IITC 會議上展示。“

2nm后,晶體管的新選擇

本周,在 2021 年 VLSI 技術(shù)和電路研討會 (VLSI 2021) 上,世界領(lǐng)先的納米電子和數(shù)字技術(shù)研究和創(chuàng)新中心 imec 首次展示了全功能集成forksheet場效應(yīng)晶體管 (FET)。據(jù)介紹,具有短溝道控制 (SSSAT=66-68mV/dec),可與低至 22nm 柵極長度的全環(huán)柵 (GAA) 納米片器件相媲美。雙功函數(shù)金屬柵極(Dual work function metal gates)以 17nm 間距集成在 n 和 pFET 之間,突出了 forksheet 器件在高級 CMOS 面積縮放方面的主要優(yōu)勢。

forksheet 器件最近被 imec 提出作為最有前途的器件架構(gòu),以擴(kuò)展 GAA 納米片器件的生成,并具有超出 2nm 技術(shù)節(jié)點(diǎn)的額外縮放和性能。與納米片器件不同,這些片現(xiàn)在由tri-gate forked結(jié)構(gòu)控制——通過在柵極圖案化之前在 p 和 nMOS 器件之間引入介電壁(dielectric wall )來實(shí)現(xiàn)。該壁將 p 柵極溝槽與 n 柵極溝槽物理隔離,允許比 FinFET 或納米片器件更緊密的 n 到 p 間距。早期基于 TCAD 模擬的技術(shù)評估顯示,這個晶體管擁有卓越的面積和性能可擴(kuò)展性。性能提升主要?dú)w因于減小的米勒電容——由更小的柵極-漏極重疊導(dǎo)致。

Imec 首次展示了其forksheet器件的電氣特性,該器件通過使用 300 毫米工藝流程成功集成,柵極長度低至 22 納米。發(fā)現(xiàn) n- 和 pFET 都具有兩個堆疊的硅通道,都具有完整的功能。它們的短通道控制 (SSSAT = 66-68mV) 與在同一晶片上共集成的垂直堆疊納米片器件的短通道控制相當(dāng)。對于 forksheet 器件,使用替代金屬柵極流在 17nm 的 np 空間(約為最先進(jìn)的 FinFET 技術(shù)中的間距的 35%)集成了雙功函數(shù)金屬柵極,突出了其中之一新設(shè)備架構(gòu)的主要優(yōu)勢。

”從 2022 年開始,預(yù)計今天的前沿 FinFET 晶體管將逐漸讓位于大批量制造中的垂直堆疊納米片晶體管,因為 FinFET 無法在縮放尺寸上提供足夠的性能,“ CMOS 設(shè)備總監(jiān) Naoto Horiguchi 解釋說imec 的技術(shù)。”然而,工藝限制將限制納米片的 n 和 p 器件可以組合在一起的距離,從而對進(jìn)一步降低電池高度構(gòu)成挑戰(zhàn)。新的 forksheet 器件架構(gòu)——GAA 納米片器件的自然演變——有望突破這一極限,允許軌道高度從 5T 縮放到 4.3T,同時仍提供性能增益。或者,通過叉板設(shè)計,可用空間可用于增加板寬度,從而進(jìn)一步增強(qiáng)驅(qū)動電流。

從Forksheet到CFET

在2019年的VLSI座談會上,imec表示將會把CFET應(yīng)用到5納米、3納米、2納米上,筆者就此向其中一位演講者提出:“imec計劃從哪個技術(shù)節(jié)點(diǎn)開始使用CFET”?得到了以下回答:“就此,目前imec還沒有達(dá)成一致意見”。

后來,imec在其內(nèi)部達(dá)成了以下共識:3納米之前采用Nanosheet、2納米采用Forksheet、1納米采用CFET。也就是說,在此次VLSI座談會上,imec的其他發(fā)言人,如Sujith Subramanian先生,也是基于以上技術(shù)藍(lán)圖而做的發(fā)表。(如下圖)

圖一

從上圖可以清晰地看出FinFET、Nanosheet、Forksheet、CFET的結(jié)構(gòu)變化。從FinFET到CFET,通過將Contact Poly Pitch(PP)做到最小、分離nMOS和pMOS,以達(dá)到縮小SRAM面積的效果。

在歷年的VLSI座談會上從未出現(xiàn)過Forksheet這中晶體管結(jié)構(gòu),今年是第一次,首先做成Nanosheet、然后用絕緣壁膜將其內(nèi)部分離,就能將nMOS和pMOS分離(如下圖),與其說將nMOS和pMOS的Nanosheet分離有意義,不如說工藝的削減更有意義。

圖2

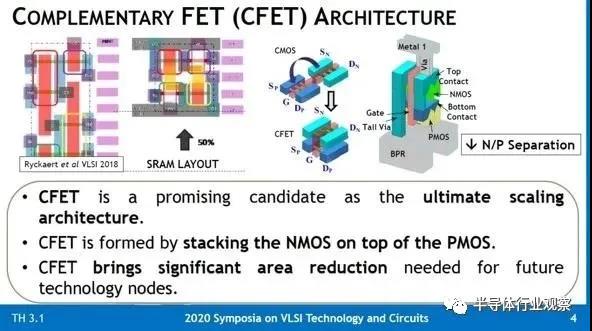

此外,在1納米中,采用了將nMOS和pMOS縱向排列的CFET(如下圖8),雖然CFET的工藝流程非常復(fù)雜,但毫無疑問,極大地縮小了CMOS、SRAM的面積,達(dá)到了集成化。問題是---是否做到了人們所期待的晶體管的特性,這是未來研發(fā)的關(guān)鍵。

圖3

1nm以后的晶體管選擇:CFET?

在VLSI 2020上,IMEC發(fā)表了有關(guān)單片CFET的有趣論文,我有機(jī)會采訪了其中一位作者Airoura Hiroaki。在業(yè)界眾所周知,F(xiàn)inFET(FF)即將達(dá)到其定標(biāo)壽命。三星已經(jīng)宣布,他們將在3nm的時候轉(zhuǎn)向水平納米片(Horizontal Nanosheets :HNS)。臺積電(TSMC)保持3nm的FF,但預(yù)計將轉(zhuǎn)移到2nm的新架構(gòu)。

假設(shè)英特爾當(dāng)時仍在追求自己的技術(shù),則預(yù)計英特爾將保留7nm的FF,然后再遷移至5nm的HNS。

該行業(yè)最可能的路線圖是從FF到帶有或不帶有Forksheets的HNS,然后過渡到CFET(Complimentary FETs),請參見圖1。

從以上技術(shù)藍(lán)圖來看,28納米使用了High-K/Metal Gate,16納米---14納米導(dǎo)入了FinFET,7納米---5納米采用了EUV曝光設(shè)備,此外,還將Co應(yīng)用于Middle of Line(MOL)上。

MOL是一種將晶體管(FOEL)與多層配線(BEOL)連接在一起的孔(Via),雖然imec使用了Co,還有其他選擇項如Mo、Ru等。

此外,4納米---3納米中采用了具有Nanosheet結(jié)構(gòu)的晶體管。

此次的VLSI座談會上,有關(guān)7納米、5納米、3納米的文章發(fā)布得比較多,然而,筆者卻發(fā)現(xiàn)將Gate All Around(GAA)的Nanosheet結(jié)構(gòu)應(yīng)用在這些節(jié)點(diǎn)上的情況是全球共通的認(rèn)知。

同時從技術(shù)藍(lán)圖看,在2納米中,使用搭載了Buried Power Rail(BPR,在晶體管下埋入電源線的構(gòu)造)的Forksheet晶體管;在1納米中,將會使用采用了BPR的Complementary FET(CFET)。

imec在其內(nèi)部達(dá)成了以下共識:3納米之前采用Nanosheet、2納米采用Forksheet、1納米采用CFET。

也就是說,在此次VLSI座談會上,imec也是基于以上技術(shù)藍(lán)圖而做的發(fā)表。從上圖可以清晰地看出FinFET、Nanosheet、Forksheet、CFET的結(jié)構(gòu)變化。

從FinFET到CFET,通過將Contact Poly Pitch(PP)做到最小、分離nMOS和pMOS,以達(dá)到縮小SRAM面積的效果。

Forksheet 和CFET通過堆疊nFET和pFET器件的CFET改善n到p的間距來縮小尺寸,見圖3。

CFET結(jié)構(gòu)在當(dāng)前的工作中,已經(jīng)開發(fā)了“單片”(monolithic) CFET,方法是將單獨(dú)的硅片用于nFET和pFET,然后將它們粘合在一起,而按照順序(sequential),CFET則會將兩種類型的FET都制造在同一硅片上。

Imec聲稱單片技術(shù)比順序技術(shù)便宜,而順序技術(shù)要求SOI會增加襯底成本1%。

片CFET的成本優(yōu)勢在1納米中,IMEC采用了將nMOS和pMOS縱向排列的CFET(如下圖8),雖然CFET的工藝流程非常復(fù)雜,但毫無疑問,極大地縮小了CMOS、SRAM的面積,達(dá)到了集成化。

問題是——是否做到了人們所期待的晶體管的特性,這是未來研發(fā)的關(guān)鍵。

我發(fā)現(xiàn)起始晶圓成本高出約1%,這有兩個原因,一是,我不相信順序CFET需要SOI,二是,SOI比標(biāo)準(zhǔn)晶圓貴了約1%。整體方法還將需要兩個起始晶圓,而不僅僅是一個。

我認(rèn)為這種成本分析需要更多的調(diào)查。在單片方法中,nFET和pFET在分離的晶圓上制造,從而可以針對該器件優(yōu)化每個器件的制造流程。

隨著我們朝N3方向發(fā)展,n到p的分離減少了寄生效應(yīng)并提高了性能。同樣,通過從FF移至GAA)可以在所有四個側(cè)面而不是三個側(cè)面上提供一個柵極,從而改善了靜電控制。

這項工作中制造的單片CFET為下一代器件提供了順序CFET的替代方案,需要進(jìn)一步研究。