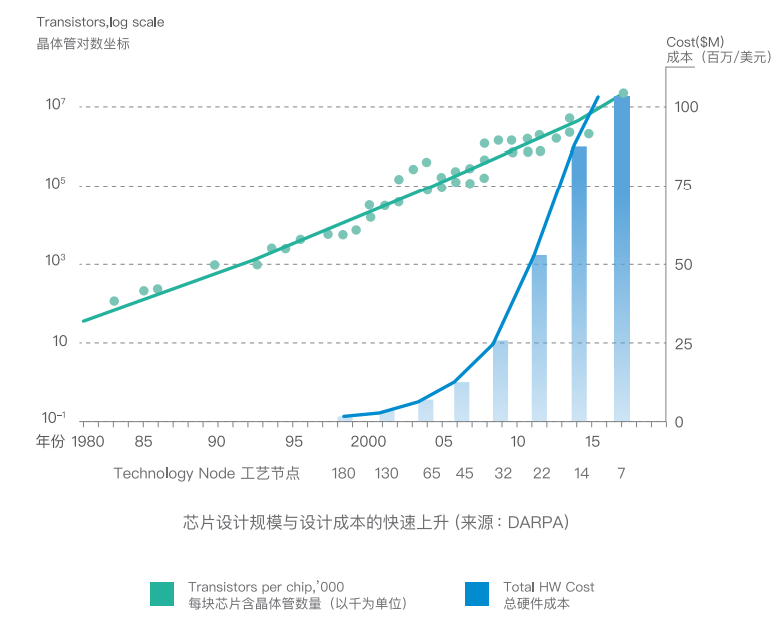

一顆芯片的誕生,要經(jīng)歷一段精雕細(xì)琢的漫長過程。在過去的幾十年里,芯片的工藝、規(guī)模跟隨著摩爾定律逐級躍遷,其內(nèi)部的復(fù)雜度、集成度也呈指數(shù)級增長。如今,芯片內(nèi)部集成的晶體管數(shù)量動輒數(shù)以億計,而微型化、輕量化的趨勢也讓芯片的設(shè)計難度大幅度增加。

摩爾定律逐漸達(dá)到物理極限,先進(jìn)工藝帶來的性能提升空間也隨之坍縮,迫使業(yè)界將目光轉(zhuǎn)向芯片的設(shè)計階段。芯片內(nèi)部結(jié)構(gòu)的設(shè)計對其能否流片成功起到?jīng)Q定性作用,而作為芯片設(shè)計最上游的產(chǎn)業(yè),EDA工具逐漸成為集成電路持續(xù)發(fā)展的重要支撐。

借助EDA工具,芯片設(shè)計公司通過搭建高精度仿真模型,不斷發(fā)現(xiàn)和排除先進(jìn)工藝在制造過程中可能產(chǎn)生的問題,求得芯片綜合性能、功耗、面積、成本等各方面最優(yōu)解的解決方案。然而,隨著應(yīng)用需求逐漸細(xì)化、工藝迭代紅利逐漸減少,EDA發(fā)展的步伐越來越跟不上芯片設(shè)計規(guī)模和需求的快速增長。在芯華章科技產(chǎn)品與業(yè)務(wù)規(guī)劃總監(jiān)楊曄看來,未來十年,集成電路的發(fā)展對EDA提出了更高的要求,為了進(jìn)一步提升設(shè)計和驗(yàn)證效率、降低技術(shù)門檻、縮短項(xiàng)目周期,EDA工具和方法學(xué)亟需創(chuàng)新和突破。

圖:芯華章科技產(chǎn)品與業(yè)務(wù)規(guī)劃總監(jiān)楊曄

后摩爾時代,EDA發(fā)展困局

集成電路發(fā)展初期,芯片設(shè)計還是手工繪制版圖。隨著計算機(jī)商業(yè)化加速,芯片集成度也在不斷提升,人工布線已經(jīng)無法滿足芯片設(shè)計需求。脫胎于CAD、CAE的概念,EDA逐漸開始商業(yè)化,進(jìn)入發(fā)展的黃金時期。

隨著芯片設(shè)計方法學(xué)逐漸演進(jìn)和革新,芯片工藝進(jìn)入到納米級別,規(guī)模和復(fù)雜度成倍增長。楊曄認(rèn)為,EDA 1.0正陷入后摩爾時代困局,面臨著新的挑戰(zhàn)。從市場應(yīng)用來看,日益細(xì)分的應(yīng)用場景給芯片設(shè)計造成了巨大的困難,EDA 1.0的設(shè)計周期和驗(yàn)證方法已經(jīng)無法支撐起下游市場的更迭速度。其次,復(fù)雜集成電路驗(yàn)證過程消耗的時間成本也隨之增加。據(jù)業(yè)界統(tǒng)計,芯片制造過程中70%的時間成本都會消耗在驗(yàn)證上。充分的驗(yàn)證是芯片成功流片的前提,但依賴于工程師經(jīng)驗(yàn)的驗(yàn)證無論在覆蓋率還是容錯率上都無法得到保障。

圖源:芯華章

另一方面,先進(jìn)工藝開發(fā)投入的IP成本逐漸增加,IP模塊的復(fù)用價值被削弱。語言、接口和數(shù)據(jù)標(biāo)準(zhǔn)化和開放性不足,導(dǎo)致EDA工具嚴(yán)重碎片化,影響EDA流程的自動化、智能化發(fā)展。此外,楊曄還指出,EDA的開發(fā)與應(yīng)用都需要強(qiáng)大的數(shù)學(xué)理論支撐,行業(yè)壁壘高,芯片設(shè)計人才稀缺,這也致使國產(chǎn)EDA發(fā)展緩慢甚至停滯不前。

打通芯片設(shè)計驗(yàn)證“任督二脈”

他山之石,可以攻玉。如前所述,EDA 1.0已經(jīng)無法滿足市場需求,亟需破局的鑰匙。借鑒應(yīng)用軟件開發(fā)的發(fā)展經(jīng)驗(yàn),芯華章已經(jīng)找到了那把突出重圍的鑰匙。楊曄表示,EDA 2.0彌補(bǔ)了前代的弊端和不足,實(shí)現(xiàn)了自動化、智能化的芯片設(shè)計及驗(yàn)證流程,為客戶提供快速、專業(yè)、靈活的芯片設(shè)計服務(wù),是后摩爾時代芯片設(shè)計發(fā)展的未來方向。

那么如何解決設(shè)計難、人才少、周期長、成本高等問題,實(shí)現(xiàn)EDA 1.0至EDA 2.0的演進(jìn),芯華章給出了三條關(guān)鍵路徑:

開放和標(biāo)準(zhǔn)化

EDA 2.0增強(qiáng)了芯片設(shè)計流程各個環(huán)節(jié)的開放程度,包括軟件API接口、數(shù)據(jù)格式和數(shù)據(jù)訪問接口等;EDA軟件也對更多硬件平臺開放;芯片內(nèi)外部總線和接口趨于標(biāo)準(zhǔn)化;商業(yè)EDA和開源EDA相結(jié)合;IP模塊也更加開放和便捷。

自動化和智能化

以開放和標(biāo)準(zhǔn)化為前提,EDA 2.0縮減了芯片架構(gòu)在設(shè)計、驗(yàn)證、布局等流程中的人力投入,采用高度并行化的設(shè)計工具,結(jié)合過去的設(shè)計經(jīng)驗(yàn)和數(shù)據(jù),在設(shè)計需求分析、芯片架構(gòu)探索、設(shè)計生成、物理設(shè)計及驗(yàn)證階段進(jìn)行數(shù)據(jù)模型化仿真,實(shí)現(xiàn)芯片設(shè)計全流程自動化,提高芯片設(shè)計效率。

平臺化和服務(wù)化

EDA工具與云端軟硬件生態(tài)相結(jié)合,對軟硬件框架和算法進(jìn)行創(chuàng)新、融合和重構(gòu),優(yōu)化用戶服務(wù)。芯華章打造了基于云原生軟件架構(gòu)的全新服務(wù)平臺EDaaS,深度利用云端彈性功能,為客戶提供近乎無限的計算彈性和更優(yōu)化的使用模式。

芯片設(shè)計離不開EDA工具,而EDA 2.0降低了EDA工具的使用門檻和芯片設(shè)計門檻,縮減了設(shè)計周期,讓芯片設(shè)計更加簡單便捷。楊曄表示,芯華章以智能調(diào)試、智能編譯、智能驗(yàn)證為三大基座,提供硬件仿真系統(tǒng)、FPGA原型驗(yàn)證系統(tǒng)、智能驗(yàn)證、形式驗(yàn)證及邏輯仿真等五大產(chǎn)品線,全面覆蓋數(shù)字芯片驗(yàn)證需求,為芯片打通設(shè)計與驗(yàn)證的“任督二脈”。

國產(chǎn)EDA如何破局

EDA發(fā)展三十余年,Cadence(楷登電子)、Synopsys(新思科技)和西門子旗下的Mentor Graphics占據(jù)了全球超60%的市場份額。2020年國內(nèi)EDA市場規(guī)模為66.2億元,而海外三巨頭就占據(jù)了80%以上,留給國產(chǎn)自主EDA企業(yè)的份額極其有限。

作為集成電路的上游支撐,EDA工具的重要性不言而喻。楊曄表示,EDA是數(shù)字化時代的底層關(guān)鍵技術(shù),目前,國產(chǎn)EDA在數(shù)字驗(yàn)證仿真等環(huán)節(jié)依然存在短板,產(chǎn)業(yè)鏈脆弱,因此在中國建立完善的集成電路產(chǎn)業(yè)鏈迫在眉睫。

國家政策支持下,對集成電路的重視和支持力度加大,整個產(chǎn)業(yè)鏈發(fā)展持續(xù)向好。隨著汽車、工業(yè)、醫(yī)療、教育等領(lǐng)域逐漸趨于自動化、網(wǎng)絡(luò)化,集成電路產(chǎn)業(yè)迎來了發(fā)展的爆發(fā)期,擁有龐大的市場空間和發(fā)展機(jī)遇。面對EDA產(chǎn)業(yè)機(jī)遇,芯華章等眾多企業(yè)協(xié)同產(chǎn)業(yè)鏈專業(yè)人士,積極吸納行業(yè)頂尖人才,培養(yǎng)新生代技術(shù)儲備力量,共同推動EDA 2.0的演進(jìn)。

從科技革命角度來看,軟件定義芯片的時代已經(jīng)到來。人工智能、云計算等技術(shù)飛速發(fā)展,集成電路正在尋求新的突破口,而國產(chǎn)EDA技術(shù)也已經(jīng)踏上新賽道,逐步構(gòu)建算力、算法和數(shù)據(jù)深度融合的數(shù)字化系統(tǒng)全新生態(tài),打造本土EDA核心競爭力。