由“摩爾定律”驅動的芯片集成度和復雜度持續(xù)提升,將為EDA工具發(fā)展帶來新需求。EDA作為串聯(lián)整個集成電路產業(yè)的根技術,市場空間巨大:賽迪智庫的數(shù)據(jù)顯示,近幾年全球EDA工具總銷售額保持上漲,2020年總銷售額72.4億美元,同比增長10.7%,分地區(qū)來看,北美約占全球EDA銷售額的40.9%,亞太地區(qū)占42.1%,歐洲地區(qū)約占17%。如何提供EDA工具協(xié)助,使得在更短的開發(fā)周期內完成更復雜的設計和驗證?

上海國微思爾芯技術股份有限公司(下稱“國微思爾芯”)是一家全球領先的EDA原型驗證解決方案供應商,國微思爾芯首席執(zhí)行官與總裁林俊雄是硬件加速ASIC/SoC設計方法的積極倡導者,他投身在促進可擴展的原型/仿真硬件架構和定義自動化軟件規(guī)范上。探索科技(techsugar)EDA專題邀請到林俊雄,來共同探討從驗證到數(shù)字EDA全流程,EDA工具和封裝技術有哪些優(yōu)化芯片設計流程、提高芯片設計效率的新技術風向。

后摩爾時代,發(fā)力封裝、擁抱AI

后摩爾時代的集成電路技術演進方向主要包括延續(xù)摩爾定律(More Moore)、擴展摩爾定律(More than Moore)以及超越摩爾定律(Beyond Moore)三類,主要發(fā)展目標涵蓋了建立在摩爾定律基礎上的生產工藝特征尺寸的進一步微縮、以增加系統(tǒng)集成的多重功能為目標的芯片功能多樣化發(fā)展,以及通過三維封裝(3D Package)、系統(tǒng)級封裝(SiP)等方式實現(xiàn)器件功能的融合和產品的多樣化。

國微思爾芯認為,先進封裝提供了高帶寬的裸片到裸片(Die-to-Die)互聯(lián),這是的一種延續(xù)摩爾定律方法。先進封裝通過平面上的小芯片(chiplet)互連,甚至3D Chiplet互連,來實現(xiàn)更高邏輯密度的芯片。但隨之而來的是更大的挑戰(zhàn),芯片的設計必須適應不同IP、不同Chiplet組合的復雜產品形態(tài),新的芯片設計也必須快速和原有Chiplet IP良好協(xié)同工作。針對此類需求,EDA業(yè)內提出了混合異構驗證方法,成熟的Chiplet,RTL-Ready IP,System Modeling IP可以在一個系統(tǒng)中同時建模驗證,并發(fā)揮Chiplet、RTL-Ready IP的高速優(yōu)勢,也支持System Modeling IP的靈活配置功能。

人工智能技術將在EDA領域扮演更重要角色。人工智能等對于計算效率和能效比提出更高要求,對應應用隨之成為半導體行業(yè)的主流推動引擎,異構化的設計也在成為主流。不同的運算單元有不同的架構設計,對信息流也有不同的處理方式,需要針對其特性使用不同驗證的方法學。

對于異構芯片設計驗證的需求,國微思爾芯提出基于驗證云系統(tǒng)的統(tǒng)一驗證平臺,平臺融合架構設計、原型驗證等不同解決方案,以期實現(xiàn)高效快速驗證。據(jù)林俊雄介紹,該平臺上的解決方案采用了統(tǒng)一的編譯/控制腳本和核心數(shù)據(jù)庫,芯片開發(fā)者可以在項目生命周期的不同階段選擇最適合的解決方案,并隨著項目的開發(fā)進展平滑遷移到更優(yōu)的解決方案,減少切換成本。此外,利用統(tǒng)一驗證平臺還可以確保各個階段的驗證任務在同一個環(huán)境中完成。

良好生態(tài)與設計方法學輔助平抑成本

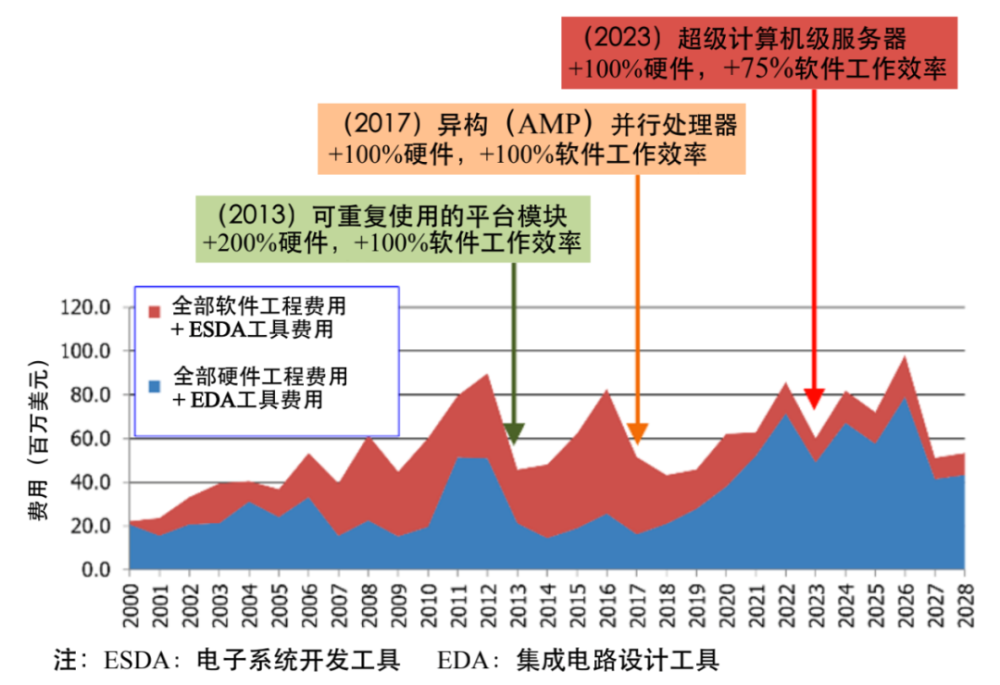

半導體工藝每更新一次,EDA軟件就要隨之更新,例如從7nm到5nm,客戶為了跟上半導體先進工藝便需要重新購買。在先進工藝開發(fā)過程中,IP成本也在日益增加,如何去平抑IP成本?

林俊雄表示,EDA公司更加強化構筑產業(yè)生態(tài)系,例如成立國產IP聯(lián)盟和共同開發(fā)更敏捷的IP評估平臺。先進工藝的芯片設計集成了更多的IP,如中央處理單元(CPU)、圖形處理單元(GPU)、人工智能加速器和高速接口,這些都需要相對應的驗證VIP來確保芯片的正確性和接口的相容性。林俊雄表示,為了順應IP/VIP成本日漸提高的趨勢,EDA公司與IP公司需要共同著力于建立EDA/IP合作生態(tài)系,開發(fā)敏捷的設計驗證環(huán)境來協(xié)助客戶縮短芯片設計周期,加速產品上市。

據(jù)業(yè)界統(tǒng)計,芯片制造過程中70%的時間成本都會消耗在驗證上。而AI、5G、智能汽車、云服務器等領域,對芯片的性能要求越來越高,芯片設計朝著更復雜更大型的方向發(fā)展,給驗證帶來更大的挑戰(zhàn)。

為應對大型設計的驗證挑戰(zhàn),國微思爾芯于2020年底推出高密原型驗證解決方案,產品單機柜高達64顆FPGA,支持多層次組網,可拓展至幾十億ASIC門容量。今年5月,國微思爾芯發(fā)布“Genesis 芯神匠”架構設計軟件,提供一站式軟硬件協(xié)同建模平臺,幫助設計師徹底解決無法建模的難題;“Genesis 芯神匠”搭配芯神瞳原型驗證平臺,利用既有IP精準的建模仿真,快速設計出高效能、低功耗的產品架構。

國產以市場區(qū)隔與產品差異破局

EDA是壁壘高筑的一環(huán),EDA國產化是一條難而正確的道路。三十多年,EDA三大巨頭(Synopsys、Cadence與西門子的Mentor)不間斷投入資源進行研發(fā)、兼并整合,營造出十分成功的產業(yè)生態(tài),使得客戶依賴度極高,從而形成今天市場寡頭壟斷的局面。國產EDA在三座大山的籠罩下,難以發(fā)展自身實力,無法獨立支撐信息產業(yè)的安全;另一方面,設計公司在權衡切換EDA平臺所帶來的成本和潛在風險時,顧慮重重。

國內外產業(yè)發(fā)展至今,差距已如溝壑難填,在林俊雄看來,主要原因是中國沒有在EDA領域持續(xù)投入資源,去不斷研發(fā)和構建市場生態(tài),這才喪失了在全球EDA領域逐鹿的機會。他表示,國內EDA產業(yè)的發(fā)展除了延續(xù)三大巨頭的模式之外,還需不斷通過創(chuàng)新,引入新的方法學,融入如“AI”等前沿技術,打造自己的競爭能力。此外,混合異構的芯片驗證環(huán)境建置、支持芯片的架構探索、效能分析和軟硬件的協(xié)同驗證,是值得設計公司重點研發(fā)之處,可以幫助國產公司在激烈競爭的半導體市場中做出市場區(qū)隔和產品差異化。

中國半導體產業(yè)的繁榮發(fā)展切實給國內EDA公司帶來大量機會,而國內尚未發(fā)育出可以提供給客戶全流程平臺的企業(yè),這造成需求與供給能力之間巨大的差距。林俊雄提倡企業(yè)正視國內外差異,在技術研發(fā)和支持方面持續(xù)投入,努力彌合供需之間的巨大差距,以更前沿的方法學、更有效地提供即時技術支持和異地協(xié)同開發(fā)能力來吸引國內客戶。

同時,林俊雄還表示,國微思爾芯期望攜手國內客戶共同建立國內EDA產業(yè)生態(tài),推進半導體產業(yè)鏈各個環(huán)節(jié)的協(xié)同發(fā)展。與很多其他行業(yè)相比,半導體行業(yè)是走在全球化最前端的,全球化的程度也最為深入。林俊雄評價到,全球化市場割裂的提法是政治需求而不是產業(yè)需求,產業(yè)應該做全球化、全球合作的積極推動者。