自Pat Gelsinger回歸并就任Intel CEO之后,這家芯片巨頭便走上了快車道,并多線快下,力爭(zhēng)領(lǐng)先。

在今日舉辦的Inel Accelerated大會(huì)上,Pat Gelsinge和他所領(lǐng)導(dǎo)的技術(shù)團(tuán)隊(duì)不但分享了公司在工藝上的路線圖,同時(shí)還談到了公司在封裝、晶圓代工,甚至還有公司在EUV工藝上的規(guī)劃。

現(xiàn)在,我們綜合我們Intel領(lǐng)導(dǎo)層所講的一些內(nèi)容,以及外媒報(bào)道的一些精華,以饗讀者。

工藝路線圖:4nm、3nm、20A和18A

正如Pat Gelsinger在演講中所說(shuō),最初,制程工藝“節(jié)點(diǎn)”的名稱與晶體管的柵極長(zhǎng)度相對(duì)應(yīng),并以微米為度量單位。隨著晶體管越變?cè)叫。瑬艠O的長(zhǎng)度越來(lái)越微縮,我們開(kāi)始以納米為度量單位。

他接著說(shuō),在過(guò)去多年的發(fā)展中,英特爾在工藝制程上面有過(guò)很多的貢獻(xiàn)。例如在1997年,英特爾推出了應(yīng)變硅(strained silicon)技術(shù),在加上其他技術(shù)方面的創(chuàng)新,進(jìn)而持續(xù)縮小晶體管,讓它們更快、更便宜和更高能效也變得同樣重要。

“從這時(shí)開(kāi)始,傳統(tǒng)命名方法不再與實(shí)際的晶體管的柵極長(zhǎng)度相匹配。”Pat Gelsinger強(qiáng)調(diào)。

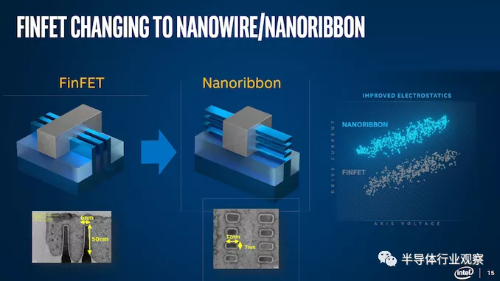

來(lái)到2011年,在英特爾也率先推出FinFET技術(shù)。這是一種構(gòu)建晶體管的全新方式,具有獨(dú)特的形狀和結(jié)構(gòu)。正是得益于這種創(chuàng)新性的技術(shù),摩爾定律繼續(xù)生效,但Pat Gelsinger卻表示,伴隨著這種技術(shù)的出現(xiàn),行業(yè)進(jìn)一步分化。

在Pat Gelsinger看來(lái),包括英特爾在內(nèi)整個(gè)行業(yè)使用著各不相同的制程節(jié)點(diǎn)命名和編號(hào)方案,這些多樣的方案既不再指代任何具體的度量方法,也無(wú)法全面展現(xiàn)該如何實(shí)現(xiàn)能效和性能的最佳平衡。

“為此,英特爾想要更新自己的命名體系,以創(chuàng)建一個(gè)清晰、一致和有意義的框架,來(lái)幫助我們的客戶對(duì)整個(gè)行業(yè)的制程節(jié)點(diǎn)演進(jìn)有一個(gè)更準(zhǔn)確認(rèn)知,進(jìn)而做出更明智的決策。”Pat Gelsinger強(qiáng)調(diào)。

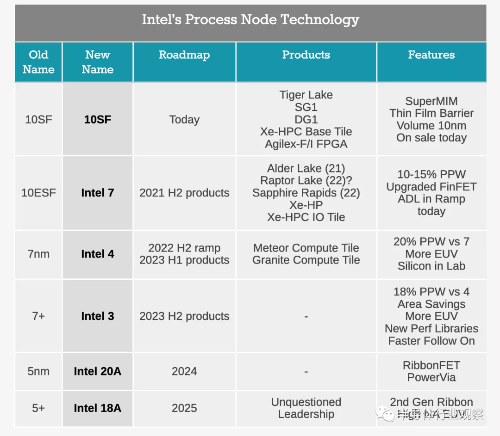

基于這個(gè)思路,繼去年推出英特爾有史以來(lái)最為強(qiáng)大的單節(jié)點(diǎn)內(nèi)性能增強(qiáng)的10納米SuperFin節(jié)點(diǎn)后,英特爾又推出了下一個(gè)節(jié)點(diǎn)——我們之前稱它為Enhanced SuperFin——現(xiàn)在更名為Intel 7、緊隨其后的是Intel 4和Intel 3。繼Intel 3之后的那個(gè)節(jié)點(diǎn),英特爾將其命名為20A,而不是大家以為的Intel 1。

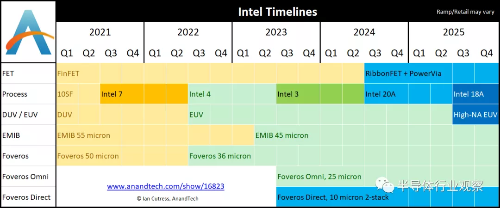

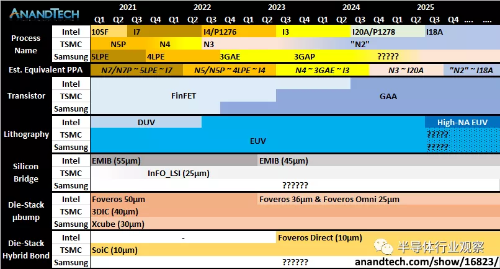

而據(jù)外媒anandtech的報(bào)道,英特爾在工藝方面也繼承了過(guò)往的一些傳統(tǒng)。如下圖所示,英特爾對(duì)用于生產(chǎn)(production)和進(jìn)入零售(retail)之間是有區(qū)別的;英特爾將某些技術(shù)稱為“準(zhǔn)備就緒”(being ready),而其他技術(shù)則稱為“加速”(ramping‘),因此這個(gè)時(shí)間表只是提到的那些日期。正如您想象的那樣,每個(gè)工藝節(jié)點(diǎn)都可能存在數(shù)年,此圖只是展示了英特爾在任何給定時(shí)間的領(lǐng)先技術(shù)。

綜合可見(jiàn),英特爾的詳細(xì)規(guī)劃和時(shí)間如下所示:

2020 年,10nm SuperFin (10SF):該工藝已經(jīng)實(shí)現(xiàn)大批量量產(chǎn):基于該工藝制造的Tiger Lake 和英特爾的 Xe-LP 獨(dú)立顯卡解決方案(SG1、DG1)已經(jīng)推出;

2021 H2,Intel 7:這個(gè)節(jié)點(diǎn)以前稱為 10nm Enhanced Super Fin 或 10ESF。Alder Lake (正在批量生產(chǎn))和 Sapphire Rapids 都屬于這一代工藝的產(chǎn)品,由于晶體管優(yōu)化,這代工藝的每瓦性能比 10SF 提高 10-15%。此外,英特爾的 Xe-HP 現(xiàn)在將被稱為英特爾 7 產(chǎn)品。

2022 H2,Intel 4:這個(gè)接在在以前稱為 Intel 7nm。英特爾今年早些時(shí)候表示,其 Meteor Lake 處理器將使用基于該工藝節(jié)點(diǎn)技術(shù)的計(jì)算塊,現(xiàn)在該芯片已返回實(shí)驗(yàn)室進(jìn)行測(cè)試。英特爾預(yù)計(jì),在這個(gè)節(jié)點(diǎn)下,芯片每瓦性能比上一代提高 20%,并且該技術(shù)使用更多 EUV,主要用于 BEOL。英特爾的下一個(gè)至強(qiáng)可擴(kuò)展產(chǎn)品 Granite Rapids 也將使用Intel 4進(jìn)行生產(chǎn)。需要強(qiáng)調(diào)一下,Intel 4是英特爾首個(gè)完全采用極紫外光刻(EUV)技術(shù)的制程節(jié)點(diǎn);

2023 H2,Intel 3:以前稱為英特爾 7+。增加 EUV 和新高密度庫(kù)的使用。這就是英特爾的戰(zhàn)略變得更加模塊化的地方——Intel 3 將共享Intel 4 的一些特性,但足夠新來(lái)描述這個(gè)新的完整節(jié)點(diǎn),特別是新的高性能庫(kù)。盡管如此,預(yù)計(jì)會(huì)很快跟進(jìn)。EUV 使用的另一個(gè)進(jìn)步是,英特爾預(yù)計(jì) 2023 年下半年的制造量將增加,其每瓦性能比Intel 4 提高 18%。

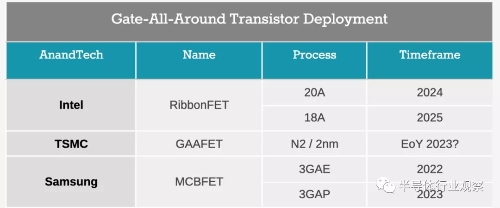

2024 年,Intel 20A:以前稱為 Intel 5nm。但新的路想吐轉(zhuǎn)向兩位數(shù)命名,A 代表 ?ngstr?m,或 10A 等于 1nm。關(guān)于這個(gè)節(jié)點(diǎn)有很少細(xì)節(jié),但在這個(gè)節(jié)點(diǎn),英特爾將從 FinFET 轉(zhuǎn)向其稱為 RibbonFET 的 Gate-All-Around (GAA) 晶體管。此外,英特爾還將推出一種新的 PowerVia 技術(shù)。

2025年,Intel 18A:這在上圖中未列出,但I(xiàn)ntel預(yù)計(jì)2025年會(huì)有18A工藝。18A將使用ASML最新的EUV機(jī)器,稱為High-NA機(jī)器,能夠進(jìn)行更精確的光刻。英特爾表示,它是 ASML 在 High-NA 方面的主要合作伙伴,并準(zhǔn)備接收 High-NA 機(jī)器的第一個(gè)機(jī)器。ASML 最近宣布 High-NA 被推遲——當(dāng)被問(wèn)及這是否是一個(gè)問(wèn)題時(shí),英特爾表示不會(huì),因?yàn)?High-NA 和 18A 的時(shí)間表是英特爾希望交叉并具有無(wú)可置疑的領(lǐng)導(dǎo)地位的地方。

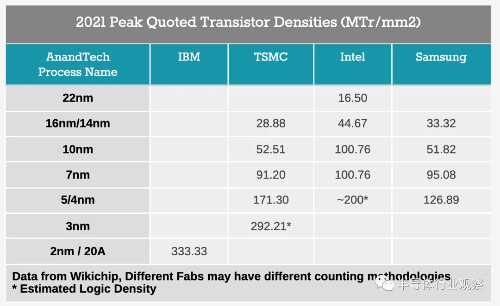

在談到英特爾為何重命名節(jié)點(diǎn)的時(shí)候,anandtech強(qiáng)調(diào),當(dāng)中的一個(gè)要素是他們要與其他代工廠產(chǎn)品匹配。英特爾的競(jìng)爭(zhēng)對(duì)手臺(tái)積電和三星都使用較小的數(shù)字來(lái)比較類似的密度工藝。隨著英特爾現(xiàn)在更名,他們與行業(yè)更加一致。話雖如此,anandtech暗示,英特爾的 4nm 可能與臺(tái)積電的 5nm 相提并論。到 3nm 我們預(yù)計(jì)會(huì)有一個(gè)很好的平價(jià)點(diǎn),但這將取決于英特爾與臺(tái)積電的發(fā)布時(shí)間表相匹配。

需要注意的一個(gè)關(guān)鍵點(diǎn)是,新的 Intel 7 節(jié)點(diǎn)(以前稱為 10ESF 節(jié)點(diǎn))不一定是我們通常理解的“完整”節(jié)點(diǎn)更新。該節(jié)點(diǎn)是作為 10SF 的更新派生而來(lái)的,如上圖所示,將具有“晶體管優(yōu)化”。從 10nm 到 10SF,這意味著SuperMIM和新的thin film設(shè)計(jì)提供了額外的 1 GHz+,但是從 10SF 到新的 Intel 7 的確切細(xì)節(jié)目前尚不清楚。然而,英特爾表示,從Intel 7 遷移到Intel 4 將是一個(gè)常規(guī)的全節(jié)點(diǎn)跳躍,Intel 3 使用Intel 4 的模塊化部分以及新的高性能庫(kù)和芯片改進(jìn),以實(shí)現(xiàn)性能的另一次跳躍。

詢問(wèn)英特爾這些工藝節(jié)點(diǎn)是否會(huì)有額外的優(yōu)化點(diǎn)時(shí),英特爾回應(yīng)道,它們中的任何一個(gè)是否會(huì)被明確地產(chǎn)品化將取決于特性。個(gè)別優(yōu)化可能會(huì)額外增加 5-10% 的每瓦性能,我們被告知,即使 10SF(保留其名稱)也有幾個(gè)額外的優(yōu)化點(diǎn),但不一定公開(kāi)。因此,這些更新是否以 7+ 或 7SF 或 4HP 的形式銷售尚不清楚,但與任何制造過(guò)程一樣,隨著更新的發(fā)生以幫助提高性能/功率/產(chǎn)量,假設(shè)設(shè)計(jì)遵循相同的規(guī)則,它們就會(huì)被應(yīng)用。

“最后這個(gè)命名(20A)反映了摩爾定律仍在持續(xù)生效。隨著越來(lái)越接近”1納米“節(jié)點(diǎn),我們將采用更能反映新時(shí)代的命名,即在原子水平上制造器件和材料的時(shí)代——半導(dǎo)體的埃米時(shí)代。”Pat Gelsinger說(shuō)。他進(jìn)一步指出,對(duì)于未來(lái)十年走向超越“1納米”節(jié)點(diǎn)的創(chuàng)新,英特爾有著一條清晰的路徑。

在Pat Gelsinger看來(lái),在窮盡元素周期表之前,摩爾定律都不會(huì)失效,英特爾將持續(xù)利用硅的神奇力量不斷推進(jìn)創(chuàng)新。英特爾的最新命名體系,是基于我們客戶看重的關(guān)鍵技術(shù)參數(shù)而提出的,即性能、功率和面積。

但Anandtech指出,這里的問(wèn)題之一是工藝節(jié)點(diǎn)準(zhǔn)備就緒(ready)、產(chǎn)品發(fā)布的生產(chǎn)量增加(ramping production)和實(shí)際可用之間( available)的區(qū)別。例如,Alder Lake(現(xiàn)在采用英特爾 7nm)將于今年問(wèn)世,但 Sapphire Rapids 將更多地成為 2022 年的產(chǎn)品。同樣,有報(bào)道稱,英特爾 7 上的 Raptor Lake 將于 2022 年推出,以在 2023 年用英特爾 4 上的平鋪 Meteor Lake 取代 Alder Lake。雖然英特爾很高興討論工藝節(jié)點(diǎn)開(kāi)發(fā)時(shí)間框架,但產(chǎn)品時(shí)間框架并不開(kāi)放(如毫無(wú)疑問(wèn),如果錯(cuò)過(guò)了規(guī)定的時(shí)間,客戶會(huì)感到沮喪)。

兩大創(chuàng)新性技術(shù):RibbonFET和PowerVia

在演講中,英特爾的全球技術(shù)開(kāi)發(fā)團(tuán)隊(duì)負(fù)責(zé)人Ann Kelleher博士表示,公司將于2024年上半年推出的Intel 20A會(huì)成為制程技術(shù)的又一個(gè)分水嶺。它擁有兩大開(kāi)創(chuàng)性技術(shù)——RibbonFET的全新晶體管架構(gòu),名為PowerVia的史無(wú)前例的創(chuàng)新技術(shù),可優(yōu)化電能傳輸。

如上文所說(shuō),轉(zhuǎn)向 20A 時(shí),英特爾的工藝名稱指的是埃而不是納米。也就是在這個(gè)時(shí)刻,英特爾將從其 FinFET 設(shè)計(jì)過(guò)渡到一種新型晶體管,稱為 Gate-All-Around 晶體管或 GAAFET。在英特爾的案例中,他們?yōu)槠浒姹咎峁┑臓I(yíng)銷名稱是 RibbonFET。

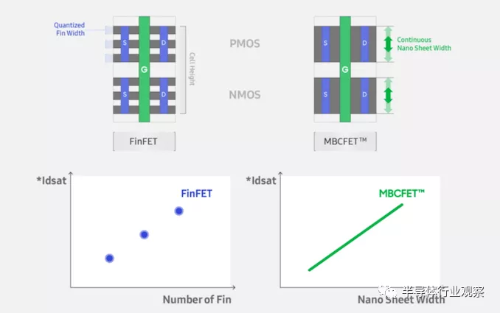

人們普遍預(yù)計(jì),一旦標(biāo)準(zhǔn) FinFET 失去動(dòng)力,半導(dǎo)體制造行業(yè)將轉(zhuǎn)向 GAAFET 設(shè)計(jì)。每個(gè)領(lǐng)先的供應(yīng)商都稱他們的實(shí)現(xiàn)方式不同(RibbonFET、MCBFET),但它們都使用相同的基本原理——具有多個(gè)層的靈活寬度晶體管幫助驅(qū)動(dòng)晶體管電流。FinFET 依賴于源極/漏極的多個(gè)量化鰭片和多個(gè)鰭片軌跡的單元高度,而 GAAFET 支持可變長(zhǎng)度的單個(gè)鰭片,從而允許在功率、性能或面積方面優(yōu)化每個(gè)單獨(dú)單元器件的電流。

多年來(lái),英特爾一直在半導(dǎo)體技術(shù)會(huì)議上討論 GAAFET,在 2020 年 6 月的國(guó)際 VLSI 會(huì)議上,時(shí)任Intel CTO的 Mike Mayberry 博士展示了一張圖表,其中包含轉(zhuǎn)向 GAA 設(shè)計(jì)的增強(qiáng)靜電。當(dāng)時(shí)我們?cè)儐?wèn)了英特爾批量實(shí)施 GAA 的時(shí)間表,并被告知預(yù)計(jì)“在 5 年內(nèi)”。目前,英特爾的 RibbonFET 將采用 20A 工藝,根據(jù)上述路線圖,很可能在 2024 年底實(shí)現(xiàn)產(chǎn)品化。

在此次活動(dòng)的英特爾 RibbonFET 圖表中,它們同時(shí)顯示了 PMOS 和 NMOS 器件,以及明顯看起來(lái)像 4 堆棧設(shè)計(jì)的結(jié)構(gòu)。鑒于我在行業(yè)會(huì)議上看到英特爾的演示文稿涉及從 2 堆棧到 5 堆棧的任何內(nèi)容,我們確認(rèn)英特爾確實(shí)將使用 4 堆棧實(shí)現(xiàn)。添加的堆棧越多,制造所需的工藝節(jié)點(diǎn)步驟就越多,引用英特爾的 Kelleher 博士的話,“移除堆棧比添加堆棧更容易!”。對(duì)于任何給定的進(jìn)程或功能,究竟什么是正確的堆棧數(shù)量仍然是一個(gè)活躍的研究領(lǐng)域,但英特爾似乎熱衷于四個(gè)。

據(jù)英特爾制程技術(shù)相關(guān)負(fù)責(zé)人Sanjay Natarajan博士介紹,RibbonFET是一個(gè)Gate All Around晶體管。作為一項(xiàng)已經(jīng)在業(yè)界被研發(fā)多年的技術(shù),Gate All Around的名稱來(lái)自于晶體管的架構(gòu)。從設(shè)計(jì)上看,這個(gè)全新設(shè)計(jì)將柵極完全包裹在通道周圍,可實(shí)現(xiàn)更好的控制,并在所有電壓下都能獲得更高的驅(qū)動(dòng)電流。

新的晶體管架構(gòu)加快了晶體管開(kāi)關(guān)速度,最終可打造出更高性能的產(chǎn)品。通過(guò)堆疊多個(gè)通道,即納米帶,可以實(shí)現(xiàn)與多個(gè)鰭片相同的驅(qū)動(dòng)電流,但占用的空間更小。通過(guò)對(duì)納米帶的部署,英特爾可以使得帶的寬度可以被調(diào)整,以適應(yīng)多種應(yīng)用。

縱觀其他競(jìng)爭(zhēng)對(duì)手,臺(tái)積電有望在其 2nm 工藝上過(guò)渡到 GAAFET 設(shè)計(jì)。在 2020 年 8 月的年度技術(shù)研討會(huì)上,臺(tái)積電確認(rèn)將一直采用 FinFET 技術(shù)直至其 3nm(或 N3)工藝節(jié)點(diǎn),因?yàn)樗呀?jīng)能夠找到該技術(shù)的重大更新,以實(shí)現(xiàn)超越最初預(yù)期的性能和泄漏擴(kuò)展——與臺(tái)積電 N5 相比,N3具有高達(dá) 50% 的性能提升、30% 的功耗降低或 1.7 倍的密度提升。臺(tái)積電表示,繼續(xù)使用 FinFET 為其客戶提供了舒適感。需要強(qiáng)調(diào)的是,臺(tái)積電 N2 的細(xì)節(jié)尚未披露。

相比之下,三星表示將在其 3nm 工藝節(jié)點(diǎn)中引入其 GAA 技術(shù)。早在 2019 年第二季度,三星代工廠就宣布向主要客戶提供其使用 GAAFET 的新 3GAE 工藝節(jié)點(diǎn)的第一個(gè) v0.1 開(kāi)發(fā)套件。當(dāng)時(shí)三星預(yù)測(cè)到 2021 年底量產(chǎn),而最新公告表明,雖然 3GAE 將在 2022 年內(nèi)部部署,但主要客戶可能要等到 2023 年才能獲得更先進(jìn)的 3GAP 工藝。

按照這個(gè)指標(biāo),三星可能是第一個(gè)邁入GAA大門的,盡管有內(nèi)部節(jié)點(diǎn),而臺(tái)積電將首先從 N5、N4 和 N3 節(jié)點(diǎn)中獲得很多收益。大約來(lái)到2023 年底,一切會(huì)變得有趣,因?yàn)榕_(tái)積電可能會(huì)考慮其 N2 設(shè)計(jì),而英特爾則致力于 2024 年的時(shí)間框架。官方幻燈片顯示 2024 年上半年,盡管作為技術(shù)公告與產(chǎn)品公告,兩者之間通常存在一些滯后。

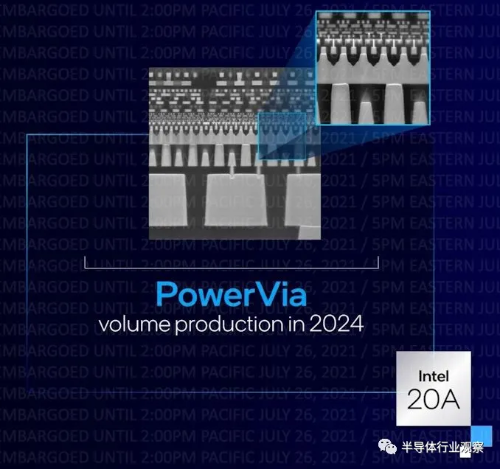

PowerVia則是英特爾全新的背面電能傳輸網(wǎng)絡(luò)。這是由英特爾工程師開(kāi)發(fā)的一項(xiàng)獨(dú)特技術(shù),也將在Intel 20A中首次采用。

我們知道,現(xiàn)代電路的制造過(guò)程從晶體管層 M0 作為最小層開(kāi)始。在此之上,以越來(lái)越大的尺寸添加額外的金屬層,以解決晶體管與處理器不同部分(緩存、緩沖器、加速器)之間所需的所有布線。現(xiàn)代高性能處理器的設(shè)計(jì)中通常有 10 到 20 個(gè)金屬層,頂層放置外部連接。然后將芯片翻轉(zhuǎn)(稱為倒裝芯片),以便芯片可以通過(guò)底部的連接和頂部的晶體管與外部世界進(jìn)行通信。

但正如Sanjay Natarajan博士所說(shuō),這種傳統(tǒng)的互連技術(shù)是在晶體管層的頂部進(jìn)行互聯(lián),由此產(chǎn)生的電源線和信號(hào)線的互混,導(dǎo)致了布線效率低下的問(wèn)題,會(huì)影響性能和功耗。為此業(yè)界轉(zhuǎn)向了“背面供電的技術(shù)”,也就是英特爾所說(shuō)的PowerVias。

在新的工藝中,英特爾把電源線置于晶體管層的下面,換言之是在晶圓的背面。通過(guò)消除晶圓正面的電源布線需求,可騰出更多的資源用于優(yōu)化信號(hào)布線并減少時(shí)延。通過(guò)減少下垂和降低干擾,也有助于實(shí)現(xiàn)更好的電能傳輸。這使我們能夠根據(jù)產(chǎn)品需求,對(duì)性能、功耗或面積進(jìn)行優(yōu)化。

換另一種說(shuō)法,在全新的設(shè)計(jì)中,我們現(xiàn)在將晶體管置于設(shè)計(jì)的中間。在晶體管的一側(cè),我們放置了通信線,允許芯片的各個(gè)部分相互通信。另一方面是所有與電源相關(guān)的連接(以及電源門控)。從本質(zhì)上講,我們轉(zhuǎn)向了三明治,其中晶體管是填充物。

“PowerVia將是業(yè)界首個(gè)部署的背面電能傳輸網(wǎng)絡(luò)。當(dāng)我們將這一創(chuàng)新做到產(chǎn)品中時(shí),其缺陷密度、性能和可靠性讓我們相信,它將蓄勢(shì)待發(fā)。”Sanjay Natarajan博士強(qiáng)調(diào)。

從整體來(lái)看,我們可以確定這種設(shè)計(jì)的好處始于簡(jiǎn)化電源線和連接線。通常,這些必須被設(shè)計(jì)為確保沒(méi)有信號(hào)干擾,并且主要的干擾源之一是大功率傳輸線,因此通過(guò)將它們放在芯片的另一側(cè),可以將它們排除在外。它也以另一種方式起作用——互連數(shù)據(jù)線的干擾會(huì)增加功率傳輸電阻,從而導(dǎo)致能量和熱量損失。通過(guò)這種方式,PowerVias 可以在驅(qū)動(dòng)電流增加時(shí)幫助新一代晶體管,因?yàn)樗梢灾苯釉谀抢锕╇姡皇菄@連接進(jìn)行布線。

但正如anandtech所說(shuō),這里有幾個(gè)障礙需要注意。

通常我們首先開(kāi)始制造晶體管,因?yàn)樗鼈兪亲罾щy且最有可能出現(xiàn)缺陷的——如果在計(jì)量早期發(fā)現(xiàn)缺陷(制造中的缺陷檢測(cè)),那么可以在周期中盡早報(bào)告。通過(guò)在中間放置晶體管,英特爾現(xiàn)在可以先制造幾層電源,然后再進(jìn)入艱難的階段。現(xiàn)在從技術(shù)上講,與晶體管相比,這些電源層將非常容易,并且不會(huì)出錯(cuò),但這是需要考慮的。

要考慮的第二個(gè)障礙是電源管理和導(dǎo)熱性。現(xiàn)代芯片首先將晶體管構(gòu)建成十幾個(gè)層,以電源和連接結(jié)束,然后芯片被翻轉(zhuǎn),因此耗電的晶體管現(xiàn)在位于芯片的頂部,并且可以管理熱量。在三明治設(shè)計(jì)中,熱能將通過(guò)芯片頂部的任何東西,這很可能是內(nèi)部通信線路。假設(shè)這些電線的熱量增加不會(huì)在生產(chǎn)或常規(guī)使用中引起任何問(wèn)題,那么這可能不是什么大問(wèn)題,但是當(dāng)熱量必須從晶體管傳導(dǎo)出去時(shí)需要考慮。

值得注意的是,這種“背面供電”技術(shù)已經(jīng)開(kāi)發(fā)了很多年。在 2021 年的 VLSI 研討會(huì)上發(fā)表的五篇研究論文中,imec 發(fā)表了多篇關(guān)于該技術(shù)的論文,展示了使用 FinFET 時(shí)的最新進(jìn)展,并且在 2019 年,Arm 和 imec宣布了在 imec 研究中基于等效 3nm 工藝構(gòu)建的 Arm Cortex-A53 上的類似技術(shù)設(shè)施。

總體而言,該技術(shù)降低了設(shè)計(jì)上的 IR 壓降,這在更先進(jìn)的工藝節(jié)點(diǎn)技術(shù)上越來(lái)越難以實(shí)現(xiàn)以提高性能。當(dāng)該技術(shù)在高性能處理器上大量使用時(shí),將會(huì)很有趣。

下一代封裝:EMIB 和 Foveros

除了工藝節(jié)點(diǎn)的進(jìn)步,英特爾還必須推進(jìn)下一代封裝技術(shù)。因?yàn)槭袌?chǎng)對(duì)高性能芯片的需求加上日益困難的工藝節(jié)點(diǎn)開(kāi)發(fā),就創(chuàng)造了這樣的一種環(huán)境,在這種環(huán)境中,處理器不再是一個(gè)單一的硅片,而是依賴于以有利于性能的方式封裝在一起的多個(gè)較小(并且可能優(yōu)化)的小芯片或塊、電源和最終產(chǎn)品。

換而言之,單個(gè)大型芯片不再是明智的商業(yè)決策——因?yàn)樗鼈冏罱K可能很難做到?jīng)]有缺陷,或者制造它們的技術(shù)沒(méi)有針對(duì)芯片上的任何特定功能進(jìn)行優(yōu)化。然而,將處理器分成單獨(dú)的硅片會(huì)為在這些片之間移動(dòng)數(shù)據(jù)造成額外的障礙——如果數(shù)據(jù)必須從硅片過(guò)渡到其他東西(例如封裝或中介層),那么就有了力量要考慮的成本和延遲成本。

權(quán)衡是針對(duì)特定目的構(gòu)建的優(yōu)化硅,例如在邏輯工藝上制造的邏輯芯片,在存儲(chǔ)器工藝上制造的存儲(chǔ)器芯片,并且較小的芯片在合并時(shí)通常比較大的芯片具有更好的電壓/頻率特性。但支撐這一切的是芯片是如何組合在一起的,

英特爾的兩種主要專業(yè)封裝技術(shù)是 EMIB 和 Foveros。英特爾解釋了兩者與未來(lái)節(jié)點(diǎn)開(kāi)發(fā)相關(guān)的未來(lái)。

一、EMIB:嵌入式多芯片互連橋接器

英特爾的 EMIB 技術(shù)專為布局在 2D 平面上的芯片到芯片連接而設(shè)計(jì)。

同一基板上的兩個(gè)芯片相互通信的最簡(jiǎn)單方法是采用穿過(guò)基板的數(shù)據(jù)通路。基板是由絕緣材料層組成的印刷電路板,其中散布著蝕刻成軌道和跡線( tracks and traces)的金屬層。根據(jù)基板的質(zhì)量、物理協(xié)議和所使用的標(biāo)準(zhǔn),通過(guò)基板傳輸數(shù)據(jù)會(huì)消耗大量電力,并且?guī)挄?huì)降低。但是,這是最便宜的選擇。

基板的替代方案是將兩個(gè)芯片都放在中介層(interposer)上。中介層是一大塊硅片,大到足以讓兩個(gè)芯片完全貼合,并且芯片直接與中介層結(jié)合。類似地,中介層也有數(shù)據(jù)路徑,但由于數(shù)據(jù)是從硅片移動(dòng)到硅片的,因此功率損失不如基板多,帶寬可以更高。這樣做的缺點(diǎn)是中介層也必須制造(通常在 65nm 上),所涉及的芯片必須足夠小以適應(yīng),而且可能相當(dāng)昂貴。為此,interposer和active interposers是一個(gè)很好的解決方案。

英特爾的 EMIB 解決方案是中介層和基板的結(jié)合。英特爾沒(méi)有采用大型中介層,而是使用小型硅片并將其直接嵌入基板中,英特爾將其稱為橋接器。橋?qū)嶋H上是兩半,每邊有數(shù)百或數(shù)千個(gè)連接,并且芯片被構(gòu)建為連接到橋的一半。現(xiàn)在,兩個(gè)芯片都連接到該橋接器,具有通過(guò)硅傳輸數(shù)據(jù)的好處,而不受大型中介層可能帶來(lái)的限制。如果需要更多帶寬,英特爾可以在兩個(gè)芯片之間嵌入多個(gè)橋接器,或者為使用兩個(gè)以上芯片的設(shè)計(jì)嵌入多個(gè)橋接器。此外,該橋的成本遠(yuǎn)低于大型中介層。

有了這些解釋,聽(tīng)起來(lái)英特爾的 EMIB 是雙贏的。然而該技術(shù)存在一些限制——實(shí)際上將橋嵌入基板有點(diǎn)困難。英特爾已花費(fèi)數(shù)年時(shí)間和大量資金試圖完善該技術(shù)以實(shí)現(xiàn)低功耗運(yùn)行。最重要的是,每當(dāng)您將多個(gè)元素添加在一起時(shí),該過(guò)程都會(huì)產(chǎn)生相關(guān)的良率問(wèn)題——即使將芯片連接到橋的良率是 99%,但在單個(gè)設(shè)計(jì)中使用十幾個(gè)芯片會(huì)降低整體良率下降到 87%,即使從已知的好芯片(有自己的收益)開(kāi)始也是如此。當(dāng)您聽(tīng)說(shuō)英特爾一直致力于將這項(xiàng)技術(shù)推向市場(chǎng)時(shí),他們正在努力改進(jìn)這些數(shù)字。

英特爾目前在市場(chǎng)上的幾種產(chǎn)品上都有 EMIB,最引人注目的是其 Stratix FPGA 和 Agilex FPGA 系列,但它也是 Kaby G 移動(dòng)處理器系列的一部分,將 Radeon GPU 連接到高帶寬內(nèi)存。英特爾已經(jīng)表示將基于其推出多款未來(lái)產(chǎn)品,包括 Ponte Vecchio(超級(jí)計(jì)算機(jī)級(jí)圖形)、Sapphire Rapids(下一代至強(qiáng)企業(yè)處理器)、Meteor Lake(2023 消費(fèi)級(jí)處理器)以及其他與圖形相關(guān)的產(chǎn)品。

在 EMIB 的路線圖方面,英特爾將在未來(lái)幾年減少凸點(diǎn)間距。當(dāng)芯片連接到嵌入在基板中的橋時(shí),它們通過(guò)凸塊連接,凸塊之間的距離稱為間距——凸塊間距越小,在同一區(qū)域內(nèi)可以建立的連接越多。這允許芯片增加帶寬或減小橋接尺寸。

2017 年的第一代 EMIB 技術(shù)使用 55 微米凸點(diǎn)間距,而且即將推出的 Sapphire Rapids 似乎仍然如此,但是英特爾正在將自己與超越 Sapphire Rapids 的 45 微米 EMIB,導(dǎo)致第三代 36 微米 EMIB. 這些的時(shí)間表沒(méi)有透露,但是在 Sapphire Rapids 之后將是 Granite Rapids,因此到這時(shí),可能會(huì)推出 45 微米的設(shè)計(jì)。

二、Foveros:Die to Die 的堆棧

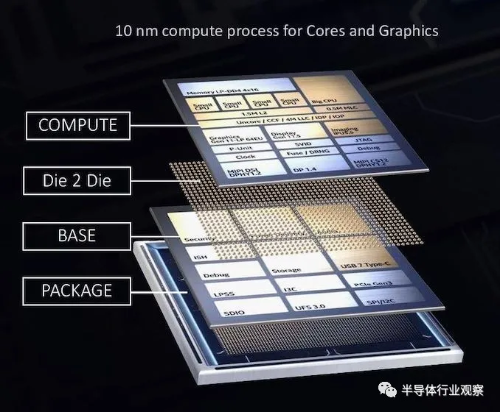

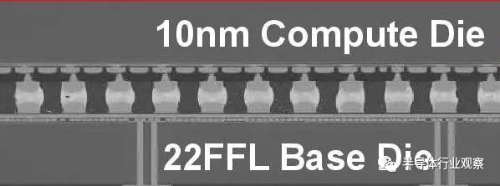

英特爾于 2019 年通過(guò)Lakefield推出了其芯片到芯片堆疊技術(shù),Lakefield 是一款專為低空閑功耗設(shè)計(jì)而設(shè)計(jì)的移動(dòng)處理器。雖然該處理器此后走向了生命盡頭,但該想法仍然是英特爾未來(lái)產(chǎn)品組合和代工產(chǎn)品的未來(lái)不可或缺的一部分。

Intel 的 die-to-die 堆疊在很大程度上與 EMIB 部分中提到的中介層技術(shù)非常相似。

我們將一塊(或更多)硅片放在另一塊硅片上。然而,在這種情況下,interposer或基片具有與頂部硅片中的主計(jì)算處理器的完整運(yùn)行相關(guān)的有源電路。雖然內(nèi)核和圖形在 Lakefield 的頂級(jí)芯片上,建立在英特爾的 10 納米工藝節(jié)點(diǎn)上,但基礎(chǔ)芯片擁有所有 PCIe 通道、USB 端口、安全性以及與 IO 相關(guān)的所有低功耗,并建立在 22FFL 低功耗上進(jìn)程節(jié)點(diǎn)。

因此,雖然 EMIB 技術(shù)將硅片彼此分開(kāi)工作被稱為 2D 縮放,但通過(guò)將硅片放在彼此的頂部,我們已經(jīng)進(jìn)入了完整的 3D 堆疊方式。這帶來(lái)了一些好處,尤其是在規(guī)模上,可以獲得數(shù)據(jù)路徑更短的優(yōu)勢(shì),由于更短的電線而導(dǎo)致更少的功率損耗,但也有更好的延遲。芯片到芯片的連接仍然是鍵合連接,第一代的間距為 50 微米。

但這里有兩個(gè)關(guān)鍵限制:熱量和功耗。為避免散熱問(wèn)題,英特爾使基本芯片幾乎沒(méi)有邏輯并使用低功耗工藝。在電源方面,問(wèn)題在于讓頂部計(jì)算芯片為其邏輯供電——這涉及從封裝向上通過(guò)基礎(chǔ)芯片到頂部芯片的大功率硅通孔 (TSV),而那些承載功率的 TSV 成為由于高電流引起的干擾而導(dǎo)致的局部數(shù)據(jù)信令問(wèn)題。還希望在未來(lái)的工藝中縮小到更小的凸點(diǎn)間距,從而實(shí)現(xiàn)更高的帶寬連接,需要更多地關(guān)注功率傳輸。

今天與 Foveros 相關(guān)的第一個(gè)公告是關(guān)于第二代產(chǎn)品。英特爾的 2023 年消費(fèi)級(jí)處理器 Meteor Lake 已在上文中描述為使用英特爾 4nm 計(jì)算塊。英特爾今天還表示,它將在該平臺(tái)上使用其第二代 Foveros 技術(shù),實(shí)現(xiàn) 36 微米的凸點(diǎn)間距,與第一代相比,連接密度有效地增加了一倍。Meteor Lake 中的另一個(gè) tile 尚未公開(kāi)(它有什么或它在哪個(gè)節(jié)點(diǎn)上),但英特爾也表示 Meteor Lake 將從 5 W 擴(kuò)展到 125 W。

三、Foveros Omni:第三代 Foveros

對(duì)于那些一直密切關(guān)注英特爾封裝技術(shù)的人來(lái)說(shuō),“ODI”這個(gè)名字可能很熟悉。它代表 Omni-Directional Interconnect,它是英特爾之前封裝技術(shù)路線圖中的名稱。現(xiàn)在將作為 Foveros Omni 銷售。

這意味著第一代 Foveros 需要top tie小于 base die的限制現(xiàn)在被取消。top tie可以比base die大,或者如果每個(gè)層上有多個(gè)裸片,它們可以連接到任意數(shù)量的其他硅片。Foveros Omni 的目標(biāo)是真正解決 Foveros 初始部分中討論的功率問(wèn)題——因?yàn)槌休d TSV 的功率會(huì)在信號(hào)中造成大量局部干擾,因此放置它們的理想位置是在base die的外部。Foveros Omni 是一種技術(shù),允許頂部裸片從基礎(chǔ)裸片懸垂,銅柱從基板一直延伸到頂部裸片以提供電源。

使用這種技術(shù),如果可以從top die的邊緣引入電源,則可以使用這種方法。然而,我確實(shí)想知道,如果使用大硅片,電源是否會(huì)更好地從中間饋電——英特爾曾表示 Foveros Omni 與分離式 base dies一起工作,這樣,如果base die設(shè)計(jì)用于可在該較低層上使用的基板。

通過(guò)將功率 TSV 移到base die之外,這還可以改善裸片到裸片的凸點(diǎn)間距。英特爾稱 Omni 為 25 微米,與第二代 Foveros 相比,凸點(diǎn)密度又增加了 50%。英特爾預(yù)計(jì) Foveros Omni 將在 2023 年為批量生產(chǎn)做好準(zhǔn)備。

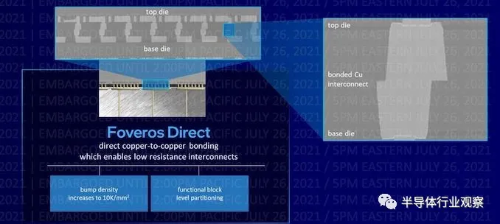

四、Foveros Direct:第四代 Foveros

任何芯片到芯片連接的問(wèn)題之一是連接本身。在迄今為止提到的所有這些技術(shù)中,我們都在處理微凸點(diǎn)粘合連接——帶有錫焊帽的小銅柱,它們被放在一起并“粘合”以創(chuàng)建連接。由于這些技術(shù)正在增加銅和沉積錫焊料,因此很難將它們按比例縮小,而且電子設(shè)備的功率損耗也會(huì)轉(zhuǎn)移到不同的金屬中。

Foveros Direct 通過(guò)直接進(jìn)行銅對(duì)銅鍵合來(lái)解決這個(gè)問(wèn)題。

多年來(lái),人們一直在研究硅與硅之間直接連接的概念,而不是依靠柱子和凸塊的結(jié)合。如果一塊硅直接與另一塊對(duì)齊,那么幾乎不需要額外的步驟來(lái)生長(zhǎng)銅柱等。問(wèn)題在于確保所有連接都已完成,確保top die和base die都非常平坦,沒(méi)有任何障礙。此外,兩片硅必須合二為一,并且永久粘合在一起而不會(huì)分開(kāi)。

Foveros Direct 是一項(xiàng)技術(shù),可幫助英特爾將其芯片到芯片連接的凸點(diǎn)間距降低到 10 微米,密度是 Foveros Omni 的 6 倍。通過(guò)實(shí)現(xiàn)扁平銅對(duì)銅連接,凸點(diǎn)密度增加,全銅連接的使用意味著低電阻連接和功耗降低。英特爾建議使用 Direct,功能芯片分區(qū)也變得更容易,并且可以根據(jù)需要將功能塊拆分到多個(gè)級(jí)別。

從技術(shù)上講,F(xiàn)overos Direct 作為芯片到芯片的鍵合可以被認(rèn)為是對(duì) Foveros Omni 的補(bǔ)充,它具有base die外部的電源連接——兩者都可以相互獨(dú)立使用。直接綁定會(huì)使內(nèi)部電源連接更容易,但可能仍然存在干擾問(wèn)題,Omni 會(huì)處理這些問(wèn)題。

應(yīng)該指出的是,臺(tái)積電擁有類似的技術(shù),稱Chip-on-Wafer (或Wafer-on-Wafer),其客戶產(chǎn)品將在未來(lái)幾個(gè)月內(nèi)使用 2 層堆棧推向市場(chǎng)。臺(tái)積電在 2020 年年中展示了 12 層堆棧,但這是用于信號(hào)的測(cè)試工具,而不是產(chǎn)品。堆棧中的問(wèn)題仍然是熱量,以及進(jìn)入每一層的內(nèi)容。

英特爾預(yù)測(cè),F(xiàn)overos Direct 與 Omni 一樣,將在 2023 年準(zhǔn)備好量產(chǎn)。

“隨著我們繼續(xù)推動(dòng)先進(jìn)封裝的發(fā)展,我們將在未來(lái)幾代技術(shù)中從電子封裝過(guò)渡到集成硅光子學(xué)的光學(xué)封裝。當(dāng)然,我們將繼續(xù)與包括Leti、IMEC和IBM在內(nèi)的產(chǎn)業(yè)伙伴密切合作,在以上和其他諸多創(chuàng)新領(lǐng)域進(jìn)一步發(fā)展制程和封裝技術(shù)。”英特爾方面強(qiáng)調(diào)。

EUV光刻機(jī)和晶圓代工客戶

在英特爾今天的演講中,他們強(qiáng)調(diào),公司將成為 ASML 下一代 EUV 技術(shù)(即 High-NA EUV)的主要客戶。其中NA 與 EUV 機(jī)器的“數(shù)值孔徑”有關(guān),或者簡(jiǎn)單地說(shuō),在 EUV 光束擊中晶圓之前,您可以在機(jī)器內(nèi)部使該光束有多寬。在您擊中晶片之前光束越寬,它擊中晶片時(shí)的強(qiáng)度就越大,從而提高打印線條的準(zhǔn)確度。

通常,在光刻中為了獲得更好的印刷線,我們從單一圖案化轉(zhuǎn)向雙圖案化(或四方圖案化)以獲得這種效果,這會(huì)降低產(chǎn)量。轉(zhuǎn)向High NA 意味著生態(tài)系統(tǒng)可以更長(zhǎng)時(shí)間地保持單一模式,一些人認(rèn)為這可以讓行業(yè)“更長(zhǎng)時(shí)間地與摩爾定律保持一致”。

首先,英特爾方面表示,將EUV投入量產(chǎn),需要構(gòu)建一個(gè)以該設(shè)備為中心的完整供應(yīng)鏈生態(tài)——光刻膠、掩模生成、蒙版加附、計(jì)量檢測(cè)。而英特爾為構(gòu)建這個(gè)生態(tài)系統(tǒng)付出了很大努力。

據(jù)了解,英特爾子公司IMS是EUV多波束掩模刻寫儀的全球主要供應(yīng)商。這是制作高分辨率掩模的必備工具,而掩模則是實(shí)現(xiàn)EUV光刻技術(shù)的關(guān)鍵部分。采用掩模刻寫技術(shù)對(duì)英特爾來(lái)說(shuō)極具競(jìng)爭(zhēng)優(yōu)勢(shì),也是同業(yè)的關(guān)鍵推動(dòng)力。

與此同時(shí),英特爾還在攜手ASML定義、構(gòu)建和部署下一代EUV工具,被稱為高數(shù)值孔徑EUV(High-NA EUV)。High-NA將集成更高精度的透鏡和反射鏡,以提高分辨率,從而在硅片上刻印出更微小的圖樣。英特爾有望率先獲得業(yè)界第一臺(tái)High-NA EUV光刻機(jī),并計(jì)劃在2025年成為首家在生產(chǎn)中實(shí)際采用High-NA EUV的芯片制造商。

英特爾強(qiáng)調(diào),這些進(jìn)展也取決于我們和業(yè)界其他關(guān)鍵參與者的密切合作。與包括應(yīng)用材料(Applied Materials)、泛林集團(tuán)(LAM Research)和東電電子(TEL)在內(nèi)的設(shè)備供應(yīng)商的合作,是我們實(shí)現(xiàn)領(lǐng)先技術(shù)路線圖的關(guān)鍵。

從目前看來(lái),當(dāng)前的 EUV 系統(tǒng)的NA為 0.33,而新系統(tǒng)的NA為 0.55。ASML 的最新更新表明,它預(yù)計(jì)客戶將在 2025/2026 年可以使用 High-NA 設(shè)備進(jìn)行生產(chǎn),這意味著英特爾可能會(huì)在 2024 年中期獲得第一臺(tái)機(jī)器(我們認(rèn)為是 ASML NXE:5000)。確切地說(shuō),ASML 打算在那個(gè)時(shí)間段內(nèi)生產(chǎn)多少臺(tái)High NA 機(jī)器是未知的,那就意味著擁有第一臺(tái)機(jī)器不會(huì)是一個(gè)大勝利。但是,如果 High-NA 上升緩慢,則由英特爾來(lái)利用其優(yōu)勢(shì)。

最后,英特爾還披露了他們?cè)诰A代工方面的進(jìn)展。

Pat Gelsinger表示,英特爾代工服務(wù)(IFS)的優(yōu)勢(shì)之一,是公司既能提供領(lǐng)先的制程和封裝技術(shù)創(chuàng)新,又能將我們的既有成熟技術(shù)以全新的方式服務(wù)于我們的客戶。客戶對(duì)英特爾代工服務(wù)(IFS)一直懷有強(qiáng)烈的興趣,其中受到重點(diǎn)關(guān)注的是我們成熟的先進(jìn)封裝技術(shù)。

基于此,英特爾宣布,公司已經(jīng)與AWS簽約,它們將成為我們的第一個(gè)使用英特爾代工服務(wù)(IFS)封裝解決方案的客戶。此外,英特爾也與高通合作,他們將采用Intel 20A制程工藝技術(shù)。

兩家公司都堅(jiān)信,移動(dòng)計(jì)算平臺(tái)的領(lǐng)先發(fā)展將開(kāi)啟半導(dǎo)體的新時(shí)代。可以明確的是,英特爾代工服務(wù)已揚(yáng)帆起航!