12月14日上午,,中國工程院,、科睿唯安公司與高等教育出版社聯(lián)合在京發(fā)布《全球工程前沿2021》報(bào)告,。工程科技創(chuàng)新是推動經(jīng)濟(jì)社會進(jìn)步的重要力量,,是實(shí)現(xiàn)人類可持續(xù)發(fā)展的重要保障,?!度蚬こ糖把?021》報(bào)告圍繞機(jī)械與運(yùn)載工程,、信息與電子工程,、化工冶金與材料工程、能源與礦業(yè)工程,、土木水利與建筑工程,、環(huán)境與輕紡工程、農(nóng)業(yè),、醫(yī)藥衛(wèi)生,、工程管理9個(gè)領(lǐng)域,遴選出年度工程研究前沿93項(xiàng)和工程開發(fā)前沿93項(xiàng),,并對其中關(guān)鍵的28項(xiàng)工程研究前沿和28項(xiàng)工程開發(fā)前沿從國家布局,、合作態(tài)勢以及發(fā)展趨勢等角度進(jìn)行詳細(xì)剖析。信息與電子工程領(lǐng)域工程開發(fā)前沿的第一位,,就是目前被廣泛關(guān)注的芯粒設(shè)計(jì)與芯片三維堆疊系統(tǒng)集成技術(shù),,也就是所謂的Chiplet技術(shù)。這說明我們國家最高水平的工程技術(shù)領(lǐng)域的專家已經(jīng)注意到了這一技術(shù)的重要價(jià)值并予以了高度關(guān)注,。但是在目前的國際形勢下,,我國如何基于自身的現(xiàn)實(shí)條件,尋找到一條適合我國現(xiàn)實(shí)情況的Chiplet發(fā)展之路,。進(jìn)而在一定程度上彌補(bǔ)我國集成電路產(chǎn)業(yè)的短板,,以另辟蹊徑的方式增強(qiáng)我國集成電路產(chǎn)業(yè)抗風(fēng)險(xiǎn)能力。本文作者將根據(jù)自身的理解和研究經(jīng)歷,,提出一些看法,,歡迎各界朋友批評指正。

Chiplet——“延續(xù)”摩爾定律的重要技術(shù)途徑

Chiplet又被翻譯為芯?;蛐⌒酒?,為了不引起歧義本文直接使用Chiplet英文原文。到目前為止AMD、Intel,、Nvidia等多家國際頭部IC設(shè)計(jì)企業(yè)都推出過基于Chiplet的產(chǎn)品,,而目前又傳出蘋果準(zhǔn)備在下一代高端處理器中采用Chiplet技術(shù)。一時(shí)間Chiplet技術(shù)仿佛成為了流量明星,,成為最近幾年來集成電路行業(yè)最熱的技術(shù)之一,。而在國內(nèi),Chiplet技術(shù)也是受到了各方關(guān)注,。但遺憾的是,,除了海思以外還缺乏有公司或者機(jī)構(gòu)真正采用Chiplet技術(shù)去做出商業(yè)級別的芯片。

那么各個(gè)頭部公司青睞Chiplet的原因是什么呢,?這實(shí)際是“摩爾定律”發(fā)展趨緩,,依靠傳統(tǒng)方法算力提升難度增加而探索出了一條技術(shù)途徑。

“摩爾定律”到底死沒死,,是近10年來不斷被提起的一個(gè)話題,。不斷有消息宣稱“摩爾定律”已死,但又不斷有專家出來辟謠說“摩爾定律”還活著,,還在不斷的延續(xù),。一時(shí)間仿佛“摩爾定律”化身為薛定諤的貓,處于“又生又死”的狀態(tài),。但其實(shí)我們仔細(xì)分析一下“活”,,就可以發(fā)現(xiàn)“摩爾定律”確實(shí)還活著,只不過越來越不能“健康”的活著,。如果拿人來做比喻的話,,那么在45nm工藝制程之前的摩爾定律可以說正值盛年,要想活下去注意身體,、日常鍛煉就好,。而到了45nm節(jié)點(diǎn)時(shí),過大的泄漏電流已經(jīng)讓微縮難以為繼,,不得已英特爾將采用被稱為high-k的嶄新材料來制造晶體管閘極電介質(zhì),,而而晶體管閘極的電極也新的金屬材料組合。這就好像40多,、50歲的人經(jīng)歷了針對某個(gè)器官的重大手術(shù)一樣,,活是繼續(xù)能活下去,但這活的質(zhì)量已經(jīng)大不如前,。

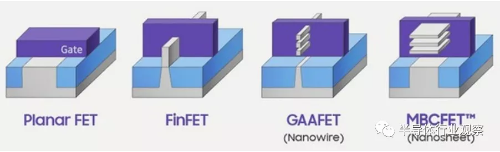

而在工藝制程演進(jìn)到28nm以下時(shí),,傳統(tǒng)的平面晶體管結(jié)構(gòu)完全不能支撐進(jìn)一步微縮,2011年以后以FinFET為代表的新型器件結(jié)構(gòu)全面崛起,。至此以后工藝制程的微縮進(jìn)入了“舉步維艱”的時(shí)代,,Intel公司由于其制程長期被卡在14nm附近導(dǎo)致處理器性能提升緩慢(當(dāng)然,,也不止這個(gè)原因)而被廣大網(wǎng)友戲稱為“牙膏廠”。即便是采用了FinFET技術(shù)也并沒有能夠?yàn)槟柖裳訅鄱嗑?,隨著工藝制程進(jìn)入了10nm以下,,一些如GAAFET這樣的新的器件結(jié)構(gòu)又將被應(yīng)用到產(chǎn)業(yè)中。

圖1.近10年新型器件結(jié)構(gòu)的演變

這些新型器件的結(jié)構(gòu)導(dǎo)致工藝復(fù)雜,,各家實(shí)現(xiàn)的技術(shù)路線也各不相同。同樣是7nm制程的,,臺積電和三星的采取的技術(shù)路線區(qū)別很大,。其實(shí)發(fā)展到這一步,“摩爾定律”可以類比于一個(gè)已步入暮年的普通人,,靠“打針吃藥”勉力維持著,。雖然活著,但活得很艱難,?;畹暮堋百F”也活的很“脆弱”。

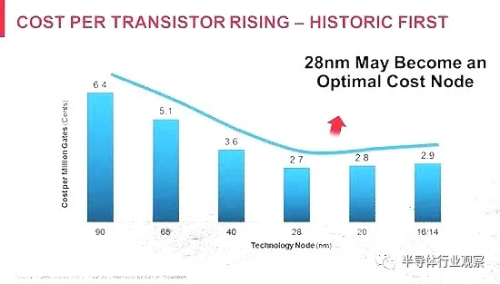

先來談貴的問題,。貴的原因是由于采用了大量新技術(shù)新工藝新結(jié)構(gòu),,這讓芯片制造的成本成倍增加。增加成本還不是最關(guān)鍵的,,關(guān)鍵這樣的成本增加似乎是無止盡的,。為維持晶體管的密度可以持續(xù)增加,現(xiàn)在每革新一代制程就需要大量的技術(shù)和工藝創(chuàng)新,。這就是使得經(jīng)濟(jì)成本完全沒有辦法攤薄,。

事實(shí)上從圖2就可以看出,在28nm以后,,平攤到單個(gè)晶體管上的價(jià)格其實(shí)就沒有下降,,反而在不斷的上升。這其實(shí)已經(jīng)在經(jīng)濟(jì)上宣告了摩爾定律的終結(jié)——我們確實(shí)還是可以買到包含了越來越多晶體管的芯片,,但是那種等2年左右時(shí)間就可以用同樣的價(jià)格買到比原來多一倍晶體管芯片的“理想年代”已經(jīng)一去不返了,。

圖2.不同制程下每百萬門的造價(jià)

接下來說“脆弱”的問題,也就是晶體管的缺陷不斷增加的問題,。這其實(shí)是晶體管微縮到一定程度以后,,必然出現(xiàn)的問題。現(xiàn)在的晶體管加工早已經(jīng)是讓光刻技術(shù)“不堪重負(fù)”,。無論是多重曝光還是浸潤式光刻,,都是用一種“明知不可為而為之”的方式在追求極致的微縮。而這就讓工藝的一致性和準(zhǔn)確性控制非常難做,,出現(xiàn)工藝誤差甚至加工缺陷的情況就越來越嚴(yán)重,。最終反應(yīng)到芯片上面就是成品率低或者說器件故障率高。故障率高的結(jié)果就是一次加工,拋開測試后無法工作的壞片,,剩下能工作的芯片就很少,。本來加工一次就貴,加工完了以后還要扔掉不少,,于是加工出來的合格產(chǎn)品的價(jià)格就會居高不下

傳統(tǒng)上解決的方法無非兩種:一是加大投資進(jìn)一步去改進(jìn)工藝加強(qiáng)品控,,但這不但投資巨大而去改進(jìn)總是有物理極限的;二是利用容錯(cuò)設(shè)計(jì)的方法讓芯片即使在有錯(cuò)的情況下也可以正常工作,,但這也需要付出額外硅片面積來實(shí)現(xiàn)容錯(cuò)電路的,,當(dāng)缺陷多到一定程度以后加過多的容錯(cuò)電路從經(jīng)濟(jì)上看又不劃算 。所以“脆弱”的問題最終還是反應(yīng)到了“貴”上面,,成為進(jìn)一步推高先進(jìn)制程芯片造價(jià)的推手,。

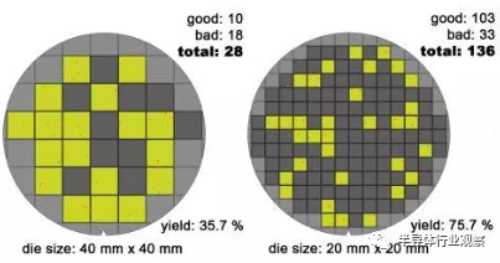

以上兩個(gè)問題應(yīng)該如何解決?確實(shí)都不太好解決,,但可以嘗試先來解決第二個(gè)問題,。解決第二個(gè)問題的方法就是“切”,把大芯片切成小芯片,。

圖3給了一個(gè)示意圖,,當(dāng)我們的裸芯(Die)的面積越小,那么在缺陷概率一定的情況下整體的良率越高,。如果裸芯的面積是40*40的良率才35.7%,。如果面積減少到20*20,良率就上升到了75%,。如果進(jìn)一步減小,,良率還會提升。這里面有一些統(tǒng)計(jì)學(xué)上的數(shù)學(xué)關(guān)系,。這里就不詳細(xì)解釋了,,大家從理性直覺簡單來分析一下就能明白:在缺陷“密度”確定的情況下,裸芯的面積越小,,“撞”上缺陷的概率就越大,。

圖3.裸芯面積越小整體良率越高

所以把大芯片切成小芯片(Chiplet)就變成了提升良率的一種必然選擇。而一旦切成Chiplet以后又有了一個(gè)新的好處:快速復(fù)用,。雖然以前SoC設(shè)計(jì)方法學(xué)中IP已經(jīng)被設(shè)計(jì)成可以復(fù)用的,,但形成SoC原型設(shè)計(jì)以后該走的軟硬件協(xié)同驗(yàn)證、后端與物理設(shè)計(jì),、流片制造,、封裝測試的流程一個(gè)也少不了??梢哉f是“復(fù)用了但又沒有完全復(fù)用”,。而如果是Chiplet的話,,就是一個(gè)已經(jīng)走完了完整設(shè)計(jì)、制造,、測試流程的成品小裸片,,只是需要直接做一次封裝加工就可以用起來。其復(fù)用的程度遠(yuǎn)超過現(xiàn)在的IP,。

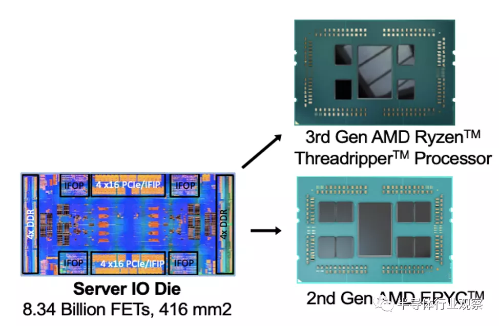

圖4就給出了AMD復(fù)用Chiplets的一個(gè)典型案例,。把多個(gè)Chiplet在封裝級重新拼裝成起來構(gòu)成完整的系統(tǒng)級芯片,可以在保證良率的前提下繼續(xù)讓單顆芯片內(nèi)部的晶體管數(shù)量增加,,又可以復(fù)用之前已經(jīng)成熟的Chiplet,。

圖4.AMD在第三代銳龍(Ryzen)處理器上復(fù)用了第二代宵龍(EPYC)處理器的IO Chiplet

在圖4中可以看出AMD在第三代銳龍(Ryzen)處理器上復(fù)用了第二代霄龍(EPYC)處理器的IO Chiplet,這種復(fù)用不但意味著可以將“老舊制程”生產(chǎn)的Chiplet繼續(xù)應(yīng)用到下一代產(chǎn)品中以節(jié)約成本,,更意味著可以極大的節(jié)約設(shè)計(jì),、驗(yàn)證和生產(chǎn)的周期并漸小失敗的風(fēng)險(xiǎn),。這一方面要節(jié)約大量的人力成本,,同時(shí)也可以加快上市時(shí)間。

如果只是看單位硅片面積上的晶體管數(shù)量,,Chiplet技術(shù)仿佛沒有什么幫助,,也談不上“延續(xù)”摩爾定律。但如果一顆完整的芯片看成是封裝后“成品”,,我們可以認(rèn)為摩爾定律還在繼續(xù)延續(xù),,因?yàn)榭偟木w管數(shù)量確實(shí)增加了。尤其是重要的是,,這是在不大量的增加成本的前提下完成的,,雖然這似乎是一條“退而求其次”的路線。

綜上所述:1,、摩爾定律如果繼續(xù)依靠傳統(tǒng)的“微縮”路線從經(jīng)濟(jì)上來說其實(shí)已經(jīng)難以為繼,,單個(gè)芯片上集成更多的晶體管雖然從技術(shù)上來說依然可行但成本已經(jīng)大到無法接受;2,、先進(jìn)制程的良率問題是讓流片成本居高不下的主要因素之一,,將大裸片“切”成Chiplet是有效提升單個(gè)晶圓良率的必由之路,也是讓摩爾定律可以持續(xù)的主要方法之一,。3,、Chiplet技術(shù)不但可以提升良率,還可以通過復(fù)用成熟的Chiplet進(jìn)一步降低設(shè)計(jì)成本和風(fēng)險(xiǎn),,讓單顆芯片內(nèi)部晶體管數(shù)量持續(xù)增加的同時(shí)成本依然可以接受,。

發(fā)展Chiplet技術(shù)面臨的問題

可以看到,Chiplet技術(shù)是制程演進(jìn)到了納米級別,,摩爾定律從經(jīng)濟(jì)上已難以為繼時(shí)所發(fā)展出來的一條技術(shù)路線,。也可以說是不得已而為之,,改變了傳統(tǒng)的技術(shù)演進(jìn)方式。在某種程度上說,,有一點(diǎn)“產(chǎn)業(yè)鏈局部重構(gòu)”的意味,。但這種改變必然也要面臨新的問題。

首要的問題就是多個(gè)Chiplet之間的通信問題,。這又分為了幾個(gè)層次,,包括了封裝技術(shù)、電路設(shè)計(jì),、協(xié)議標(biāo)準(zhǔn)等多個(gè)方面,。

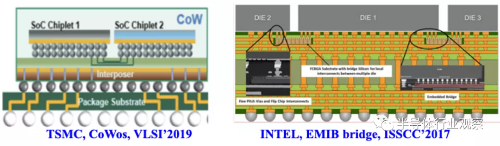

首先是封裝技術(shù),Chiplet技術(shù)要把原本單個(gè)大硅片“切”成多個(gè)再從封裝級組裝起來,。單個(gè)硅片上的布線密度和信號傳輸質(zhì)量是要遠(yuǎn)遠(yuǎn)高于Chiplet之間的,。這就要求必須要發(fā)展出高密度、大帶寬布線的“先進(jìn)封裝技術(shù)”,,盡可能的提升在多個(gè)Chiplet之間布線的數(shù)量并提升信號傳輸質(zhì)量,。好消息是經(jīng)過多年的發(fā)展,Intel和臺積電(TSMC)都已經(jīng)有了相關(guān)的技術(shù)儲備,,通過所謂的中介層(Interposer)將多個(gè)Chiplet互連起來,。TSMC公布的技術(shù)是CoW,而Intel公布的是EMIB,。今天這些技術(shù)仍然在不斷演進(jìn)中,,并有更新的技術(shù)不斷推出。

圖5.臺積電和Intel公開發(fā)表的先進(jìn)封裝技術(shù)

其次是用于Chiplet之間的高速通信接口電路設(shè)計(jì),,也就是Chiplet間通信的“物理層”設(shè)計(jì),。Chiplet之間的通信當(dāng)然可以依靠傳統(tǒng)的高速Serdes電路來解決,甚至可以完整的復(fù)用PCIe之類目前已經(jīng)成熟的協(xié)議,。但這些協(xié)議是用于解決芯片間甚至板卡間通信的,,在Chiplet之間通信用會造成面積和功耗的浪費(fèi)。目前專門研究Chiplet間高速通信接口的論文也不少,,也有很多類似的IP核被各大公司研制出來,。

通信協(xié)議是保證不同Chiplet之間能夠順利的完成數(shù)據(jù)交互的必要保證,也是決定Chiplet能否“復(fù)用”的前提條件,。目前Intel公司推出了AIB協(xié)議,、TSMC和Arm合作搞了LIPINCON協(xié)議,當(dāng)然還有不少別的協(xié)議,,在此不再贅述,。雖然各家都在嚷嚷協(xié)議的重要性,但在目前的環(huán)境下Chiplet首先是“頭部半導(dǎo)體”公司才會采用的技術(shù),,而這些公司“切”自己設(shè)計(jì)的大芯片然后再“封”起來自己說了算就行,,并沒有太多去和別的Chiplet互聯(lián)互通的緊迫性,。目前對于協(xié)議看得最重的應(yīng)該是DARPA,因?yàn)镈ARPA所關(guān)心的市場屬于量不大但特定需求多的市場,。如果各家都按一定的標(biāo)準(zhǔn)來把自己的Chiplet通信接口和協(xié)議標(biāo)準(zhǔn)化了,,那DARPA就可以“采眾家之長”,從產(chǎn)品定義到最終產(chǎn)品實(shí)現(xiàn)之間的環(huán)節(jié)會少很多,。這將大大提升美軍信息技術(shù)的迭代能力,,這也是DARPA推動電子復(fù)興計(jì)劃中“CHIPS”項(xiàng)目的初衷。其次跟著吆喝的是一些IP公司,,如果實(shí)現(xiàn)了通信協(xié)議的統(tǒng)一,,這些IP公司就有可能實(shí)現(xiàn)從“賣IP”到“賣Chiplet”的轉(zhuǎn)型,開發(fā)出新的商業(yè)模式,。

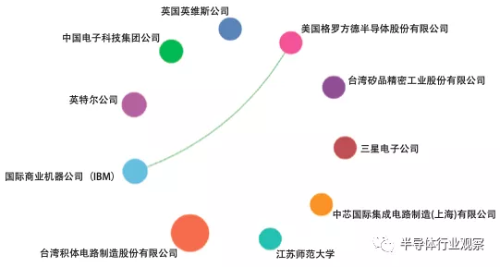

綜合看以上幾個(gè)方面,,先進(jìn)封裝技術(shù)是Chiplet實(shí)施的基礎(chǔ)和前提,事實(shí)上正是由于先進(jìn)封裝技術(shù)的突破才讓Chiplet技術(shù)從構(gòu)想走入現(xiàn)實(shí),。面向Chiplet的通信接口電路設(shè)計(jì)也很重要,,相信這些已經(jīng)實(shí)施了Chiplet的頭部公司一定也有自己的設(shè)計(jì)。但如果“實(shí)在沒有”,,用現(xiàn)有技術(shù)湊合的話其實(shí)能勉強(qiáng)一用,。至于通信協(xié)議,,目前應(yīng)該還屬于“誰都說服不了誰”的階段,。其實(shí)這個(gè)也很正常,通信協(xié)議真正能夠推開,,最后就是“產(chǎn)品為王”,。最后基于那個(gè)產(chǎn)品的協(xié)議占了主流,哪個(gè)協(xié)議也就成為了“事實(shí)標(biāo)準(zhǔn)”,。Wishbone,、CoreConnect、Avalone這些片上總線協(xié)議如今聽過的人不多了的原因,,無非是Arm作為最大的SoC方案供應(yīng)商占據(jù)了大部分市場以后自然把其支持的AMBA協(xié)議簇給帶火了?,F(xiàn)階段強(qiáng)行的去談什么統(tǒng)一標(biāo)準(zhǔn)既沒有意義也不現(xiàn)實(shí),最終必然是“剩者為王”,。更何況現(xiàn)階段Chiplet還是“自家切了自家用”的階段,,只要這些頭部公司內(nèi)部統(tǒng)一了就行。從《全球工程前沿2021》報(bào)告中公布的合作網(wǎng)絡(luò)也可以看出,,目前各個(gè)機(jī)構(gòu)之間的合作幾乎沒有,。

發(fā)展Chiplet要解決的第二大問題就是“設(shè)計(jì)方法學(xué)”的問題,說稍微直白一點(diǎn)就是:先進(jìn)封裝解決了如何“拼”的問題,,但更重要的是要解決如何“切”的問題,。半導(dǎo)體行業(yè)觀察公眾號前幾日發(fā)表的“英偉達(dá)新論文,,透露出GPU設(shè)計(jì)的無奈和未來”中詳細(xì)的闡述了英偉達(dá)公司在決策下一代GPU要采用Chiplet技術(shù)時(shí)應(yīng)該如何把一整個(gè)完整的大設(shè)計(jì)劃分成多個(gè)Chiplet的思考和驗(yàn)證過程,這其實(shí)就是“設(shè)計(jì)方法學(xué)”的初步體現(xiàn),。而要讓基于Chiplet的設(shè)計(jì)方法真正從“可用”變到“好用”,,需要定義完整的設(shè)計(jì)流程以及研制配套的設(shè)計(jì)輔助工具。這一塊展開說了又是一大段論述,,為了節(jié)約篇幅在此不做詳細(xì)闡述,。

國內(nèi)外發(fā)展Chiplet的“同”和“異”

Chiplet作為先進(jìn)的集成電路技術(shù),目前在國內(nèi)也是有大量的公司和研究機(jī)構(gòu)關(guān)注,。有關(guān)Chiplet什么聯(lián)盟,、論壇之類的也有不少。但基于目前的國際形勢和國內(nèi)產(chǎn)業(yè)的實(shí)際發(fā)展水平,,國內(nèi)要面臨的困難和國際頭部IC設(shè)計(jì)公司并不相同,。

以目前的國際形勢下,國內(nèi)集成電路產(chǎn)業(yè)最大的挑戰(zhàn)來自于“封鎖”,,而最大的機(jī)會來自于“自主”,。由于“封鎖”的問題,讓我們難以像以前那樣非常方便的獲取到先進(jìn)制程來代工,。這也很“巧合”的與Chiplet技術(shù)出現(xiàn)的原因類似:微縮的道路走不下去了,,在單位硅片面積上增加晶體管數(shù)量有困難,只有轉(zhuǎn)而追求在單個(gè)封裝內(nèi)部晶體管數(shù)還等持續(xù)提升,。這也是目前發(fā)展Chiplet技術(shù)對于國內(nèi)芯片產(chǎn)業(yè)最大的意義,,當(dāng)我們走傳統(tǒng)方式延續(xù)摩爾定律的路子被“卡”斷的時(shí)候,依然有一條“退而求其次”技術(shù)路線可以走,。

雖然目的類似,,但國內(nèi)發(fā)展Chiplet的其它條件卻和國際頭部IC設(shè)計(jì)公司發(fā)展Chiplet并不相同。

從上面的分析我們可以看出,,先進(jìn)制程下采用Chiplet是由于良率問題而導(dǎo)致單個(gè)裸芯面積不能太大,,而不得不去把大的設(shè)計(jì)“切”小。而我們要面臨的問題是由于制程不夠先進(jìn),,單位面積上容納的晶體管數(shù)量有限,,繼續(xù)去做大會面臨電源噪聲、功耗,、良率等一系列問題,。這兩者之間有一定的相似性,都是要限制單個(gè)裸片上的晶體管數(shù)量,,但背后的限制條件并不相同,,這一點(diǎn)尚未有人進(jìn)行深入的研究和比較。

先進(jìn)封裝技術(shù)是發(fā)展Chiplet的前提,,前面已有論述,。但先進(jìn)封裝技術(shù)和“傳統(tǒng)封裝技術(shù)”的差別其實(shí)和大,,其工藝流程可以相互借鑒的不多。目前先進(jìn)封裝技術(shù)實(shí)際上是掌握在臺積電,、Intel這些傳統(tǒng)被認(rèn)為是“晶圓制造商”(Foundry廠)手中的,,因?yàn)橹薪閷拥募庸て鋵?shí)和“晶圓制造”而非“傳統(tǒng)封裝”更為接近。由于我不太掌握目前國內(nèi)先進(jìn)封裝的技術(shù)能力到底到了哪一步,,對此也不展開闡述,,歡迎有知道的朋友評論區(qū)補(bǔ)充。我只是想強(qiáng)調(diào)的一點(diǎn)是:如果我們在先進(jìn)封裝技術(shù)能力上有差距,,我們需要考慮在布線密度和信號帶寬低于國際先進(jìn)水平的限制下發(fā)展Chiplet技術(shù),,對此我們要有所準(zhǔn)備。

第三個(gè)問題是目前國內(nèi)缺乏大型系統(tǒng)級芯片定義與規(guī)劃人才,,也缺乏有能力規(guī)劃Chiplet的頭部設(shè)計(jì)公司,。這其實(shí)是芯片產(chǎn)業(yè)整體欠賬所導(dǎo)致的。目前國內(nèi)設(shè)計(jì)能力最強(qiáng)的公司是海思,,而海思也曾經(jīng)在2014年就已經(jīng)用Chiplet的方式完成過產(chǎn)品設(shè)計(jì),。根據(jù)公開的文獻(xiàn)報(bào)道,海思的鯤鵬處理器也通過Chiplet的方式實(shí)現(xiàn)處理器的“系列化”,。但除此之外,,還未見有更多的商業(yè)成功案例。從“英偉達(dá)新論文,,透露出GPU設(shè)計(jì)的無奈和未來”一文中可以看出將大的設(shè)計(jì)劃分為多個(gè)Chiplet不但是一個(gè)技術(shù)問題,,更是一個(gè)面向未來的產(chǎn)品規(guī)劃問題。有“復(fù)雜大芯片”設(shè)計(jì)能力和經(jīng)驗(yàn)的公司在國內(nèi)屈指可數(shù),,有決心去規(guī)劃這樣的戰(zhàn)略方向并敢于付諸實(shí)踐的就更少,。

最后一點(diǎn),,就是國內(nèi)缺乏必要的Chiplet積累,,包括技術(shù)積累和產(chǎn)品積累。與Intel,、AMD等頭部IC設(shè)計(jì)公司自身已經(jīng)有非常成熟的復(fù)雜芯片產(chǎn)品不同,,國內(nèi)很多公司依賴于Arm、Synopsys等公司的全家桶產(chǎn)品支持和“保姆式”服務(wù),。還有很大一部分產(chǎn)品走的是“跟研”甚至是“仿制”的路線,,對于復(fù)雜系統(tǒng)芯片的理解和掌控能力非常的弱。很多產(chǎn)品還在對標(biāo)國外“中端”產(chǎn)品,,尚未達(dá)到需要去“切分”的程度,。更不用說具備一些“立等可用”的Chiplet成品。

所以,,在中國發(fā)展Chiplet需要注意目前國內(nèi)實(shí)際的產(chǎn)業(yè)狀態(tài),。一方面Chiplet作為一種新的技術(shù)路線,,確實(shí)給出了在單個(gè)裸片晶體管數(shù)量受限的情況下保持封裝后芯片產(chǎn)品整體晶體管數(shù)量持續(xù)提升的方法;另一方面Chiplet絕不是解決目前國內(nèi)芯片產(chǎn)業(yè)的“萬能神藥”,,其局限和挑戰(zhàn)同樣很大,,還會由于國內(nèi)的特殊情況而導(dǎo)致新的挑戰(zhàn)。

國內(nèi)發(fā)展Chiplet可以采取的路線

通過前面的分析,,大致談了Chiplet技術(shù)產(chǎn)生的原因以及發(fā)展過程中面臨的挑戰(zhàn),,也簡要分析了一下國內(nèi)發(fā)展Chiplet要面臨的一些與國際IC設(shè)計(jì)頭部公司不同的困難。最后,,簡要結(jié)合作者的研究經(jīng)驗(yàn)談一些不太成熟的看法,,供大家參考。

首先是要重點(diǎn)突破“先進(jìn)封裝技術(shù)”,。從前文的分析可以看出,,先進(jìn)封裝技術(shù)是實(shí)施Chiplet技術(shù)的前提。在不能大幅度提升布線密度和信號帶寬的前提下發(fā)展Chiplet技術(shù),,就好像在不具備基礎(chǔ)道路的國家發(fā)展物流產(chǎn)業(yè),,必然要受到極大的限制和阻礙。值得高興的是,,從各種公開報(bào)道和各種渠道的消息來看,,目前國內(nèi)在先進(jìn)封裝技術(shù)上取得了一定的成果。

其次是以要立足于國內(nèi)芯片產(chǎn)業(yè)的現(xiàn)實(shí),,不以拔苗助長,。目前國內(nèi)芯片產(chǎn)業(yè)發(fā)展勢頭良好,但由于長期欠賬導(dǎo)致人才,、技術(shù)都相對匱乏,,短期內(nèi)不具備形成“聚合效應(yīng)”的能力。也缺乏龍頭性企業(yè)帶動下迅速形成“生態(tài)”的可能性,。所以目前現(xiàn)實(shí)的情況只能是各個(gè)企業(yè)根據(jù)自身情況選擇合適的發(fā)展Chiplet技術(shù)的路線,,而不能強(qiáng)行的依靠所謂的“聯(lián)盟”、“標(biāo)準(zhǔn)化組織”搞圈地運(yùn)動甚至強(qiáng)行推廣某個(gè)標(biāo)準(zhǔn)或技術(shù),。要允許有一段“百家爭鳴”的階段,。但后期應(yīng)該以“賽馬制”盡快挑選出能用的“良馬”,發(fā)揮我國“集中力量辦大事”的優(yōu)勢牽引推動產(chǎn)業(yè)鏈整合,。

第三要認(rèn)真研究目前國際頭部IC設(shè)計(jì)公司的Chiplet技術(shù)路線差異,,結(jié)合國內(nèi)各廠商實(shí)際情況形成符合自身產(chǎn)業(yè)晉級的技術(shù)路線。目前各頭部IC設(shè)計(jì)公司的Chiplet技術(shù)路線其實(shí)都有差異,,例如AMD公司的CPU Chiplet+IOD模式,,Intel 的“主Chiplet+外圍Chiplets”模式等等,既建立在自身技術(shù)條件的基礎(chǔ)上也考慮目標(biāo)市場以及產(chǎn)品發(fā)展的具體需求。而目前國內(nèi)面臨的狀況是在舊制程上“堆算力”的問題,,因此“切”的問題要弱于“拼”,。個(gè)人認(rèn)為直接將現(xiàn)有成熟裸芯當(dāng)成Chiplet,搭配必要的外圍Chiplet來構(gòu)建封裝級的異構(gòu)系統(tǒng)可能是目前最為實(shí)際,、最能利用國內(nèi)現(xiàn)有基礎(chǔ)路線,。

最后也是最重要的是應(yīng)學(xué)習(xí)DARPA模式,以國家項(xiàng)目牽引打通上下游產(chǎn)業(yè)鏈的配套,,實(shí)現(xiàn)具有我國特色的Chiplet產(chǎn)業(yè)模式從無到有的轉(zhuǎn)換,。雖然Chiplet在產(chǎn)業(yè)界已有雛形,但不能否認(rèn)的是DARPA著力推動的CHIPS項(xiàng)目對于Chiplet的“催熟”作用,。而我國在目前的國際戰(zhàn)略態(tài)勢下,,更是需要以重大項(xiàng)目牽引,發(fā)揮Chiplet設(shè)計(jì)模式對于設(shè)計(jì)制造流程的優(yōu)化,,凸顯其在小批量,、多場景、系列化芯片產(chǎn)品上的優(yōu)勢,。通過特定產(chǎn)品走通完整的技術(shù)路線,,進(jìn)而初步形成完整的產(chǎn)業(yè)鏈條。

以上就是本人一些不成熟的看法,,歡迎大家批評指正,。由于年底事情較多,導(dǎo)致本文完成的較為匆忙,,對于某些技術(shù)文獻(xiàn)的引用和對技術(shù)名詞的解釋存在一定不規(guī)范的地方,,還請各位讀者見諒。本文在完成過程中受到了中科芯集成電路有限公司的大力支持和幫助,,在此表示誠摯的感謝,。