幾年前,IBM 將其半導(dǎo)體制造業(yè)務(wù)出售給 GLOBALFOUNDRIES,但他們?nèi)栽趭W爾巴尼納米技術(shù)公司擁有價(jià)值數(shù)十億美元的研究設(shè)施。IBM 在諸如 IEDM 之類的會(huì)議上非常活躍,而且這似乎有一個(gè)很好的光管地方,因?yàn)樗麄冊(cè)谶@里公布的研究成果得到了很多媒體的關(guān)注。

在 2019 年的 Litho Workshop 上,我聽到了來自IBM Albany 研究小組的演講,他解釋說 IBM 必須擁有研究線,因?yàn)樗麄冃枰钕冗M(jìn)技術(shù)的處理器來支持他們的設(shè)備運(yùn)行。我個(gè)人質(zhì)疑這個(gè)觀點(diǎn),奧爾巴尼研究小組與三星合作,支持三星投產(chǎn)的 5nm 工藝。

筆者認(rèn)為,三星的 5nm 工藝與臺(tái)積電的 5nm 工藝相比,功耗、性能和密度都相對(duì)較差。我確信在支持 IBM 的過程中有特殊功能,但我也確信無需數(shù)十億美元的研究投資也可以在臺(tái)積電流程中實(shí)現(xiàn)相同的功能。我還認(rèn)為有趣的是,他們說在開發(fā)過程中他們調(diào)高了 EUV 劑量(dose),直到獲得良好的良率,然后他們將其轉(zhuǎn)移給三星,期望三星減少 EUV 劑量。當(dāng)三星開始加速他們的 5nm 工藝時(shí),業(yè)界有傳言稱三星無法通過他們的 EUV 工具獲得足夠的晶圓(高 EUV 劑量導(dǎo)致低產(chǎn)量)并且產(chǎn)量很低。

IBM 每隔幾年也會(huì)通過一些新的發(fā)展在主流媒體上引起轟動(dòng),但在我看來,很多發(fā)展并沒有達(dá)到炒作的效果。例如,IBM 在 2021 年初宣布開發(fā) 2nm 技術(shù),但正如我之前所寫的那樣,它更像臺(tái)積電的 3nm 工藝而不是 2nm,與英特爾和臺(tái)積電預(yù)期的 2nm 工藝相比,不太可能具有競(jìng)爭(zhēng)力。

這并不是說 IBM 不做重要的研究,幾年前他們負(fù)責(zé)包括銅金屬化在內(nèi)的許多關(guān)鍵行業(yè)創(chuàng)新,我只是質(zhì)疑數(shù)十億美元的半導(dǎo)體研究設(shè)施對(duì)于不生產(chǎn)半導(dǎo)體的公司是否有意義.

在本文中,我將討論 IEDM 的三篇 IBM 論文。

第一篇,垂直傳輸納米片技術(shù),用于超越橫向傳輸器件的 CMOS 縮放

在我看來,這篇論文是 IBM 典型的一個(gè)范例,我不希望他們辜負(fù)這個(gè)炒作。在這個(gè)論文中,作者指出,這項(xiàng)工作是與三星合作完成的。主流媒體已經(jīng)發(fā)布了關(guān)于這個(gè)“突破”的消息,好像這將是一個(gè)生產(chǎn)解決方案。

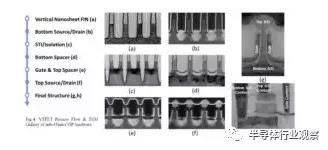

圖 1 說明了垂直傳輸納米片 (VTFET) 工藝。

這里的基本思想是不是在水平方向上制造納米片,而是將它們變成垂直方向。在該論文中,垂直納米片與 FinFET 進(jìn)行了比較,并顯示提供更好的性能和面積。我看到這有兩個(gè)問題。

首先,我的理解是垂直晶體管非常適合 SRAM 的使用,其中互連需求簡單且規(guī)則,但不適用于具有復(fù)雜互連需求的隨機(jī)邏輯設(shè)計(jì)。Imec 之前展示了一些非常有趣的垂直 SRAM 工作,盡管它似乎沒有在行業(yè)中獲得任何關(guān)注。隨著小芯片的出現(xiàn),提供卓越密度的簡單 SRAM 工藝非常有意義。但是再一次,對(duì)于邏輯用途,垂直晶體管面積可能會(huì)增加很多以適應(yīng)互連要求。

我看到的第二個(gè)問題是將它與 FinFET 進(jìn)行比較。從 FinFET 到堆疊水平納米片 (horizontal nanosheets:HNS) 的轉(zhuǎn)變已經(jīng)在進(jìn)行中。HNS 提供了優(yōu)于 FinFET 的密度和性能優(yōu)勢(shì),但更重要的是提供了長期的擴(kuò)展路徑。HNS 可以通過垂直堆疊更多片材來提高性能,它們還提供了引入介電壁(dielectric wall )的機(jī)會(huì),創(chuàng)造了一種名為 Forksheets 的 Imec 創(chuàng)新,減少了 n 到 p 的間距。除此之外,在 3D-CMOS/CFET 架構(gòu)中堆疊 n 和 p HNS 可提供更多的縮放比例,且水平 n 到 p 間距為零。除了 HNS,這些薄片還可以被 2D 材料替代,從而提供更大的縮放比例。驅(qū)動(dòng)電流以及垂直鰭片的性能是由鰭片尺寸驅(qū)動(dòng)的,我看不出這些設(shè)備如何像 HNS 那樣擴(kuò)展。

第二篇,下一代高性能計(jì)算納米片技術(shù)的關(guān)鍵要素

在我看來,這篇論文比上一篇更有趣,因?yàn)樗鉀Q了所有主要前沿邏輯供應(yīng)商都面臨的 HNS 技術(shù)問題。IBM 過去在 HNS 方面做了很多出色的工作,本文以此為基礎(chǔ)。

本文解決了兩個(gè) HNS 問題。

第一個(gè)問題是 HNS 的 pFET 遷移率很差。IBM 之前已經(jīng)描述了兩種提高 pFET 遷移率的技術(shù),一種是在釋放后修整溝道并沉積 SiGe 覆層。另一種技術(shù)是在應(yīng)變松弛緩沖層(strain relaxed buffer layer)上制造溝道。

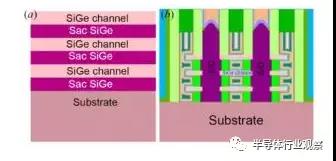

在本文中,SiGe 通道是通過在沉積原始納米片堆疊時(shí)在較高 Ge 含量犧牲層上沉積較低 Ge 含量通道而形成的。Ge 含量的差異是為了啟用選擇性釋放蝕刻,蝕刻掉犧牲膜并保持通道完好無損。SiGe 通道提供了改進(jìn)的遷移率、改進(jìn)的性能和更高的可靠性。

圖 2 說明了 SiGe 通道 HNS pFET。

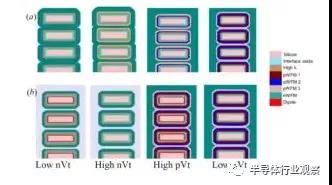

這里解決的第二個(gè)問題是如何為 HNS 實(shí)現(xiàn)多個(gè)均勻的閾值電壓 (Vts)。對(duì)于 FinFET,鰭到鰭的距離相對(duì)較寬,并且可以通過沉積和選擇性去除多種功函數(shù)金屬來實(shí)現(xiàn)多個(gè) Vts。使用 HNS,片到片 (Tsus) 的間距非常小,以至于沒有足夠的空間容納一整堆功函數(shù)金屬。金屬也往往在 NS 外側(cè)更厚,在納米片之間更薄,導(dǎo)致 Vts 不均勻。

IBM 在十多年前率先使用偶極子(dipoles)來控制 VT,該技術(shù)現(xiàn)在正受到 HNS 的廣泛關(guān)注,因?yàn)榕紭O子可以通過摻雜高 k 電介質(zhì)來產(chǎn)生,并且不需要像多功函數(shù)金屬那樣需要額外的厚度. 偶極子還可以解決 Vt 非均勻性問題。

圖 3 說明了功函數(shù)金屬如何導(dǎo)致 Vts 不均勻以及無體積偶極子如何解決該問題。

用于高級(jí)邏輯技術(shù)的基于堆疊式全方位納米片架構(gòu)的后柵極 I/O 晶體管

我想討論的第三篇論文是另一篇研究 HNS 問題的論文。

HNS 實(shí)施的另一個(gè)挑戰(zhàn)是如何創(chuàng)建可以在更高電壓下工作的 I/O 晶體管。在本文中,后柵極工藝流程結(jié)合了沉積氧化物和新型選擇性氧化,產(chǎn)生了兩種不同的柵極氧化物厚度。選擇性氧化產(chǎn)生厚和薄的選擇性氧化物,它們被添加到沉積的氧化物中。該技術(shù)的關(guān)鍵在于,生長的氧化物在氧化過程中會(huì)消耗硅,因此較厚的生長氧化物比生長的薄氧化物消耗更多的硅,從而打開片間間距 (Tsus) 以容納較厚的氧化物。

圖 4 顯示了厚和薄柵氧化層 HNS 器件以及改進(jìn)的 Tsus 以適應(yīng)厚氧化層。

盡管媒體大肆宣傳 IBM 在 IEDM 上發(fā)布的 Vertical-Transport Nanosheet,但我們認(rèn)為 IBM 完善 HNS 流程的工作更有可能對(duì)行業(yè)產(chǎn)生影響。pFET 溝道遷移率、體積更小的 Vt 解決方案和高壓 I/O 解決方案解決了業(yè)界目前正在努力解決的從 FinFET 到 HNS 過渡的問題。