今天早上,,PCI 特別興趣小組 (PCI-SIG) 發(fā)布了期待已久的 PCI Express 6.0 最終 (1.0) 規(guī)范。下一代無處不在的總線再次將 PCIe 通道的數(shù)據(jù)速率提高一倍,,使其在每個(gè)方向上達(dá)到 8GB/秒,,并且對于多通道配置來說要高得多。隨著規(guī)范的最終版本現(xiàn)已整理和批準(zhǔn),,該組織預(yù)計(jì)第一批商業(yè)硬件將在 12 到 18 個(gè)月內(nèi)投放市場,,這實(shí)際上意味著它應(yīng)該在 2023 年開始出現(xiàn)在服務(wù)器中。

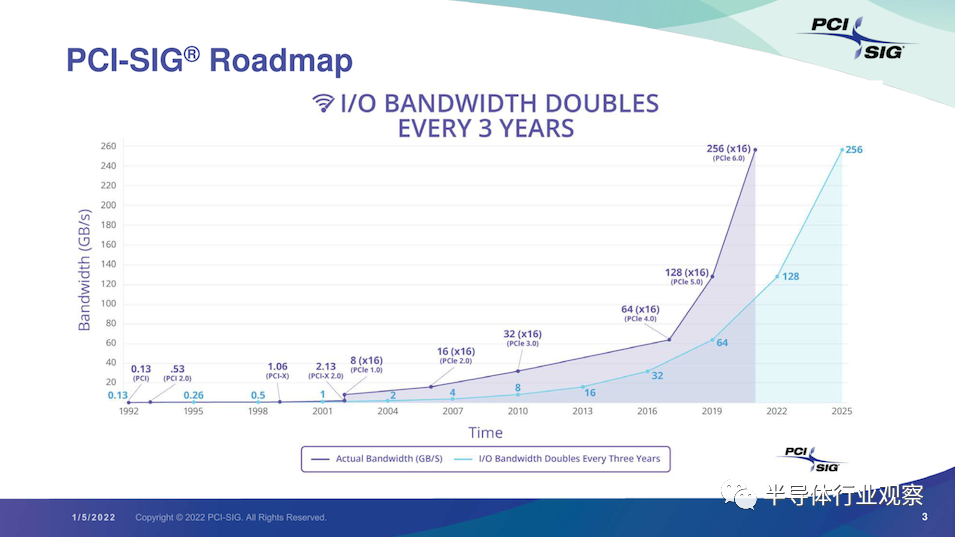

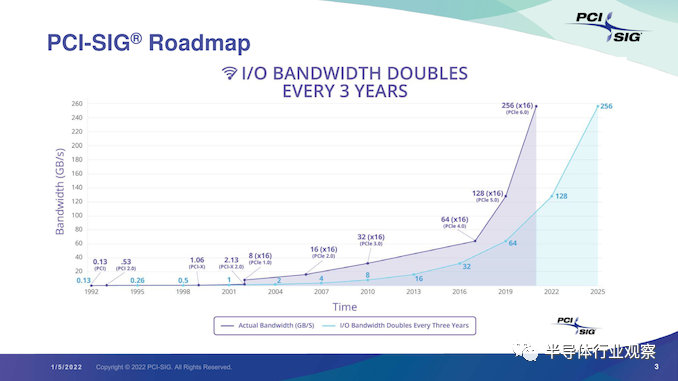

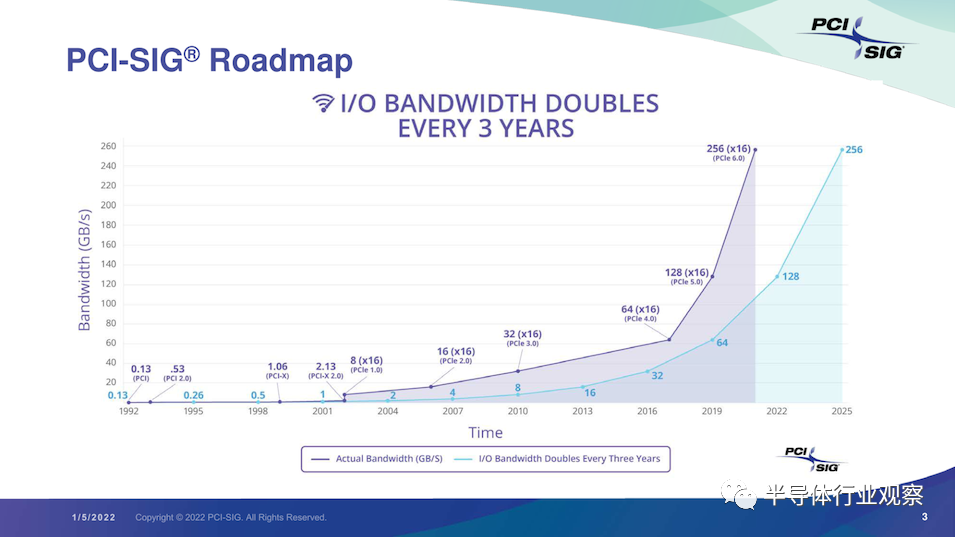

PCI Express 6.0 于 2019 年夏天首次發(fā)布,,顧名思義,,是當(dāng)前一代 PCIe 5.0 規(guī)范的直接后續(xù)產(chǎn)品,。PCI-SIG 的目標(biāo)是大約每 3 年將 PCIe 帶寬翻一番,,一旦 5.0 規(guī)范完成,PCI-SIG 幾乎立即著手開發(fā) PCIe 6.0,,尋找再次將 PCIe 帶寬翻倍的方法,。這些開發(fā)工作的產(chǎn)物是新的 PCIe 6.0 規(guī)范,盡管該組織僅在幾周前就錯(cuò)過了 2021 年末發(fā)布的最初目標(biāo),,但今天他們宣布該規(guī)范已最終確定并將發(fā)布給該組織的成員,。

與往常一樣,更快版本的 PCIe 技術(shù)的創(chuàng)建是由行業(yè)永不滿足的帶寬需求推動的,。由顯卡,、加速器、網(wǎng)卡,、SSD 和其他 PCIe 設(shè)備移動的數(shù)據(jù)量只會繼續(xù)增加,,因此總線速度也必須如此發(fā)展才能保持這些設(shè)備的性能。與該標(biāo)準(zhǔn)的過去版本一樣,,對更快規(guī)范的直接需求來自服務(wù)器運(yùn)營商,,他們已經(jīng)定期使用大量高速硬件。但在適當(dāng)?shù)臅r(shí)候,該技術(shù)也應(yīng)該過濾到消費(fèi)設(shè)備(即個(gè)人電腦),。

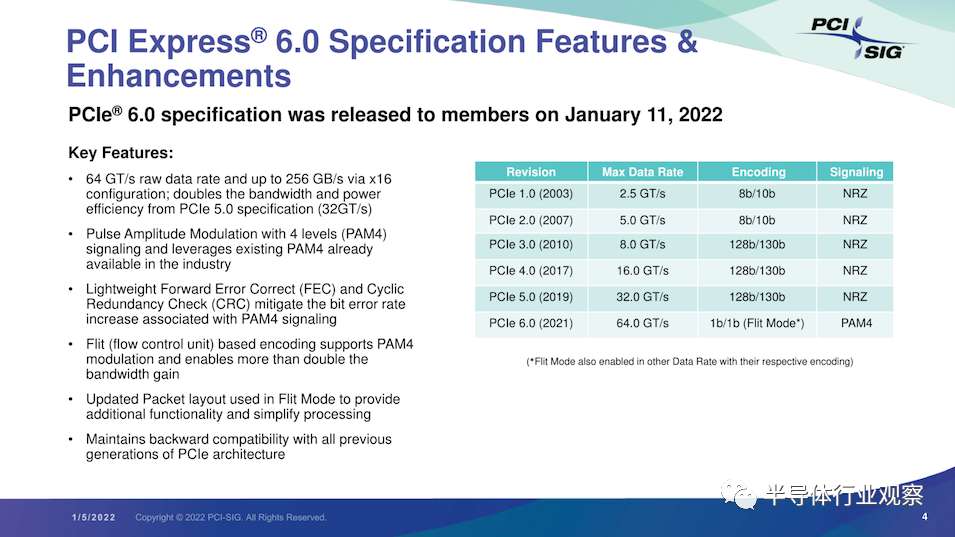

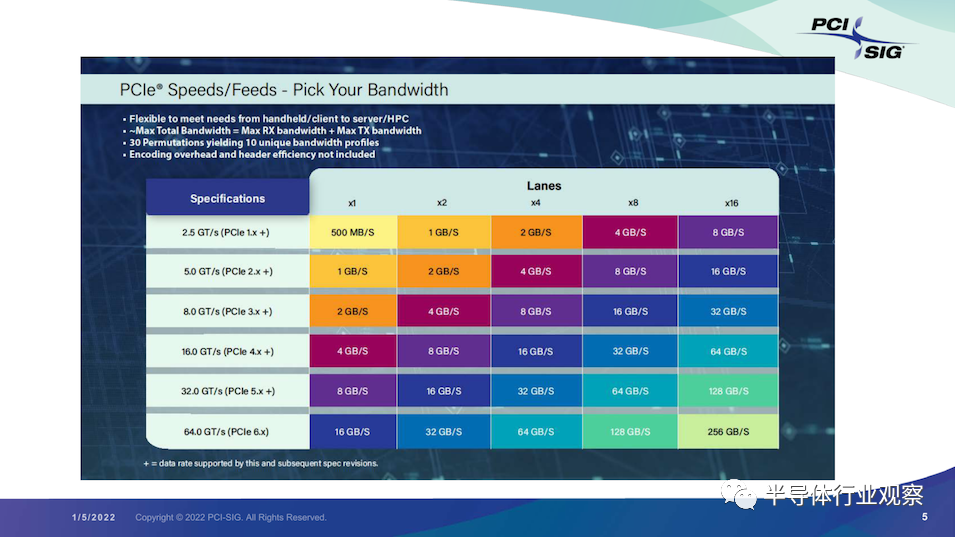

通過將 PCIe 鏈路的速度提高一倍,,PCIe 6.0 實(shí)現(xiàn)了帶寬速率的全面加倍。X1 鏈接從 4GB/秒/方向移動到 8GB/秒/方向,,并且對于完整的 x16 鏈接一直擴(kuò)展到 128GB/秒/方向,。對于已經(jīng)縫合給定寬度的鏈路的設(shè)備,額外的帶寬意味著總線限制的顯著增加,;同時(shí),,對于尚未使鏈路飽和的設(shè)備,PCIe 6.0 提供了減少鏈路寬度,、保持相同帶寬同時(shí)降低硬件成本的機(jī)會,。

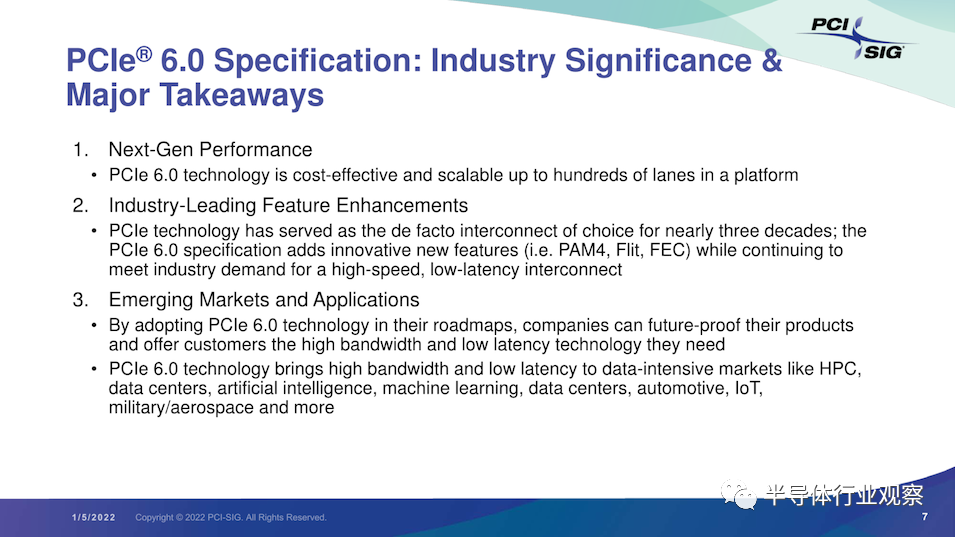

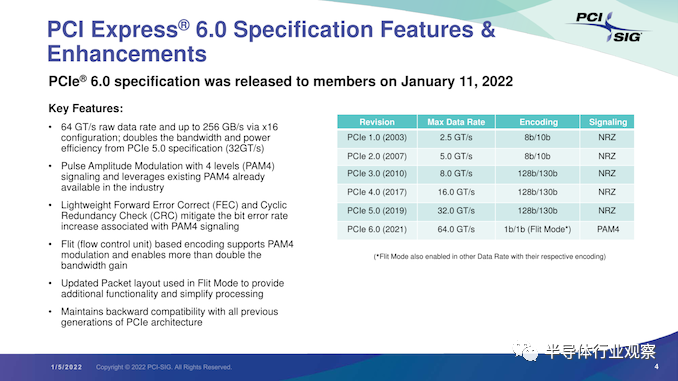

PCI Express 于 2003 年首次推出,今天的 6.0 版本基本上標(biāo)志著該技術(shù)的第三次重大修訂,。雖然 PCIe 4.0 和 5.0 只是對早期信號方法的“擴(kuò)展”——特別是繼續(xù)使用 PCIe 3.0 的 128b/130b 信號和 NRZ——但 PCIe 6.0 進(jìn)行了更重大的改革,,可以說是該標(biāo)準(zhǔn)歷史上最大的一次。

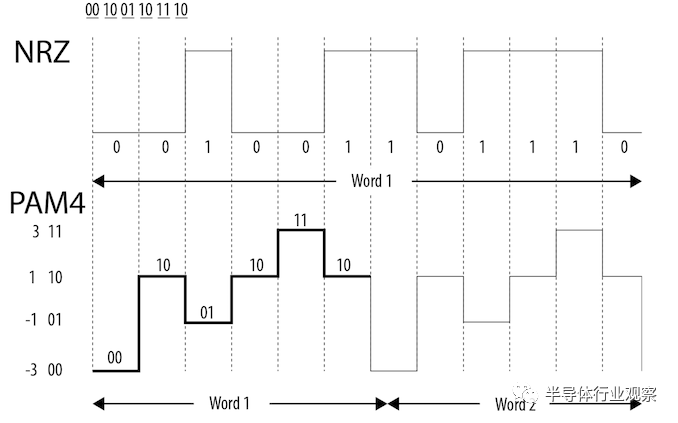

為了使帶寬再次翻倍,,PCI-SIG 徹底顛覆了信號技術(shù),,從一開始就使用的不歸零 (NRZ) 技術(shù)轉(zhuǎn)向脈沖幅度調(diào)制 4 (PAM4)。

正如我們在首次宣布 PCIe 6.0 開發(fā)時(shí)所寫的那樣:

在非常高的水平上,,PAM4 與 NRZ 相比,,是從MLC NAND 手冊中獲取一頁,并將單個(gè)單元(或在本例中為傳輸)將保持的電氣狀態(tài)數(shù)量增加一倍,。與傳統(tǒng)的 0/1 高/低信號不同,,PAM4 使用 4 個(gè)信號電平,因此信號可以編碼為四種可能的兩位模式:00/01/10/11,。這使得 PAM4 可以承載兩倍于 NRZ 的數(shù)據(jù),,而不必將傳輸帶寬加倍,對于 PCIe 6.0 來說,,這將帶來大約 30GHz 的頻率,。

PAM4 本身并不是一項(xiàng)新技術(shù),但到目前為止,,它一直是 200G 以太網(wǎng)等超高端網(wǎng)絡(luò)標(biāo)準(zhǔn)的領(lǐng)域,,其中可用于更多物理通道的空間量更加有限。因此,,業(yè)界在使用信號標(biāo)準(zhǔn)方面已經(jīng)有幾年的經(jīng)驗(yàn),,并且隨著自身帶寬需求的不斷增長,PCI-SIG 決定將其帶入機(jī)箱中,,以下一代 PCIe 為基礎(chǔ),。

使用 PAM4 的代價(jià)當(dāng)然是成本。即使每赫茲帶寬更大,PAM4 目前在幾乎每個(gè)級別上的實(shí)施成本都更高,,從PHY到物理層,。這就是為什么它沒有風(fēng)靡全球,以及為什么 NRZ 繼續(xù)在其他地方使用的原因,。PCIe 的大規(guī)模部署規(guī)模當(dāng)然會在這里大有幫助——規(guī)模經(jīng)濟(jì)仍然很重要——但是一旦 PCIe 6.0 處于上升階段,,看看幾年后的情況將會很有趣。

同時(shí),,與我之前的類比中的 MLC NAND 不同,,由于附加的信號狀態(tài),PAM4 信號本身比 NRZ 信號更脆弱,。這意味著與 PAM4 一起,,PCIe 歷史上第一次該標(biāo)準(zhǔn)還獲得了前向糾錯(cuò) (FEC)。名副其實(shí),,前向糾錯(cuò)是一種通過提供恒定的糾錯(cuò)數(shù)據(jù)流來糾正鏈路中的信號錯(cuò)誤的方法,,它已經(jīng)普遍用于數(shù)據(jù)完整性至關(guān)重要且沒有時(shí)間重新傳輸?shù)那闆r下(例如作為帶 DSC 的 DisplayPort 1.4)。雖然到目前為止 PCIe 還不需要 FEC,,但 PAM4 的脆弱性將改變這一點(diǎn),。包含 FEC 不應(yīng)該對最終用戶產(chǎn)生明顯的影響,但對于 PCI-SIG,,這是另一個(gè)需要應(yīng)對的設(shè)計(jì)要求,。

值得注意的是,F(xiàn)EC 還與循環(huán)冗余校驗(yàn) (CRC) 配對,,作為防止誤碼的最后一層,。即使在 FEC 仍然未能通過 CRC(因此仍然是損壞的)的數(shù)據(jù)包將觸發(fā)數(shù)據(jù)包的完全重傳。

切換到 PAM4 的結(jié)果是,,通過在不增加頻率的情況下增加傳輸?shù)臄?shù)據(jù)量,,信號損失要求不會上升。PCIe 6.0 將具有與 PCIe 5.0 相同的 36dB 損耗,,這意味著雖然標(biāo)準(zhǔn)并未正式定義走線長度,但 PCIe 6.0 鏈路應(yīng)該能夠達(dá)到與 PCIe 5.0 鏈路一樣遠(yuǎn)的距離,。這無疑讓供應(yīng)商和工程師都松了一口氣,。

除了 PAM4 和 FEC,PCIe 6.0 的最后一項(xiàng)主要技術(shù)補(bǔ)充是它的流量控制單元(FLow control unIT:FLIT) 編碼方式,。不要與物理層的 PAM4 混淆,,F(xiàn)LIT 編碼用于邏輯層,將數(shù)據(jù)分解為固定大小的數(shù)據(jù)包,。通過將邏輯層移動到固定大小的數(shù)據(jù)包,,PCIe 6.0 能夠?qū)崿F(xiàn) FEC 和其他糾錯(cuò)方法,因?yàn)檫@些方法需要所述固定大小的數(shù)據(jù)包。FLIT 編碼本身并不是一項(xiàng)新技術(shù),,但與 PAM4 一樣,,本質(zhì)上是從已經(jīng)使用的高速網(wǎng)絡(luò)領(lǐng)域借來的。而且,,根據(jù) PCI-SIG,,它是規(guī)范中最重要的部分之一,因?yàn)樗菃⒂茫ǔ掷m(xù))具有 FEC 的 PCIe 低延遲操作的關(guān)鍵部分,,并且允許非常小的開銷,。總而言之,,PCI-SIG 認(rèn)為 PCIe 6.0 編碼是一種 1b/1b 編碼方法,,

由于它更像是一個(gè)啟用部分而不是規(guī)范的一個(gè)特性,因此 FLIT 編碼對用戶來說應(yīng)該是相當(dāng)不可見的,。然而,,需要注意的是,PCI-SIG 認(rèn)為 FLIT 編碼在某種意義上也被向后移植以降低鏈路速率非常重要/有用,。一旦在鏈路上啟用 FLIT,,鏈路將始終保持 FLIT 模式,即使鏈路速率協(xié)商下降,。因此,,例如,如果 PCIe 6.0 顯卡要從 64 GT/s (PCIe 6.0) 速率下降到 2.5GT/s (PCIe 1.x) 速率以節(jié)省空閑時(shí)的電量,,則鏈路本身仍將是在 FLIT 模式下運(yùn)行,,而不是回到完整的 PCIe 1.x 樣式鏈接。這既簡化了規(guī)范的設(shè)計(jì)(不必重新協(xié)商超出鏈路速率的連接),,又允許所有鏈路速率受益于 FLIT 的低延遲和低開銷,。

與往常一樣,PCIe 6.0 向后兼容早期規(guī)范,;因此舊設(shè)備將在較新的主機(jī)上運(yùn)行,,而較新的設(shè)備將在較舊的主機(jī)上運(yùn)行。此外,,目前的連接器形式仍然受到支持,,包括無處不在的 PCIe 卡邊緣連接器。因此,,雖然對規(guī)范的支持需要內(nèi)置到新一代設(shè)備中,,但它應(yīng)該是一個(gè)相對簡單的過渡,就像前幾代技術(shù)一樣,。

不幸的是,,PCI-SIG 無法為我們提供太多指導(dǎo),,說明這對實(shí)施意味著什么,特別是在消費(fèi)者系統(tǒng)中——該小組只是制定標(biāo)準(zhǔn),,由硬件供應(yīng)商來實(shí)施,。因?yàn)榍袚Q到 PAM4 意味著給定走線長度的信號損失量沒有增加,從概念上講,,放置 PCIe 6.0 插槽應(yīng)該與放置 PCIe 5.0 插槽一樣靈活,。也就是說,我們將不得不拭目以待,,看看 AMD 和英特爾在未來幾年會設(shè)計(jì)出什么,。能夠做某事,以及能夠在消費(fèi)者硬件預(yù)算上做這件事并不總是一回事,。

總結(jié)一下,,隨著 PCIe 6.0 規(guī)范最終完成,PCI-SIG 告訴我們,,根據(jù)之前的采用時(shí)間表,,我們應(yīng)該會在 12 到 18 個(gè)月內(nèi)看到符合 PCIe 6.0 的硬件上市。實(shí)際上,,這意味著我們應(yīng)該在明年看到第一個(gè)服務(wù)器設(shè)備,,然后可能再過一兩年用于消費(fèi)設(shè)備。

附:發(fā)布會PPT