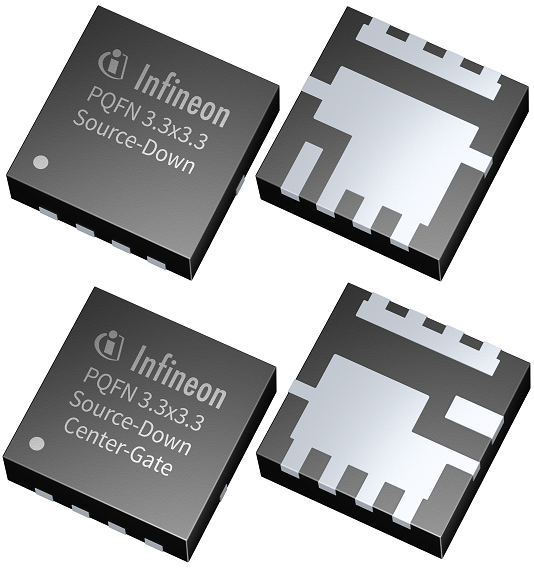

【2022年2月15日,德國慕尼黑訊】高功率密度、出色的性能和易用性是當前電源系統(tǒng)設計的關鍵要求。為此,英飛凌科技股份公司(FSE: IFX / OTCQX: IFNNY)推出了新一代OptiMOS? 源極底置(Source-Down,簡稱SD)功率MOSFET,為解決終端應用中的設計挑戰(zhàn)提供切實可行的解決方案。該功率MOSFET采用PQFN 封裝,尺寸為3.3 x 3.3 mm2,支持從25 V到100 V的寬電壓范圍。此種封裝可實現(xiàn)更高的效率、更高的功率密度以及業(yè)內(nèi)領先的熱性能指標,并降低BOM成本,在功率MOSFET的性能方面樹立了新的行業(yè)標桿。該器件的應用領域十分廣泛,涵蓋電機驅動,適用于服務器、電信和OR-ing的SMPS,以及電池管理系統(tǒng)等。

與傳統(tǒng)的漏極底置(Drain-Down)封裝相比,最新的源極底置封裝技術能夠讓器件的外形尺寸接近于裸芯片。此外,這種創(chuàng)新封裝技術還能降低損耗,進一步增強器件的整體性能。相較于最先進的漏極底置封裝,采用源極底置封裝可使RDS(on)降低30%。這一技術創(chuàng)新能夠為系統(tǒng)設計帶來的主要優(yōu)勢包括:縮小外形尺寸,從SuperSO8 5 x 6 mm2封裝轉變到PQFN 3.3 x 3.3 mm2封裝,可減少約65%的占位空間,讓可用空間得到更有效的利用,從而提高終端系統(tǒng)的功率密度和系統(tǒng)效率。

此外,在源極底置封裝中,熱量通過導熱墊傳遞到PCB上,而非通過內(nèi)部引線鍵合或銅夾帶設計,以此來改善散熱效果。這也使得結-殼熱阻(RthJC)從1.8K/W降到了1.4K/W,降幅超過20%,從而能夠實現(xiàn)優(yōu)異的熱性能。英飛凌目前推出的兩個型號占板面積不同,它們分別是SD標準門極布局和SD門極居中布局。在標準門極布局中,電氣連接的位置保持不變,方便將標準的漏極底置封裝簡單直接地替換成新的源極底置封裝;而在中央門極布局封裝中,門極引腳被移到中心位置以便于多個MOSFET并聯(lián)。這兩種型號都能夠優(yōu)化PCB布局,使得寄生效應降低,PCB損耗改進,且易于使用。

供貨情況

OptiMOS? 源極底置功率MOSFET現(xiàn)已開始供貨,其采用PQFN 3.3 x 3.3 mm2封裝,支持從25 V到100 V的寬電壓范圍,目前推出的兩個型號占板面積不同。