問題:

何種頻率產(chǎn)生器件適合我的應(yīng)用?

答案:

了解頻率產(chǎn)生器件的性能特征對于為目標使用場景確定正確的解決方案至關(guān)重要。這是一個快速指南,旨在幫助RF系統(tǒng)工程師熟悉整個選擇流程。

主要性能判據(jù)

我們首先定義表征頻率產(chǎn)生器件性能通常使用的判據(jù)。選擇流程一般從最基本的判據(jù)開始,那就是輸出頻率范圍。為了生成整個頻譜范圍內(nèi)的頻率,人們設(shè)計了各種各樣的器件,支持從單音到跨越多個倍頻程的頻率。然而,當根據(jù)輸出頻率選擇器件時,必須注意到,寬帶和高頻能力常被用來交換其他基本特性,包括頻率穩(wěn)定性、輸出頻譜純度和開關(guān)速度。

頻率穩(wěn)定性代表輸出信號的短期和長期變化。短期穩(wěn)定性與遠小于一個完整信號周期的變化有關(guān)。這些變化以相位抖動和相位噪聲表示。相位抖動定義時域中信號相位的微小波動,相位噪聲是其頻譜表示,由相對于載波頻率的不同偏移頻率下1 Hz帶寬中包含的相對噪聲功率水平來描述。如果頻率變化發(fā)生在較長時間段內(nèi),我們通常會使用長期穩(wěn)定性來描述,它是指由于溫度、負載條件、老化等各方面導致的輸出頻率漂移(通常用ppm表示)。

頻譜純度是器件選擇流程中要考慮的另一個重要特性。它由器件輸出頻譜中存在的雜散成分來描述,通常用相對于基頻水平表示的諧波水平和饋通分量來量化。

除了輸出信號的穩(wěn)定性和頻譜純度之外,開關(guān)速度(也稱為建立時間或鎖定時間)是又一個典型的權(quán)衡參數(shù),選擇最優(yōu)頻率產(chǎn)生器方案時需要予以考慮。它描述器件從一個頻率切換到另一個頻率所需的時間,此要求可能會因最終應(yīng)用而有很大差異。

器件的主要類型

上面定義了用于表征頻率產(chǎn)生器件的主要性能判據(jù),現(xiàn)在我們簡要說明其主要類型,這些類型旨在提供與這些判據(jù)相關(guān)的不同特性組合。此概述最終應(yīng)作為選擇正確類型器件以滿足目標應(yīng)用需求的指南。

晶體(XTAL)振蕩器(XO)使用壓電諧振器(通常為石英)產(chǎn)生幾千赫茲至幾百兆赫茲的固定輸出頻率。有一種特殊類型的XO,稱為壓控晶體振蕩器(VCXO),它允許改變頻率,但只能改變很小的量以支持微調(diào)。XO是具有極高Q因子(可超過 100,000)的機電換能器,可產(chǎn)生非常穩(wěn)定且相位噪聲非常低的輸出頻率。XO的最大輸出頻率和調(diào)諧能力有限,但是,當需要為其他類型的器件提供單一精確參考以獲得更高頻率時,它是出色的選擇。

壓控振蕩器(VCO)是一種不同類型的頻率產(chǎn)生器件,依賴于LC諧振電路。與晶體相比,電氣電路元件的Q因子要低得多(通常低1000倍),但它可以實現(xiàn)高得多的輸出頻率和寬調(diào)諧范圍。VCO產(chǎn)生的輸出信號頻率由外部輸入電壓控制。VCO的內(nèi)核可以使用不同的諧振電路。使用高Q諧振器的單核VCO可在有限頻率范圍內(nèi)提供低相位噪聲性能,而較低Q因子的振蕩器以寬帶操作為目標,噪聲特性很一般。使用多個切換式高Q諧振器電路的多頻段VCO是一種折衷解決方案,既支持寬帶操作,又能提供低相位噪聲性能,但其代價是調(diào)諧速度較慢,因為切換不同的核需要時間。VCO是一種出色的全方位解決方案,但它一般不能提供穩(wěn)定的輸出信號,這就是為什么VCO經(jīng)常與鎖相環(huán)(PLL)配合使用以提高輸出頻率穩(wěn)定性的原因1。

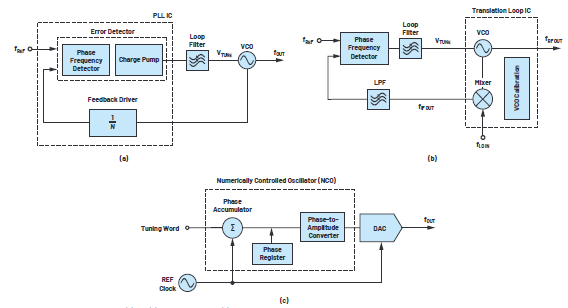

鎖相環(huán)(PLL)或PLL頻率合成器可確保許多頻率合成和時鐘恢復應(yīng)用所需的VCO輸出頻率穩(wěn)定。如圖1a所示,PLL包含鑒相器,其將VCO頻率的N分頻與參考頻率進行比較,并使用該差值輸出信號調(diào)節(jié)施加于VCO調(diào)諧線路的DC控制電壓。這使得任何頻率漂移都能得到即時校正,因而振蕩器能夠保持穩(wěn)定工作。典型的PLL IC包含誤差檢測器(帶電荷泵的鑒頻鑒相器或PFD)和反饋分頻器(參見圖1a中的虛線區(qū)域),另外還需要外部環(huán)路濾波器、精密參考頻率和VCO以構(gòu)成一個完整的反饋系統(tǒng),從而產(chǎn)生穩(wěn)定的頻率。使用集成VCO的頻率合成器IC可以大大簡化該系統(tǒng)的實現(xiàn)1,2。

集成VCO的頻率合成器將PLL和VCO組合在單個封裝中,只需要外部參考和環(huán)路濾波器就能實現(xiàn)所需的功能。集成式PLL頻率合成器是一種多功能解決方案,具有廣泛的數(shù)字控制設(shè)置,支持產(chǎn)生精確頻率。它常常包含集成功分器、倍頻器、分頻器和跟蹤濾波器,頻率覆蓋范圍超越了VCO的基頻范圍,達到數(shù)個倍頻程。所有這些元件的內(nèi)在參數(shù)決定了輸出頻率范圍、相位噪聲、抖動、鎖定時間和其他表示頻率合成電路總體性能的特性1。

轉(zhuǎn)換環(huán)路是基于PLL概念的另一類頻率合成器,但采用不同的方法實現(xiàn)。如圖1b所示,其反饋環(huán)路中使用的是集成下變頻混頻級,而不是N分頻器,環(huán)路增益設(shè)置為1,帶內(nèi)相位噪聲極小。轉(zhuǎn)換環(huán)路IC(參見圖1b中的虛線區(qū)域)專為對抖動高度敏感的應(yīng)用而設(shè)計,并與外部PFD和LO組合使用,以緊湊的尺寸實現(xiàn)完整的頻率合成解決方案,提供儀表級性能1。

直接數(shù)字頻率合成器(DDS)是集成PLL頻率合成器的替代方案,采用不同的原理實現(xiàn)。基本DDS架構(gòu)的原理圖如圖1c所示。它是一種數(shù)字控制系統(tǒng),包括表示時鐘信號的高精度參考頻率、創(chuàng)建目標波形數(shù)字版本的數(shù)字控制振蕩器(NCO)以及提供最終模擬輸出的數(shù)模轉(zhuǎn)換器(DAC)。DDS IC提供非常快的開關(guān)速度、精細的頻率和相位分辨率以及低輸出失真,因此特別適合于出色噪聲性能和高頻率捷變性至關(guān)重要的應(yīng)用1,3。

結(jié)論

頻率產(chǎn)生器件應(yīng)用廣泛,可實現(xiàn)各種功能,包括變頻、波形合成、信號調(diào)制和時鐘信號產(chǎn)生。針對最終應(yīng)用施加的不同要求,需要設(shè)計不同類型的頻率產(chǎn)生器件,本文簡要說明了這些器件的主要類型。例如,通信系統(tǒng)需要低帶內(nèi)噪聲以維持低誤差矢量幅度(EVM),頻譜分析儀依賴于具有快速鎖定時間的本振來實現(xiàn)快速頻率掃描,高速轉(zhuǎn)換器需要低抖動時鐘以確保高SNR性能。

圖1.(a) PLL、(b) 轉(zhuǎn)換環(huán)路、(c) DDS的簡化框圖

ADI公司提供非常豐富的RF集成電路產(chǎn)品組合,支持信號鏈中的幾乎所有功能模塊。ADI產(chǎn)品提供一流的性能,可滿足廣泛RF應(yīng)用——從通信和工業(yè)系統(tǒng)一直到測試測量設(shè)備和航空航天系統(tǒng)——的最苛刻要求。

參考資料

1 Anton Patyuchenko. “RF Signal Chain Discourse—Part 2: Essential Building Blocks.” Analog Dialogue, Vol. 55, No. 3, July 2021.

Anton Patyuchenko。“解密RF信號鏈—第2部分:基本構(gòu)建模塊”。《模擬對話》,第55卷第3期,2021年7月。

2 Ian Collins and David Mailloux. “Revolution and Evolution in Frequency Synthesis: How PLL/VCO Technology Has Increased Performance, Decreased Size, and Simplified Design Cycle.” Analog Devices, Inc., January 2020.

Ian Collins和David Mailloux。“頻率合成技術(shù)的變革和發(fā)展:PLL/VCO技術(shù)如何提升性能、減小尺寸并簡化設(shè)計周期”。ADI公司,2020年1月。

3 Jim Surber and Leo McHugh. “Single-Chip Direct Digital Synthesis vs. the Analog PLL.” Analog Dialogue, Vol. 30, No. 3, July 1996.

Jim Surber和Leo McHugh。“單芯片直接數(shù)字頻率合成與模擬PLL”。《模擬對話》,第30卷第3期,1996年7月。

作者簡介

Anton Patyuchenko于2007年獲得慕尼黑技術(shù)大學微波工程碩士學位。畢業(yè)之后,Anton曾在德國航空航天中心(DLR)擔任科學家。他于2015年加入ADI公司擔任現(xiàn)場應(yīng)用工程師,目前為ADI公司戰(zhàn)略與重點客戶提供現(xiàn)場應(yīng)用支持,主要負責RF應(yīng)用。