應(yīng)用材料公司以技術(shù)助力極紫外光和三維環(huán)繞柵極晶體管實(shí)現(xiàn)二維微縮

2022-04-22

來源:應(yīng)用材料

2022 年 4 月 21 日,加利福尼亞州圣克拉拉市——應(yīng)用材料公司推出了旨在幫助客戶利用極紫外光(EUV)繼續(xù)推進(jìn)二維微縮的多項(xiàng)創(chuàng)新技術(shù),并詳細(xì)介紹了業(yè)內(nèi)最廣泛的下一代三維環(huán)繞柵極晶體管制造技術(shù)的產(chǎn)品組合。

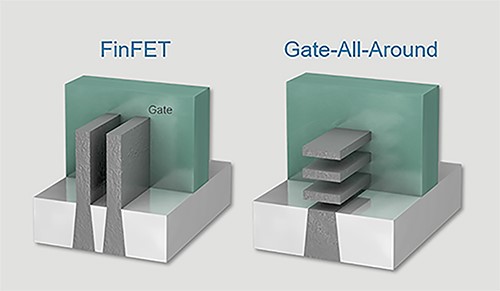

環(huán)繞柵極(GAA)晶體管將成為自2010年FinFETs問世以來芯片行業(yè)最大的設(shè)計(jì)轉(zhuǎn)變之一

材料工程的創(chuàng)新為GAA晶體管提供了功率和性能的提升

要在未來若干年內(nèi)提升晶體管密度,芯片制造商正在尋求互補(bǔ)的兩條道路。其一是延續(xù)傳統(tǒng)的摩爾定律二維微縮,也就是使用 EUV光刻和材料工程打造出更小的特征。另一條則是使用設(shè)計(jì)技術(shù)協(xié)同優(yōu)化(DTCO)和三維技巧,對邏輯單元布局進(jìn)行巧妙優(yōu)化,這樣無需對光刻柵距進(jìn)行任何更改即可增加密度。后一種方法包括后段連線和環(huán)繞柵極(GAA)晶體管,即使面臨傳統(tǒng)二維微縮的減緩,仍將有力推動邏輯密度在未來幾年內(nèi)的持續(xù)增長。通過將這些技術(shù)有機(jī)結(jié)合,可以幫助芯片制造商完成邏輯芯片在未來的迭代進(jìn)化,同時(shí)實(shí)現(xiàn)功率、性能、面積、成本和上市時(shí)間(即 PPACt)的同步改善。

應(yīng)用材料公司高級副總裁、半導(dǎo)體產(chǎn)品事業(yè)部總經(jīng)理珀拉布?拉賈博士表示:“應(yīng)用材料公司的核心戰(zhàn)略是成為賦能客戶的PPACt賦能企業(yè)?,依托我們現(xiàn)有的七大創(chuàng)新,支持客戶利用EUV繼續(xù)推進(jìn)二維微縮。同時(shí),我們還詳細(xì)介紹了GAA晶體管的顛覆性制造方法,該方法與現(xiàn)今FinFET晶體管截然不同。不僅如此,應(yīng)用材料公司已經(jīng)準(zhǔn)備好了覆蓋范圍最廣泛的GAA制造產(chǎn)品線,包含涉及外延生長、原子層沉積和選擇性材料刻蝕的全新生產(chǎn)步驟,以及兩項(xiàng)全新的用于制造理想GAA氧化柵極和金屬柵極的集成材料解決方案(Integrated Materials Solutions?)。”

二維微縮的擴(kuò)展

極紫外光(EUV)光刻的出現(xiàn)使芯片制造商得以產(chǎn)出更小的特征,并增加晶體管密度。但行業(yè)目前的現(xiàn)狀是:要繼續(xù)利用EUV進(jìn)行微縮困難重重,迫切需要全新的沉積、刻蝕和量測方法。

完成EUV光刻膠顯影后,需要先通過稱為過渡層和硬掩模的一系列中間層對芯片圖形進(jìn)行刻蝕,隨后才能將其最終刻蝕到晶圓上。迄今為止,這些中間層都是使用旋涂技術(shù)來進(jìn)行沉積的。今日,應(yīng)用材料公司推出使用該公司的Precision化學(xué)氣相沉積系統(tǒng)來進(jìn)行沉積,適用于EUV的 Stensar? 先進(jìn)圖形鍍膜(Stensar? Advanced Patterning Film for EUV)。相較于旋涂沉積,應(yīng)用材料公司的CVD膜可幫助客戶對EUV硬掩模層進(jìn)行微調(diào),使其達(dá)到特定厚度和刻蝕彈性,以便在整個晶圓上EUV圖形傳輸時(shí)達(dá)成接近完美的均勻性。

應(yīng)用材料公司還詳解了其Sym3? Y刻蝕系統(tǒng)的特殊功能,即允許客戶在相同反應(yīng)腔內(nèi)進(jìn)行材料刻蝕和沉積,這樣可先改善EUV圖形,再將其刻蝕到晶圓上。Sym3反應(yīng)腔會輕輕移除EUV光刻膠材質(zhì),然后以特殊方式重新進(jìn)行材料沉積,使圖形變均勻,從而消除因“隨機(jī)誤差”而產(chǎn)生的圖形易變性。改善后的EUV圖形可提高良率、降低芯片功耗并提升其性能。因此,位居DRAM市場中導(dǎo)體刻蝕系統(tǒng)首要供應(yīng)商位置的應(yīng)用材料公司,正在憑借其Sym3技術(shù)的飛速發(fā)展,將客戶群體從存儲器領(lǐng)域拓展到晶圓代工廠/邏輯芯片領(lǐng)域。

應(yīng)用材料公司還展示了如何將其PROVision? eBeam量測技術(shù)用于深入觀察多層芯片內(nèi)部,以便精確測量整個晶圓上的EUV圖形化特征,幫助客戶解決其他量測技巧可能無法診斷的“邊緣布局錯誤”。應(yīng)用材料公司2021年電子束系統(tǒng)的營收幾乎翻倍,使其躍居電子束技術(shù)供應(yīng)商榜首的位置。

三維環(huán)繞式柵極晶體管工藝設(shè)計(jì)

新興的GAA晶體管為客戶示范了如何利用三維設(shè)計(jì)技巧和DTCO布局創(chuàng)新來對二維微縮加以補(bǔ)充,即使二維微縮速度放緩,仍可快速提升邏輯密度。材料工程領(lǐng)域的創(chuàng)新同時(shí)還有助于GAA晶體管降低功耗和提升性能。

在FinFET中,構(gòu)成晶體管電子路徑的垂直溝道是由光刻和刻蝕來形成的,這種工藝會導(dǎo)致溝道寬度不均勻。而這種不均勻性則會對功耗和性能產(chǎn)生不利影響,這也是客戶轉(zhuǎn)投GAA的另一個主要原因。

GAA晶體管看上去就像是FinFET晶體管旋轉(zhuǎn)了90度,使溝道從垂直變?yōu)樗健AA溝道是通過使用外延生長和選擇性材料刻蝕來形成的,這種技術(shù)使客戶得以精確設(shè)計(jì)寬度,實(shí)現(xiàn)寬度均勻,從而獲得最優(yōu)功耗和性能。外延生長系統(tǒng)恰恰是應(yīng)用材料公司的首項(xiàng)產(chǎn)品,自此之后,它便一躍成為市場領(lǐng)頭羊。2016年,應(yīng)用材料公司發(fā)布Selectra?系統(tǒng)并在其中率先啟用選擇性材料刻蝕技術(shù),迄今已提供1000余個反應(yīng)腔給客戶使用,并位居市場領(lǐng)袖地位。

GAA晶體管的主要制造挑戰(zhàn)在于溝道間距僅約10納米,在如此微小的空間內(nèi),客戶必須在圍繞各溝道的全部四周進(jìn)行多層氧化柵極和金屬柵極堆疊的沉積。

應(yīng)用材料公司專為氧化柵極堆疊開發(fā)了IMS?(集成材料解決方案)系統(tǒng),通過將氧化柵極變薄,增加了驅(qū)動電流并提升晶體管性能。但氧化柵極越薄,通常就會導(dǎo)致漏電流越高,造成功耗浪費(fèi)和發(fā)熱。應(yīng)用材料公司全新的IMS?系統(tǒng)將等效氧化層厚度降低1.5埃,使設(shè)計(jì)師無需增加?xùn)艠O漏電流即可提升性能,或者在保持性能不變的前提下,使柵極漏電流減小至原先的十分之一以下。它將原子層沉積(ALD)、熱處理步驟、等離子處理步驟和量測整合到單一高真空系統(tǒng)內(nèi)。

應(yīng)用材料公司還展示了IMS系統(tǒng),該系統(tǒng)用于GAA金屬柵極的工藝,支持客戶借由調(diào)整柵極厚度來微調(diào)晶體管閾值電壓,以滿足從電池供電式移動設(shè)備到高性能服務(wù)器在內(nèi)的各種特定計(jì)算應(yīng)用的每瓦特功耗性能目標(biāo)。它可在高度真空環(huán)境內(nèi)執(zhí)行高精度金屬原子層沉積步驟以防止空氣污染。

應(yīng)用材料公司已經(jīng)在4月21日舉辦的“全新微縮之旅”大師課上,提供了有關(guān)其邏輯微縮解決方案的更多詳情。