1. 概述

對于現(xiàn)今的FPGA芯片供應商,在提供高性能和高集成度獨立FPGA芯片和半導體知識產權(IP)產品的同時,還需要提供性能卓越且便捷易用的開發(fā)工具。本文將以一家領先的FPGA解決方案提供商Achronix為例,來分析FPGA開發(fā)工具套件如何與其先進的硬件結合,幫助客戶創(chuàng)建完美的、可在包括獨立FPGA芯片和帶有嵌入式FPGA(eFPGA)IP的ASIC或者SoC之間移植的開發(fā)成果。

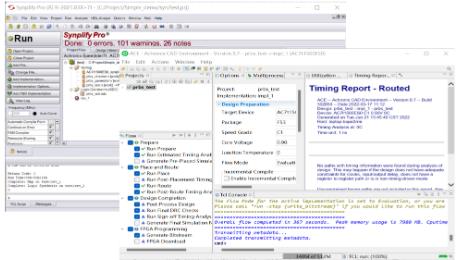

隨著人工智能、云計算、邊緣計算、智能駕駛和5G等新技術在近幾年異軍突起,也推動了FPGA技術的快速發(fā)展,如Achronix的Speedster7t獨立FPGA芯片不僅采用了7nm的工藝,而且還帶有二維片上網(wǎng)絡(2D NoC)和機器學習處理器(MLP)來支持高通量數(shù)據(jù)的流動和處理。同時,Achronix的Speedcore eFPGA IP也被很多全球領先科技公司集成到其ASIC或者SoC中。Achronix也推出了其ACE開發(fā)工具套件來同時支持這些產品,如圖1所示。它不僅提供了先進的開發(fā)功能和資源管理能力,還集成了最新的Synplify Pro軟件。

圖1 Achronix ACE開發(fā)工具套件

Achronix的ACE開發(fā)工具套件是一套最先進的設計工具鏈,可為Achronix的所有硬件產品提供支持。ACE與業(yè)界標準的邏輯綜合工具配合使用,可支持FPGA設計人員便捷地將其設計映射到Speedster7t FPGA、Speedcore eFPGA中。這也意味著Achronix的用戶可以根據(jù)其應用的規(guī)模,在Speedster7t、搭載該芯片的VectorPath加速卡、以及帶有Speedcore的SoC或者ASIC中選擇最佳的產品形態(tài)和路線圖。

ACE包括了為Achronix優(yōu)化的Synopsys的Synplify-Pro工具。Achronix仿真邏輯庫也獲得了Mentor的ModelSim、Synopsys的VCS等主流仿真工具的支持,設計人員還可以使用功能強大的布局規(guī)劃工具(floorplanner)進行設計優(yōu)化,并且在進入時序驅動的布局布線之前為所有設計模塊實例分配區(qū)域或位置。

ACE還包括一個關鍵的時序路徑分析工具,可以分析時序以確保設計符合性能要求。設計人員還可以使用ACE強大的Snapshot嵌入式邏輯分析器來創(chuàng)建復雜的觸發(fā)條件,并顯示在Speedster7t器件中運行的信號。

總之,ACE開發(fā)工具套件可以覆蓋FPGA設計開發(fā)、編譯到調試所有的必備功能。

2. ACE中集成的時序路徑分析工具

時序分析是FPGA開發(fā)中一個十分關鍵的過程,也是復雜FPGA系統(tǒng)開發(fā)必須進行的一步。時序問題是所有FPGA設計者繞不開的經常會出現(xiàn)的問題。如何能讓FPGA設計跑在更高的頻率,如何能更快地解決時序問題,對于FPGA設計至關重要。

好的時序路徑分析工具能夠幫助設計者更快地定位時序問題。Achronix ACE開發(fā)工具套件集成了功能強大的時序路徑分析工具,相信能夠有效地幫助FPGA設計者解決各種各樣的時序問題。

3. 時序報告的產生

FPGA的基本開發(fā)流程中,有多處可以進行時序分析的地方。ACE開發(fā)工具套件可以提供綜合以后、布局以后、布線以后等各個階段的時序分析。對于大多數(shù)設計者,只做布局布線以后的時序分析即可,因為帶了布局布線信息的時序分析最為精確,下面我們重點介紹布局布線以后的時序分析。

在利用ACE工具生成時序報告之前,我們先設置時序分析的相關參數(shù),ACE會根據(jù)設置的參數(shù)自動生成一個時序分析報告。如圖2所示,第一項設置關鍵路徑的打印條數(shù),默認是10條。第二項是設置每條關鍵路徑中最壞路徑的打印條數(shù),因為在每條關鍵路徑的兩個端點中可能包含多條路徑。

第三個單選框是打印未約束的時序路徑,這個信息可以幫助設計者查看時序約束是否覆蓋了設計中的所有路徑,報告中出現(xiàn)的未約束的路徑是不是用戶有意不想讓工具去分析的路徑。最后一個單選框是打印異步clear和preset信號到寄存器數(shù)據(jù)輸出的路徑。

圖2 時序報告相關參數(shù)

在ACE跑完布局布線時序分析以后,工具會根據(jù)參數(shù)設置產生相應的時序報告。時序報告有三種格式,html,csv和txt。三種文件格式不同,內容完全一樣。

除了可以自動生成時序報告以外,ACE開發(fā)工具套件也支持用戶用Tcl命令去生成指定路徑的時序報告。ACE開發(fā)工具套件支持的時序分析相關的Tcl命令如下:

check_setup:對設計做一些時序方面的檢查。

prepare_sta:做靜態(tài)時序分析的準備,進入時序分析模式。

report_checks:用于報告具體路徑的時序分析結果。

report_clock_properties:用于報告設計中用到的時鐘屬性。

reset_sta:用于退出時序分析模式。

通過上面五條Tcl命令可以靈活地對設計進行時序檢查和分析,具體使用可參見Achronix ACE User Guide UG070。

4. 時序報告詳解

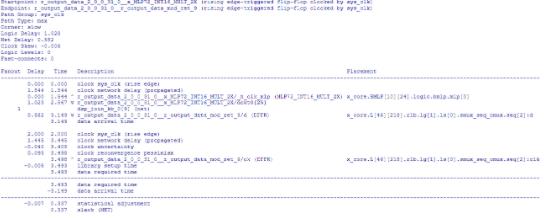

打開時序報告,文件開頭會有一個summary,如圖3所示。

圖3 時序報告Summary

在Summary里面會顯示在fast corner和slow corner下的setup和hold分析的關鍵路徑。同時在Summary的最下面,系統(tǒng)會報告每個時鐘的目標約束和實際能跑到的頻率。在Summary頁面中,關鍵路徑前有一個path id,這個path id同時又是一個超鏈接,用鼠標點擊后會自動跳轉到具體的時序路徑分析頁面,如圖4所示。

圖4 具體的時序路徑分析

圖5所示是一條分析setup的路徑。

圖5 setup timing路徑分析

數(shù)據(jù)從FF1發(fā)送出去被FF2捕獲,這里的Data Arrival Time等于時鐘launch edge到FF1的CLK端口需要的時間T_launch,加上源時鐘的路徑延遲,即CLK端到數(shù)據(jù)Q端需要的時間Tco,再加上數(shù)據(jù)的傳播延遲T_delay:

Data Arrival Time = T_launch + Tco + T_delay = 1.544 ns + 1.023 ns + 0.582 ns = 3.149 ns

Data Required Time等于CLK到達FF2所需要的時間T_capture,加上clock uncertainty,減去CLK路徑悲觀補償,再減去FF2的建立時間T_setup, 最后不要忘了加上一個時鐘周期:

Data Required Time = T_period + T_capture - T_clock_uncertainty + T_clk_reconvergence_pessimism – T_setup = 2.000 ns + 1.445 ns - 0.040 ns + 0.093 ns – 0.005 ns = 3.493 ns

這樣Setup slack就可以計算得出:

Setup Slack = Data Required Time - Data Arrival Time – Statistical Adjustment= 0.344 ns – 0.007ns(時序調整值) = 0.337ns

這里要提到時鐘公共路徑悲觀補償,因為時鐘到達FF1和FF2開頭一段路徑是重合的,在這段路徑里我們還是用最大時延差和最小時延差去進行時序分析的話是很悲觀的,所以需要用這個參數(shù)補償回來。

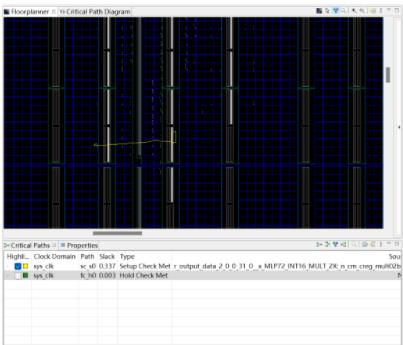

5. 圖形化界面輔助時序分析

在ACE的floorplanner界面中,可以通過圖形界面輔助進行時序分析,如圖6所示。

圖6 floorplanner界面的時序路徑分析

ACE工具會在Critical Paths頁面把時序報告中的時序路徑全部列出來,不滿足時序的路徑用紅色高亮顯示,滿足時序的路徑用綠色表示。用戶選中其中一條路徑,在floorplanner界面里這條路徑的走線就會自動高亮顯示出來,便于用戶看到這條路徑在FPGA內部具體的連接,以及源寄存器和目的寄存器在器件中的具體位置。

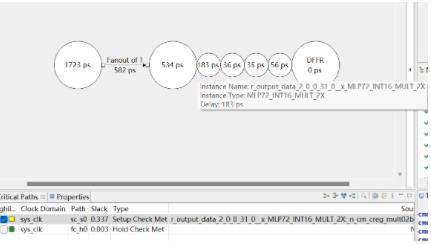

圖7 示意圖表示的時序路徑

在floorplanner頁面旁邊有個Diagram視圖,選中以后可以示意圖的方式顯示出這條路徑的具體延時數(shù)據(jù),鼠標停留在框圖上還會顯示更具體的信息。

綜上所述,在時序分析方面,ACE開發(fā)工具套件提供了完備的時序分析工具,從時序報告,到Tcl命令,再到圖形化的顯示,用戶可以很方便地利用工具進行時序分析,找到具體的問題所在,然后針對具體問題來優(yōu)化設計的整體性能。

后面我們會繼續(xù)深入了解ACE開發(fā)工具套件的各種特性,并且會用一些例子來說明如何更高效地利用這些特性為FPGA設計提供方便,敬請期待。 如需更多信息或者有任何疑問您可以通過Achronix公眾號里的聯(lián)系方式聯(lián)系我們,也可訪問Achronix公司官方網(wǎng)站。

參考文獻:

1.Achronix website www.achronix.com

2.Achronix ACE User Guide UG070