按照美光介紹,這是閃存行業(yè)首次跨入兩百層。與前幾代美光NAND相比,新產(chǎn)品具有業(yè)界最高的面密度,可以提供更高的容量和更高的能效,從而為從客戶端到云的數(shù)據(jù)密集型用例提供一流的支持。

“美光的 232 層 NAND是存儲(chǔ)創(chuàng)新的分水嶺,它首次證明了在生產(chǎn)中將 3D NAND 擴(kuò)展到超過 200 層的能力,”美光技術(shù)和產(chǎn)品執(zhí)行副總裁 Scott DeBoer 說。“這項(xiàng)突破性技術(shù)需要廣泛的創(chuàng)新,包括創(chuàng)建高縱橫比結(jié)構(gòu)的先進(jìn)工藝能力、新型材料的進(jìn)步以及基于我們市場領(lǐng)先的 176 層 NAND 技術(shù)的領(lǐng)先設(shè)計(jì)增強(qiáng)。”Scott DeBoer進(jìn)一步指出。

除了美光以外,三星和鎧俠也都在爭先恐后的涌向兩百層的閃存。此外,也有報(bào)道指出,國內(nèi)閃存企業(yè)長江存儲(chǔ)也將跨過一代,直接邁向232層存儲(chǔ)。由此可見,屬于閃存的新一輪爭霸戰(zhàn)正式開打。

美光“層數(shù)”的率先突破

在閃存堆疊的早期,韓國巨頭三星一直是領(lǐng)先者。但美光卻在后續(xù)的發(fā)展中迅速追上,并終于在176層閃存上實(shí)現(xiàn)了完美超越。而這次232層NAND Flash的量產(chǎn),更是將美光的領(lǐng)先優(yōu)勢進(jìn)一步擴(kuò)大。

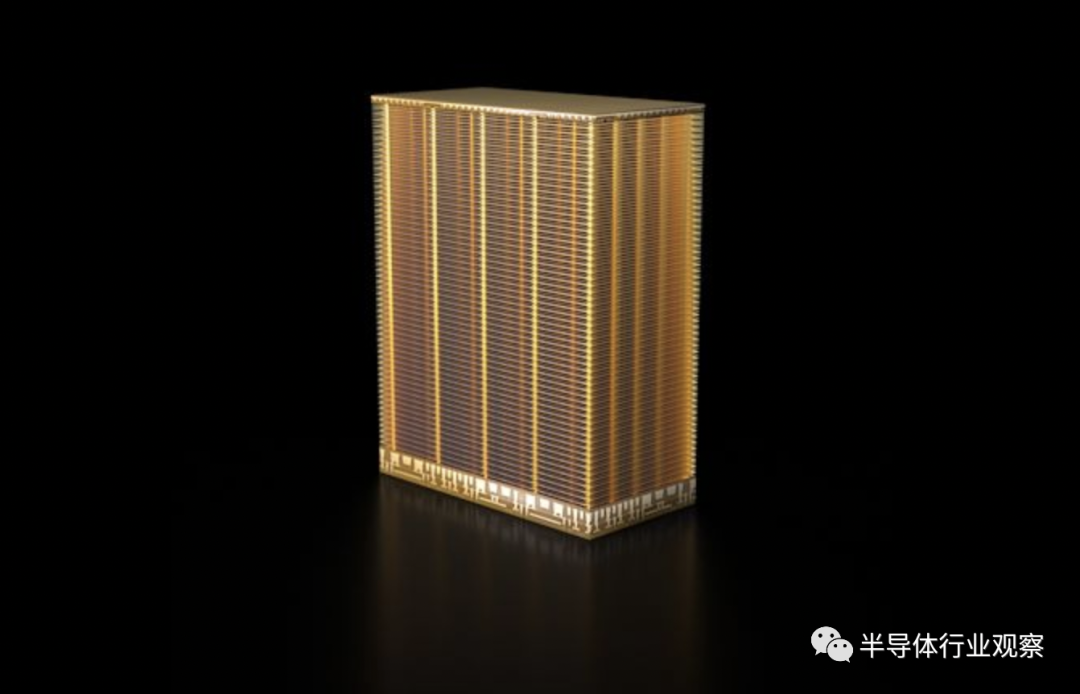

從原理上看,3D NAND Flash是通過在垂直堆棧中將多組單元相互層疊來制造的。閃存芯片中的層數(shù)越多,容量就越高。目前,所有制造商目前都在制造 100 層以上的芯片。美光則聲稱,其量產(chǎn)的232 層技術(shù)代表了世界上最先進(jìn)的NAND。

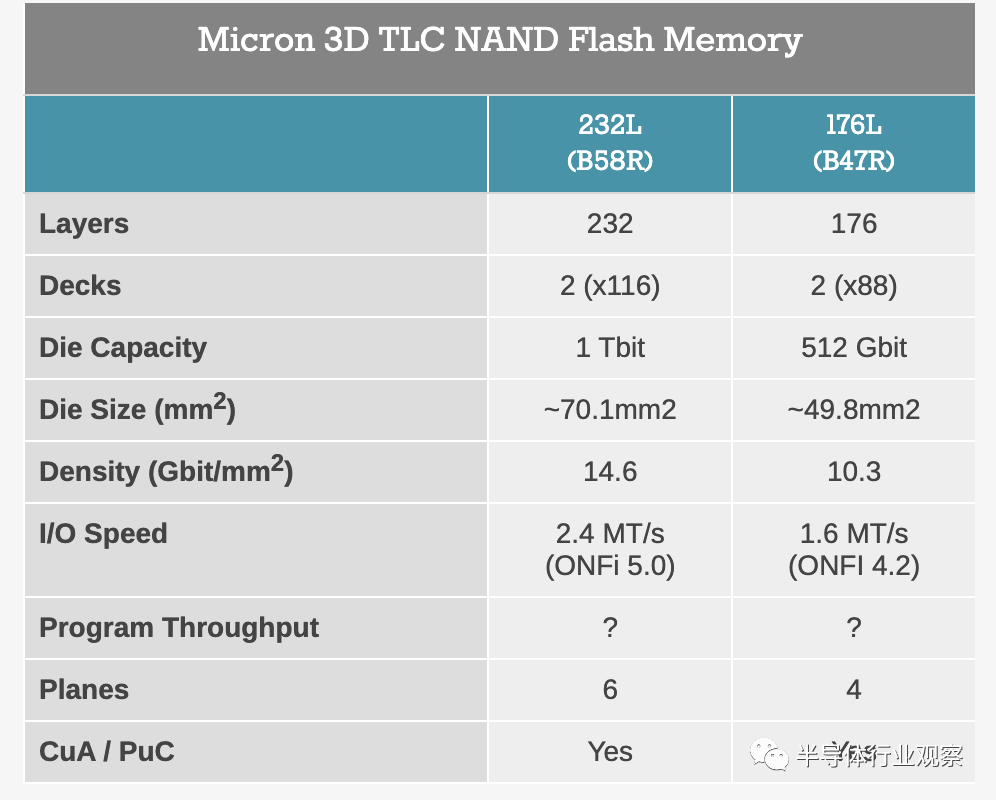

據(jù)美光介紹,公司新的232層閃存擁有業(yè)界最快的 NAND I/O 速度——每秒 2.4 GB (GB/s)。這一速度比美光 176 層節(jié)點(diǎn)上啟用的最快接口快50%。與上一代閃存相比,232 層 NAND 還提供高達(dá) 100% 的寫入帶寬和超過 75% 的讀取帶寬提升。

此外,232層NAND推出全球首款六平面(six-plane)TLC量產(chǎn)NAND。在所有 TLC 閃存的每個(gè)die中,其所具有的的平面(plane)是最多的,并且每個(gè)平面都具有獨(dú)立的讀取能力。美光的 232 層 NAND 還是首款支持 NV-LPDDR4 的生產(chǎn)產(chǎn)品,這是一種低壓接口,與之前的 I/O 接口相比,每比特傳輸節(jié)省 30% 以上。

能夠?qū)崿F(xiàn)這樣的速度提升,這當(dāng)然主要得益于美光在技術(shù)上的創(chuàng)新。

據(jù)anandtech報(bào)道,從技術(shù)角度來看,美光的232L NAND進(jìn)一步建立在美光那一代磨練出來的基本設(shè)計(jì)元素之上。因此,我們再次關(guān)注弦堆疊設(shè)計(jì)(string stacked design),美光使用一對(duì)116層decks,高于上一代的88層。反過來,116層decks也是值得注意的,因?yàn)檫@是美光第一次能夠生產(chǎn)超過100層的單一deck,這一壯舉以前僅限于三星能做到。這反過來又使美光能夠僅用兩層decks生產(chǎn)尖端的NAND,隨著公司推動(dòng)總層數(shù)超過300層的設(shè)計(jì),這可能在更長時(shí)間內(nèi)是不可能的。

美光的 NAND 平臺(tái)繼續(xù)使用其電荷陷阱(charge-trap)、CMOS under Array (CuA) 架構(gòu)構(gòu)建,該架構(gòu)將 NAND 的大部分邏輯置于 NAND 存儲(chǔ)單元之下。美光長期以來一直認(rèn)為這是他們在 NAND 密度方面獲得持續(xù)優(yōu)勢的原因,而這在他們的232層 NAND上再次展現(xiàn)。美光聲稱,他們已經(jīng)實(shí)現(xiàn)了 14.6 Gbit/mm?的密度,比他們的 176L NAND 密度高約 43%。而且,根據(jù) Micron 的說法,密度比競爭對(duì)手的 TLC 產(chǎn)品高 35% 到 100%。如此高的密度使美光最終能夠生產(chǎn)出他們的第一個(gè) 1Tbit TLC 裸片,從產(chǎn)品化的角度來看,這意味著美光現(xiàn)在還可以通過堆疊 16 個(gè) 232L 裸片來生產(chǎn) 2TB 芯片封裝。

與此同時(shí),美光也一直在研究其芯片封裝的尺寸,因此雖然更大的容量意味著他們的芯片尺寸逐代增加(根據(jù)美光的密度數(shù)據(jù),我們估計(jì)約為70.1mm 2),他們?nèi)匀粚⑿酒庋b縮小了 28%。因此,單芯片封裝從12mmx18mm(216mm2) 縮小到 11.5mmx13.5mm (~155mm2)。因此對(duì)于美光的下游客戶來說,美光 NAND 的更大容量和更小封裝的結(jié)合意味著設(shè)備制造商可以減少分配給 NAND 封裝的空間量,或者轉(zhuǎn)向另一個(gè)方向并嘗試塞進(jìn)更多的封裝進(jìn)入相似數(shù)量的空間。

此外,美光還在新產(chǎn)品的外圍邏輯上實(shí)現(xiàn)了最新一代的 ONFi。

ONFi 于 2021 年完成,現(xiàn)已推出第一批 NAND 產(chǎn)品,這種技術(shù)將控制器-NAND 傳輸速率提高了 50%,達(dá)到 2400MT/秒。ONFi 5.0 還引入了一種新的 NV-LPDDR4 信令方法,該方法具有相同的 2400MT/s 速率,但由于它基于 LPDDR 技術(shù),因此功耗更低。據(jù)美光公司稱,他們發(fā)現(xiàn)每比特能量傳輸節(jié)省了 30% 以上,從而線束降低了能耗。盡管與往常一樣進(jìn)行此類比較,但值得注意的是帶寬增益超過了節(jié)能(50%對(duì)30%)。

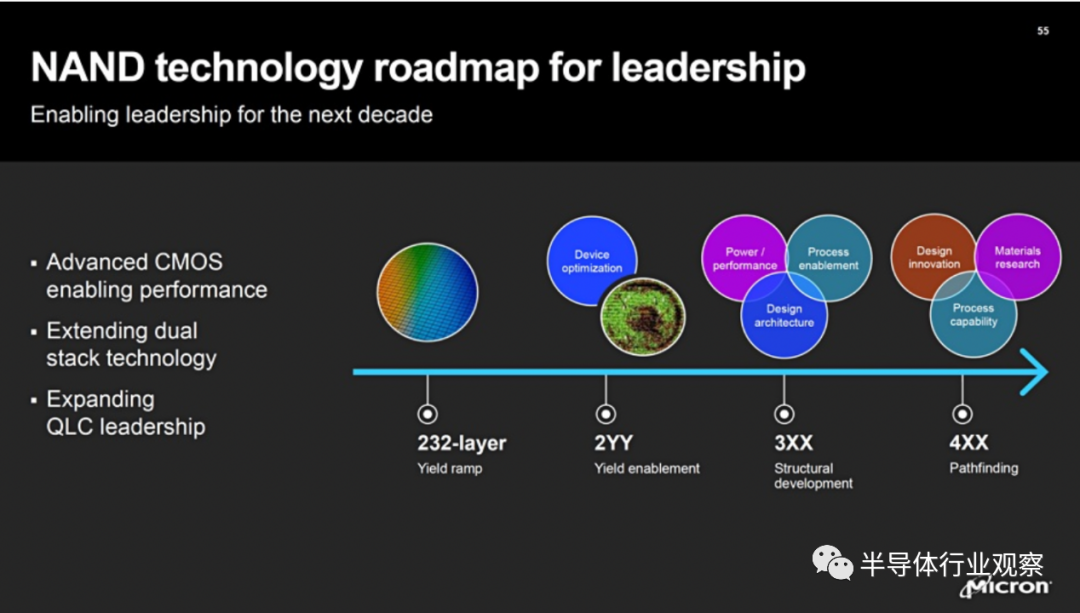

按照美光在投資者日的分享,未來會(huì)有五百層的NAND Flash規(guī)劃,但他們并沒有公布具體的時(shí)間表。

其他巨頭的亦步亦趨

在美光高調(diào)宣布232層閃存量產(chǎn)的同時(shí),其他存儲(chǔ)巨頭也在暗中發(fā)力。

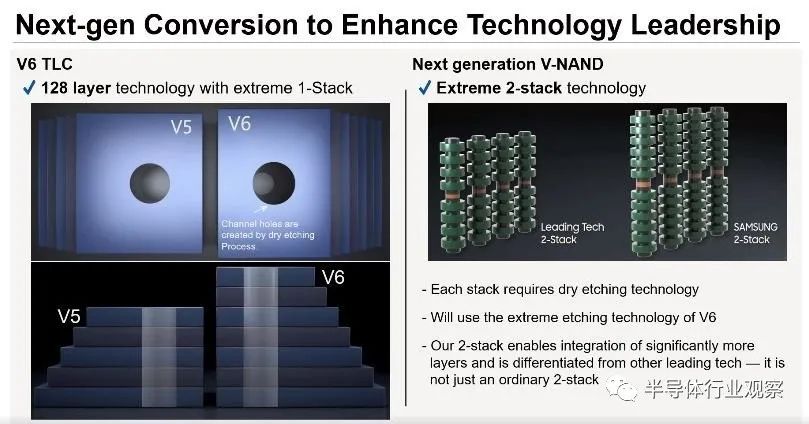

首先看三星方面,據(jù)韓媒businesskorea今年年初的報(bào)道,三星電子將在 2022 年底推出 200 層或更多層的第八代 NAND 閃存。業(yè)內(nèi)人士認(rèn)為,三星已經(jīng)通過“雙堆疊”的方式獲得了 256 層技術(shù)。報(bào)道進(jìn)一步指出,三星電子將成為第一家通過在 128 層單堆棧中增加 96 層來發(fā)布 224 層 NAND 閃存的芯片制造商。與 176 層芯片相比,224 層 NAND 閃存可以將生產(chǎn)力和數(shù)據(jù)傳輸速度提高 30%。而這背后的技術(shù)支柱則是來自三星V-NAND技術(shù)。

三星表示,自2013年推出以來,V-NAND一直是存儲(chǔ)業(yè)內(nèi)最成功的技術(shù)之一。它不僅僅是在越來越寬的小城市街道上一個(gè)接一個(gè)地延伸存儲(chǔ)芯片,而是使打開一扇相當(dāng)于摩天大樓存儲(chǔ)設(shè)計(jì)的大門,重塑了這個(gè)行業(yè)!三星進(jìn)一步指出,在從 100+ 層擴(kuò)展到 200+ 層的過程中,他們希望將其尖端的 V-NAND 摩天大樓彼此堆疊(由絕緣層隔開),這正是上面說的“128+96”的設(shè)計(jì)方式。按照三星預(yù)計(jì),這種所謂的串堆疊可能是推動(dòng) V-NAND 向前發(fā)展的最有效方式。當(dāng)然,額外的 3D 工藝改進(jìn)改進(jìn)也是需要的。

相關(guān)報(bào)道也指出,三星新技術(shù)的存儲(chǔ)密度較之上一代增加了40%左右。V-NAND V8閃存的單核容量也從之前的512Gbit翻倍到1Tbit,性能也更強(qiáng)。IO接口速率則直接從2Gbps提升至2.4Gbps,性能更兼容最新的PCIe 5.0標(biāo)準(zhǔn)。得益于更大的存儲(chǔ)容量。V-NAND V8閃存的厚度還是可以控制在合理的水平,封裝512GB容量不超過0.8。

在三星以外,另一家韓國巨頭SK Hynix也被報(bào)道也在追求200+層的閃存。相關(guān)報(bào)道指出,SK海力士有望在2023年推出其200+層的產(chǎn)品,但從他們官方,我們目前還沒有任何相關(guān)信息傳出。不過從公司更早之前的報(bào)道可以看到,4D NAND Flash技術(shù)也許會(huì)是SK海力士征服這個(gè)市場的“殺手锏”。

SK海力士表示,3D-NAND具有存儲(chǔ)容量隨著通過三維堆疊堆疊的層數(shù)的增加而增加的結(jié)構(gòu)。3D-NAND使用堆疊多層氧化物-氮化物的方法,在其上形成稱為“plug”的垂直深孔,然后在其中形成由氧化物-氮化物-氧化物制成的存儲(chǔ)器件。通過這種方法,可以通過少量的工藝同時(shí)形成大量的細(xì)胞。在 3D-NAND 中,電流流過位于圓柱形單元中心的多晶硅通道,并根據(jù)存儲(chǔ)在氮化硅中的電荷類型存儲(chǔ)編程和擦除信息。

在SK海力士看來,雖然3D-NAND 的核心技術(shù)是實(shí)現(xiàn)更高層數(shù)的三維堆疊,這在過去幾代了發(fā)展也不錯(cuò),但為了在3D-NAND之后進(jìn)一步最大化存儲(chǔ)容量,SK海力士開發(fā)了一種4D-NAND,可以使芯片尺寸更小。從技術(shù)上看,4D NAND就是在3D NAND單元下方形成外圍電路,以消除外圍電路占用的面積,從而最大限度地提高存儲(chǔ)容量并降低NAND閃存的成本。

在更早之前的2019年,SK海力士曾經(jīng)做過非常大膽的預(yù)測,那就是到2025年推出500 層堆疊產(chǎn)品,到2023年,更是將其4D NAND Flash堆疊提升到800+。但從目前看來,這實(shí)現(xiàn)起來似乎有點(diǎn)困難。

今年早些時(shí)候,西部數(shù)據(jù)與合作伙伴 Kioxia 也分享了他們的閃存路線圖。據(jù)介紹,該公司計(jì)劃很快推出其第 6 代 BiCS,它將在 TLC 和 QLC 配置中具有 162 層。他們同時(shí)還指出,公司即將推出的具有超過 200 層的 BiCS+ 內(nèi)存,該內(nèi)存將于 2024 年推出。與 BiCS6 相比,它的每個(gè)晶圓的位數(shù)將增加 55%,傳輸速度提高 60%,寫入速度提高 15%。

在去年九月份接受半導(dǎo)體行業(yè)觀察等記者采訪的時(shí)候,鎧俠方面曾經(jīng)表示,從162 層閃存開始,公司開始采用CMOS電路配置在存儲(chǔ)陣列下方的CUA結(jié)構(gòu)。據(jù)了解,這種設(shè)計(jì)的芯片厚度會(huì)大于CAN結(jié)構(gòu),但鎧俠表示,從單片晶圓中產(chǎn)出的芯片數(shù)量的增加可以彌補(bǔ)生產(chǎn)時(shí)間變長的影響。面向未來鎧俠后續(xù)還將引入CBA結(jié)構(gòu),即CMOS/存儲(chǔ)陣列鍵合,存儲(chǔ)陣列和周邊電路會(huì)分別生產(chǎn)。最終,將兩片晶圓鍵合在一起以形成一個(gè)存儲(chǔ)器芯片。除此以外,PLC和Twin BiCS也是鎧俠提升平面存儲(chǔ)密度的重要途徑。

所謂PLC,是penta level cell的簡稱,這是一種存儲(chǔ)5電位的設(shè)計(jì)。但鎧俠并不滿足于此,在之前的學(xué)術(shù)會(huì)議上,鎧俠還談到了存儲(chǔ)6電位的HLC(hexa level cell)和存儲(chǔ)8電位的OLC(octa level cell)。

至于Twin BiCS,則是鎧俠在2019年推出一個(gè)閃存新技術(shù)。據(jù)介紹,這是全球首個(gè)3D半圓形分裂浮柵極閃存單元。其使用的技術(shù)主要有半圓形、分裂、浮柵極,簡單來說就是將傳統(tǒng)的浮柵極分裂為兩個(gè)對(duì)稱的半圓形柵極,利用曲率效應(yīng)提高閃存P/E編程/擦除過程中的性能。

按照鎧俠介紹,他們計(jì)劃在未來十年內(nèi)構(gòu)建 500 層以上的 NAND Flash。

此外,有報(bào)道指出,國內(nèi)閃存新秀長江存儲(chǔ)的閃存層數(shù)也會(huì)直接從128層躍升到232層,并于今年年底量產(chǎn)。關(guān)于這個(gè)消息,并沒有辦法求證。我們僅將其列舉在此,以供大家參考。

NAND Flash何去何從?

從上文的介紹可以看到,自閃存進(jìn)入了3D時(shí)代,圍繞在層數(shù)的競爭正在愈演愈烈,甚至有專家預(yù)研,未來甚至可能會(huì)出現(xiàn)1000層的3D NAND Flash。但正如鎧俠在接受半導(dǎo)體行業(yè)觀察采訪的時(shí)候所說,這種高層數(shù)閃存的出現(xiàn),會(huì)增加閃存的制造時(shí)間和成本,這也是他們探索橫向發(fā)展3D 閃存的原因。

歐洲知名機(jī)構(gòu)imec也表示,為了維持 NAND-Flash 路線圖,一些主要廠商最近宣布將層數(shù)進(jìn)一步增加到 500 層或更多。按照這個(gè)趨勢線,這個(gè)數(shù)字將在十年結(jié)束前增加到 1000。他們也同意,暴增的層數(shù)會(huì)帶來更高的處理復(fù)雜性,也會(huì)挑戰(zhàn)沉積和蝕刻工藝,并導(dǎo)致應(yīng)力在層內(nèi)積聚。這也是類似三星這樣的NAND-Flash 制造商最近開始將層數(shù)分成兩(或更多)層,并將單獨(dú)處理的層堆疊在一起的原因。

但在他們看來,在更遙遠(yuǎn)的未來,預(yù)計(jì)我們將需要更多顛覆性的“后 NAND”創(chuàng)新來繼續(xù)實(shí)現(xiàn)閃存的密度縮放,從而為進(jìn)入Tbit/mm?時(shí)代做準(zhǔn)備。基于這樣的考慮, imec將GAA NAND-Flash 納入了路線圖。(具體參考我們之前的文章《NAND Flash何去何從,3D FetFET將擔(dān)當(dāng)重任》)

從很多的報(bào)道可以看到,各種新型存儲(chǔ)也將有望在未來扮演替代者的角色。不過短期看來,NAND Flash還將是存儲(chǔ)世界的重要組成,這是毫無疑問的。

更多信息可以來這里獲取==>>電子技術(shù)應(yīng)用-AET<<