1. 時(shí)鐘周期約束:時(shí)鐘周期約束,顧名思義,就是我們對(duì)時(shí)鐘的周期進(jìn)行約束,這個(gè)約束是我們用的最多的約束了,也是最重要的約束。

2. vivado中時(shí)鐘約束指令:

create_clock

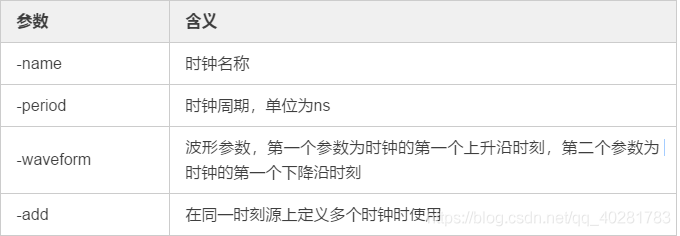

使用create_clock來創(chuàng)建時(shí)鐘周期約束,使用方法:

create_clock -name <name> -period <period> -waveform {<rise_time> <fall_time>} [get_ports <input_port>]

值得注意的是,這里的時(shí)鐘必須是主時(shí)鐘 primary clock。主時(shí)鐘通常有兩種情況:一種是由外部時(shí)鐘源提供,另外一種是告訴收發(fā)器的時(shí)鐘提供。

如何查看主時(shí)鐘?

綜合、布局布線之后

打開綜合設(shè)計(jì)或者布局布線設(shè)計(jì)

兩種方式查看主時(shí)鐘:第一種,report_clock_networks -name mainclock,可以直接查看主時(shí)鐘。第二種,check_timing -override_defaults no_clock,可以查看沒有被約束的主時(shí)鐘

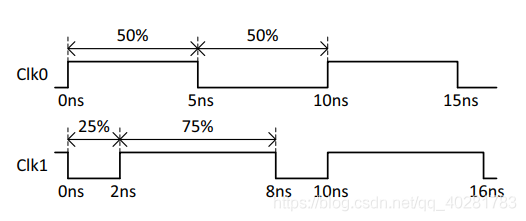

當(dāng)主時(shí)鐘之間的相位關(guān)系確定時(shí),則通過-waveform參數(shù)進(jìn)行約束

如上圖所示的兩個(gè)主時(shí)鐘,進(jìn)行如下約束:

create_clock -name clk0 -period 10.0 -waveform {0 5} [get_ports clk0]

create_clock -name clk1 -period 8.0 -waveform {2 8} [get_ports clk1]

數(shù)字單位默認(rèn)是ns。如果不寫waveform參數(shù),則默認(rèn)占空比是50%且第一個(gè)上升沿在0時(shí)刻。

一般來說,如果輸入時(shí)鐘是差分的,只需要對(duì)P端進(jìn)行約束即可。

create_generated_clock

約束在FPGA內(nèi)部產(chǎn)生的衍生時(shí)鐘,使用方法如下:

create_generated_clock -name <generated_clock_name> \

-source <master_clock_source_pin_or_port> \

-multiply_by <mult_factor> \

-divide_by <div_factor> \

-master_clock <master_clk> \

<pin_or_port>

因?yàn)槭茄苌鷷r(shí)鐘,所以有-source參數(shù),指明衍生時(shí)鐘從哪里來的,后面就是源時(shí)鐘名字,master clock,叫上一級(jí)時(shí)鐘,區(qū)別于primary clock。它可以是primary clock 也可以是其他衍生時(shí)鐘。

這個(gè)命令并不是設(shè)定周期和波形,而是描述時(shí)鐘電路如何對(duì)上級(jí)時(shí)鐘的轉(zhuǎn)換:

簡(jiǎn)單的頻率分頻、倍頻

頻率和分頻組合,獲得非整數(shù)的比例,通常由MMCM或PLL完成

相移或波形反相

占空比改變

set_clock_groups

使用方法:

set_clock_groups -asynchronous -group <clock_name_1> -group <clock_name_2>

set_clock_groups -physically_exclusive -group <clock_name_1> -group <clock_name_2>

第一種用法:來指定兩個(gè)主時(shí)鐘是異步關(guān)系,使用asynchronous。

create_clock -period 10 -name clk1 [get_ports clk1]

create_clock -period 8 -name clk2 [get_ports clk2]

set_clock_groups -asynchronous -group clk1 -group clk2

第二種用法:當(dāng)我們需要驗(yàn)證同一個(gè)時(shí)鐘端口在不同時(shí)鐘頻率下能否獲得時(shí)序收斂時(shí)使用。 比如有兩個(gè)異步主時(shí)鐘clk1和clk2,需要驗(yàn)證在clk2頻率為100MHz,clk1頻率分別為50MHz、100MHz和200MHz下的時(shí)序收斂情況,我們就可以這樣寫。

create_clock -name clk1A -period 20.0 [get_ports clk1]

create_clock -name clk1B -period 10.0 [get_ports clk1] -add

create_clock -name clk1C -period 5.0 [get_ports clk1] -add

create_clock -name clk2 -period 10.0 [get_ports clk2]

set_clock_groups -physically_exclusive -group clk1A -group clk1B -group clk1C

set_clock_groups -asynchronous -group "clk1A clk1B clk1C" -group clk2

第三種用法:當(dāng)我們使用BUFGMUX時(shí),會(huì)有兩個(gè)輸入時(shí)鐘,但只會(huì)有一個(gè)時(shí)鐘被使用。 比如MMCM輸入100MHz時(shí)鐘,兩個(gè)輸出分別為50MHz和200MHz,這兩個(gè)時(shí)鐘進(jìn)入了BUFGMUX。在這種情況下,我們需要設(shè)置的時(shí)序約束如下:

set_clock_groups -logically_exclusive \

-group [get_clocks -of [get_pins inst_mmcm/inst/mmcm_adv_inst/CLKOUT0]] \

-group [get_clocks -of [get_pins inst_mmcm/inst/mmcm_adv_inst/CLKOUT1]]

虛擬時(shí)鐘

虛擬時(shí)鐘通常用于設(shè)定對(duì)輸入和輸出的延遲約束,這個(gè)約束其實(shí)是屬于IO約束中的延遲約束。虛擬時(shí)鐘和前面講的延遲約束的使用場(chǎng)景不太相同。顧名思義,虛擬時(shí)鐘,就是沒有與之綁定的物理管腳。

虛擬時(shí)鐘主要用于以下三個(gè)場(chǎng)景:

外部IO的參考時(shí)鐘并不是設(shè)計(jì)中的時(shí)鐘

FPGA I/O路徑參考時(shí)鐘來源于內(nèi)部衍生時(shí)鐘,但與主時(shí)鐘的頻率關(guān)系并不是整數(shù)倍

針對(duì)I/O指定不同的jitter和latency

簡(jiǎn)而言之,之所以要?jiǎng)?chuàng)建虛擬時(shí)鐘,對(duì)于輸入來說,是因?yàn)檩斎氲紽PGA數(shù)據(jù)的捕獲時(shí)鐘是FPGA內(nèi)部產(chǎn)生的,與主時(shí)鐘頻率不同;或者PCB上有Clock Buffer導(dǎo)致時(shí)鐘延遲不同。對(duì)于輸出來說,下游器件只接收到FPGA發(fā)送過去的數(shù)據(jù),并沒有隨路時(shí)鐘,用自己內(nèi)部的時(shí)鐘去捕獲數(shù)據(jù)。

比如:如下圖所示,在FPGA的A和B端口分別有兩個(gè)輸入,其中捕獲A端口的時(shí)鐘是主時(shí)鐘,而捕獲B端口的時(shí)鐘是MMCM輸出的衍生時(shí)鐘,而且該衍生時(shí)鐘與主時(shí)鐘的頻率不是整數(shù)倍關(guān)系。

這種情況下時(shí)序約束如下:

create_clock -name sysclk -period 10 [get_ports clkin]

create_clock -name virclk -period 6.4

set_input_delay 2 -clock sysclk [get_ports A]

set_input_delay 2 -clock virclk [get_ports B]

可以看到,創(chuàng)建虛擬時(shí)鐘用的也是create_clock約束,但后面并沒有加get_ports參數(shù),因此被稱為虛擬時(shí)鐘。

再舉個(gè)輸出的例子,我們常用的UART和SPI,當(dāng)FPGA通過串口向下游器件發(fā)送數(shù)據(jù)時(shí),僅僅發(fā)過去了uart_tx這個(gè)數(shù)據(jù),下游器件通過自己內(nèi)部的時(shí)鐘去捕獲uart_tx上的數(shù)據(jù),這就需要通過虛擬時(shí)鐘來約束;而當(dāng)FPGA通過SPI向下游器件發(fā)送數(shù)據(jù)時(shí),會(huì)發(fā)送sclk/sda/csn三個(gè)信號(hào),其中sclk就是sda的隨路時(shí)鐘,下游器件通過sclk去捕獲sda的數(shù)據(jù),而不是用自己內(nèi)部的時(shí)鐘,這是就不需要虛擬時(shí)鐘,直接使用set_output_delay即可。

注意,虛擬時(shí)鐘必須在約束I/O延遲之前被定義。

max/min delay的約束平時(shí)用的相對(duì)少一些,因?yàn)樵诳绠惒綍r(shí)鐘域時(shí),我們往往會(huì)設(shè)置asynchronous或者false_path。對(duì)于異步時(shí)鐘,我們一般都會(huì)通過設(shè)計(jì)來保證時(shí)序能夠收斂,而不是通過時(shí)序約束來保證。

更多信息可以來這里獲取==>>電子技術(shù)應(yīng)用-AET<<