眾所周知,目前的FPGA EDA設(shè)計軟件大都運(yùn)行在x86的CPU上,而在很多領(lǐng)域,F(xiàn)PGA加速器又可以作為CPU的協(xié)處理器進(jìn)行計算加速。那么,F(xiàn)PGA本身是否可以用來對FPGA EDA,比如綜合、布局、布線的過程進(jìn)行加速呢?

前陣子在Reddit上看到了這個問題,引發(fā)了很多思考,后來查了些資料,還真有這么一本書在一定程度上系統(tǒng)解答了這個問題:

這本書研究了加速EDA算法的硬件平臺,如ASIC,F(xiàn)PGA和GPU。覆蓋范圍包括討論在何種條件下使用一個平臺優(yōu)于另一個平臺,例如,當(dāng)EDA問題具有高度的數(shù)據(jù)并行性時,GPU通常是首選平臺,而當(dāng)問題具有更多的控制因素時,F(xiàn)PGA可能是首選的。書里還給出了幾種EDA算法(故障仿真、故障表生成、SPICE模型卡評估、基于蒙特卡洛的統(tǒng)計靜態(tài)時序分析、布爾可滿足性)的加速結(jié)果,與這些算法的單核實(shí)現(xiàn)相比,可將運(yùn)行速度提高800倍以上。

該書作在如何最好地利用并行性來加速EDA算法方面給出了很有價值的參考。書中還提出了一種在一組約束條件下,從常規(guī)單處理器代碼中自動提取SIMD(單指令多數(shù)據(jù)流)并行性的方法。使用這種方法,這種單處理器代碼可以自動轉(zhuǎn)換為GPU代碼,實(shí)現(xiàn)顯著加速。這種方法特別有用,因?yàn)椴煌腉PU通常有不同的規(guī)格,在這種情況下手工生成GPU代碼變得不太現(xiàn)實(shí)。

該書提供了在加速特定EDA算法時使用ASIC、GPU還是FPGA的指導(dǎo)方針,并用在這些平臺上實(shí)現(xiàn)的一個具體示例(布爾可滿足性)驗(yàn)證了這些建議;通過介紹可供讀者使用的示例算法來幫助讀者確定如何最好地加速其EDA算法;討論一種自動生成GPU代碼的方法(給出一定約束下的常規(guī)單處理器代碼的條件下)。

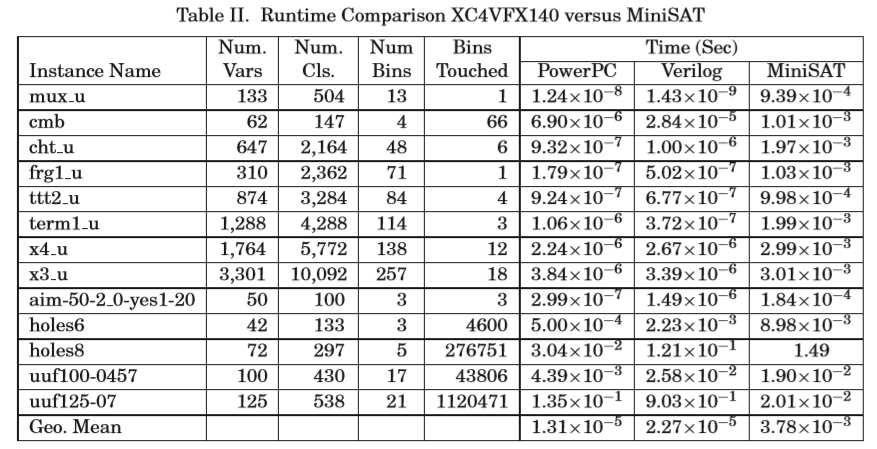

其中在該書的第五章唯一提到了FPGA平臺加速,也就是Accelerating Boolean Satisfiability on an FPGA章節(jié),提出了一種基于FPGA的SAT方法,在該方法中,Implication Graph的遍歷和Conflict Clause的生成是在硬件中并行執(zhí)行的,并且Clause Literal存儲在FPGA Slice單元里,為了解決復(fù)雜的SAT問題,啟發(fā)式地將clause劃分為許多“bin”,每個bin都可以fit進(jìn)FPGA中,最后得到結(jié)論,在使用了Virtex-4 (XC4VFX140) FPGA 之后,可以比MiniSAT(純軟件最好的算法)快90倍。但以上這些也僅僅涉及到綜合中的一部分,對于布局布線等其他EDA流程沒有深入研究,而且全書也沒有特別針對FPGA EDA算法,而是對幾個一般性EDA問題做了探討。

也許未來會有有人出一本專門講FPGA EDA加速平臺的書,再或許,有人會做一款專門用于FPGA EDA加速的SoC出來呢?:)

更多信息可以來這里獲取==>>電子技術(shù)應(yīng)用-AET<<