在硬件設(shè)計(jì)電路中,根據(jù)芯片功能復(fù)雜度,可編程芯片一般都需要不止一種供電電源來驅(qū)動(dòng)芯片內(nèi)部的不同功能塊,而FPGA具備邏輯可編程、編程靈活度更高、高集成度等特點(diǎn),供電電源種類繁多,需要硬件設(shè)計(jì)人員格外關(guān)注。

以AMD-Xilinx FPGA為例,不同的制程工藝下針對用戶的各種需求,會(huì)規(guī)劃有多個(gè)產(chǎn)品系列,其中集成不同功能、不同性能的功能模塊,因此我們按照功能模塊劃分來描述AMD-Xilinx FPGA需要的各種供電電源,簡單把電源種類分為PL供電電源、PS供電電源、集成功能塊供電電源。

每個(gè)系列FPGA產(chǎn)品的供電電源種類、名稱、電壓值、精度要求、去耦電容要求會(huì)有差異,具體設(shè)計(jì)時(shí)請工程師參照對應(yīng)芯片系列的手冊詳細(xì)查詢,本文中不對供電電源種類、名稱、電壓值、精度要求、去耦電容要求等做詳細(xì)解釋。

PL供電電源:VCCO、VCCAUX、VCCAUX_IO、VCCINT、VCCINT_IO、VCCBRAM、VBATT、VCCADC等。

PS供電電源:VCC_PSINTFP、VCC_PSINTLP、VCC_PSAUX、VCC_PSINTFP_DDR、VCC_PSPLL、VPS_MGTRAVCC、VPS_MGTRAVTT、VCCO_PSDDR、VCC_PSDDR_PLL、VCCO_PSIO、VCC_PSBATT等。

集成功能塊供電電源:

A. VCU供電電源:VCCINT_VCU;

B. XADC/System Monitor供電電源:VCCADC、VREFP、VREFN等;

C. GT Transceiver供電電源:VCCINT_GT、VMGTAVCC、VMGTAVTT、VMGTVCCAUX、VMGTAVTTRCAL等;

D. HBM供電電源:VCC_HBM、VCC_IO_HBM、VCCAUX_HBM等;

E. RF供電電源:VADC_AVCC、VADC_AVCCAUX、VDAC_AVCC、VDAC_AVCCAUX、VDAC_AVTT、VCCINT_AMS、VCCSDFEC等;

二、如何測試FPGA的供電電源

硬件工程師通常會(huì)在硬件設(shè)計(jì)初期對各路電源的功耗做預(yù)估并留有設(shè)計(jì)裕量,此時(shí)強(qiáng)烈推薦硬件設(shè)計(jì)工程師、邏輯設(shè)計(jì)工程師和嵌入式軟件設(shè)計(jì)工程師一起參與,使用XPE工具和已有的設(shè)計(jì)工程來進(jìn)行功耗預(yù)估;在硬件焊接完畢之后硬件設(shè)計(jì)工程師也會(huì)測試各路電源的電壓值、紋波等參數(shù)指標(biāo),都確認(rèn)OK后才會(huì)交給邏輯設(shè)計(jì)工程師去做外設(shè)、接口的測試。

針對支持客戶過程中遇到的幾個(gè)典型問題,作者根據(jù)自己的理解給出電源測試的幾點(diǎn)建議,歡迎硬件設(shè)計(jì)工程師們郵件來交流討論:

A. 測試電壓值時(shí)不建議使用萬用表,建議使用示波器的平均值功能,并調(diào)節(jié)合適的檔位;

B. 硬件設(shè)計(jì)中通常為了方便斷開電源,會(huì)在電源輸出進(jìn)FPGA之前添加磁珠或者電感,磁珠和電感會(huì)引入壓降,建議在磁珠和電感之后測試;如無磁珠和電感,建議測試點(diǎn)盡量靠近FPGA的電源PIN;

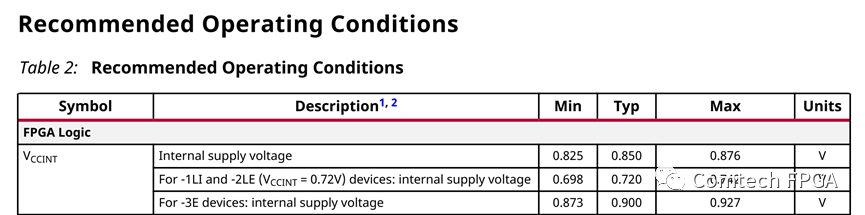

C. 每個(gè)系列的FPGA都有對應(yīng)的DC and AC SwTIching CharacterisTIcs手冊,里面會(huì)給出每種電源的電壓值要求范圍,實(shí)測電源電壓值在考慮上紋波的影響后不要超出手冊要求范圍,盡量不要接近下限;舉例說明:Kintex Ultrascale+器件的VCCINT電壓值在DS922上要求如下圖,若我們使用0.85V供電,在測試電壓值時(shí),考慮上紋波的影響,不要超出0.825V~0.876V的范圍,也盡量不要接近0.825V的下限電壓;

D. 紋波測試時(shí)選擇合適的檔位、使用交流耦合、打開20MHz帶寬抑制;

E. 帶負(fù)載測試,F(xiàn)PGA加載程序和不加載程序時(shí),功耗差異大,對于電源輸出電壓和紋波特性有影響,所以在測試電源時(shí)盡量使用完整的設(shè)計(jì)程序測試;在邏輯和軟件調(diào)試的后期也不要因?yàn)榘蹇▌偤附雍脮r(shí)硬件工程師測試過電源,而不敢懷疑電源問題;

三、電源影響FPGA功能和性能的幾個(gè)典型案例

電源影響功能和性能的幾個(gè)典型案例:

案例A:電源影響GT Transceiver性能

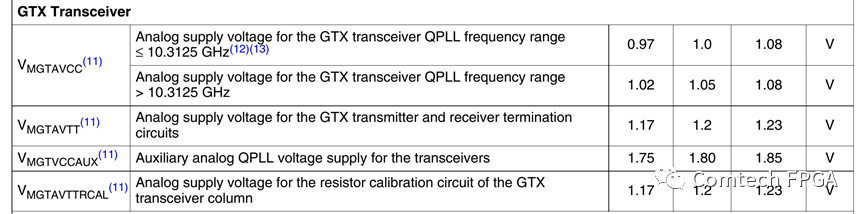

用戶使用K7 FPGA做HDMI2.0 TX設(shè)計(jì),輸出4K@60fps視頻點(diǎn)屏,屏幕上有噪點(diǎn),測試客戶板卡上GTX相關(guān)的MGTAVCC、MGTAVTT、MGTVCCAUX電源,發(fā)現(xiàn)MGTAVTT的紋波40+mV。

用戶在二次改板時(shí)修改了電源去耦電容,優(yōu)化了紋波,但是改板后在測試HDMI TX點(diǎn)屏?xí)r,4K@30fps點(diǎn)屏測試OK,4K@60fps點(diǎn)屏不成功。

使用IBERT測試,IBERT 6Gbps Near-end PCS環(huán)回測試OK,IBERT Near-end PMA環(huán)回測試鏈路不穩(wěn)定,會(huì)間歇性no link;而Ibert 3Gbps Near-end PCS環(huán)回和Near-end PMA環(huán)回均OK。

懷疑到MGTAVTT電源,經(jīng)過測試發(fā)現(xiàn),MGTAVTT在FPGA未加載程序時(shí)電壓值測試正常、紋波在30mV以內(nèi);MGTAVTT在FPGA加載程序后電源電壓從1.198V跌落到了1.18V,考慮上紋波影響后,可能會(huì)超出1.17V的下限,調(diào)高M(jìn)GTAVTT電源電壓值后,4K@60fps點(diǎn)屏測試工作正常。

案例B:電源影響GT Transceiver性能

用戶使用V5器件做XAUI設(shè)計(jì),在實(shí)驗(yàn)室環(huán)境下測試所有功能正常,最終用戶的板卡插到機(jī)房的標(biāo)準(zhǔn)機(jī)柜中測試時(shí)發(fā)現(xiàn)有數(shù)據(jù)丟幀現(xiàn)象,測試MGTAVCC、MGTAVTT、MGTVCCAUX電源的電壓值和紋波,均符合手冊要求的范圍。

經(jīng)過和用戶一起分析,認(rèn)為機(jī)房中電磁干擾可能比較大,最終把MGTAVTT調(diào)整到比標(biāo)準(zhǔn)值1.20V略大,提升Transceiver PMA抗干擾能力,問題解決。

案例C:電源影響Memory初始化完成

用戶使用A7 FPGA,外接DDR3 Memory,在樣機(jī)研制階段沒有發(fā)現(xiàn)問題,進(jìn)入批產(chǎn)階段后,在生產(chǎn)的幾千塊板卡中有幾百塊不能正常工作,通過JTAG調(diào)試發(fā)現(xiàn)DDR3的init_calib_complete為0,初始化無法完成。

換用MIG的example design測試,發(fā)現(xiàn)在有故障的板卡上使用example design也無法初始化完成,通常在MIG example design測試不過的時(shí)候我們考慮電源、時(shí)鐘、PCB的影響,由于客戶批量生產(chǎn)中大部分板卡整個(gè)程序測試OK,因此我們排除掉PCB的影響。

在測試電源時(shí),我們發(fā)現(xiàn)用戶硬件設(shè)計(jì)時(shí)在接DDR3的BANK VCCO供電的1.5V實(shí)測值為1.48V,經(jīng)過一個(gè)磁珠后電壓值為1.46V,考慮上紋波的影響,到達(dá)FPGA VCCO PIN的電壓可能低至1.44V,我們拆掉磁珠直接短接兩個(gè)焊點(diǎn)后,DDR3 example design測試OK,用戶的完整應(yīng)用測試也OK。

案例D:電源影響VCU工作

用戶使用ZU4EV來做視頻編解碼設(shè)計(jì),編碼端使用VCU做4路1080P視頻的壓縮,測試中發(fā)現(xiàn)當(dāng)使能2路1080P視頻壓縮時(shí)編碼板工作正常,當(dāng)使用軟件命令啟動(dòng)第3路視頻的壓縮時(shí),VCU編碼功能掛死;而解碼板只做2路1080P視頻的解壓縮,所以解碼板的VCU未發(fā)現(xiàn)問題。

我們在軟件側(cè)嘗試做工作,檢查VCU的IP配置,嘗試在VCU編碼掛死時(shí)重新加載VCU的驅(qū)動(dòng),使用不同的Vivado版本、Petalinux版本、驅(qū)動(dòng)版本等,測試現(xiàn)象一致。

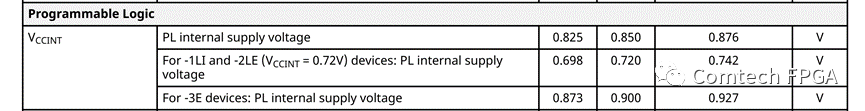

檢查用戶的原理圖,發(fā)現(xiàn)VCCINT_VCU和VCC_INT是同一路電源供電,前端電源芯片輸出0.85V電壓,查證后得知,早期的Xilinx手冊上寫VCCINT_VCU可以0.85V供電,在現(xiàn)在的手冊上VCCINT_VCU要求0.9V供電。

![]()

測試中發(fā)現(xiàn),VCCINT經(jīng)過一個(gè)磁珠后給VCCINT_VCU,在VCU啟動(dòng)到編碼功能時(shí),磁珠的壓降變化,每啟動(dòng)一路1080P視頻編碼,整板功耗增加約1W;在啟動(dòng)到第3路1080P編碼時(shí),磁珠的壓降大至0.03V,VCCINT_VCU跌落至0.82V,VCU不能正常工作。

最終我們?nèi)サ舸胖椋裋CCINT和VCCINT_VCU的電壓調(diào)高至0.87V,用戶完整設(shè)計(jì)工作正常。

更多信息可以來這里獲取==>>電子技術(shù)應(yīng)用-AET<<