比特流是一個(gè)常用詞匯,用于描述包含FPGA完整內(nèi)部配置狀態(tài)的文件,包括布線、邏輯資源和IO設(shè)置。大多數(shù)現(xiàn)代FPGA都是基于SRAM的,包括Xilinx Spartan 和Virtex 系列。在FPGA上電或隨后的FPGA重新配置期間,比特流從外部諸如閃存這樣的非易失性存儲(chǔ)器中讀取,通過FPGA配置控制器的處理,加載到內(nèi)部的配置SRAM中。

在有些情況下,設(shè)計(jì)者需要很好地了解FPGA比特流的內(nèi)部結(jié)構(gòu)。例如,使用FPGA物理實(shí)現(xiàn)工具的參數(shù)不能訪問自定義的低級(jí)比特流、實(shí)現(xiàn)復(fù)雜的配置回溯方案、通過內(nèi)部配置端口(ICAP)產(chǎn)生用于FPGA重新配置的短命令序列、讀配置狀態(tài)等。

比特流格式

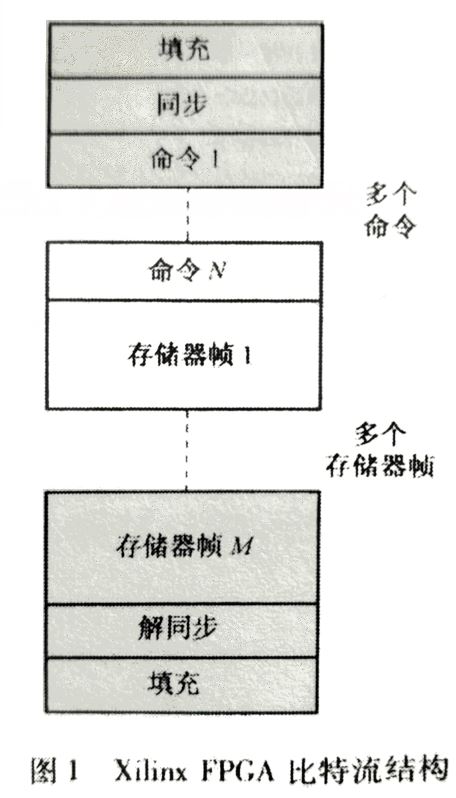

Xilinx FPGA的比特流結(jié)構(gòu)如圖1所示。

比特流包括以下組成部分:填充、同步字、用于訪問配置寄存器的命令、存儲(chǔ)器幀和解同步字。

填充

填充的數(shù)據(jù)是全0或全1序列,被FPGA配置控制器忽略。填充數(shù)據(jù)用于非易失性存儲(chǔ)器中分離比特流。一般使用全 1填充較為方便,因?yàn)閳?zhí)行擦除后閃存的狀態(tài)也是全1。

同步字

同步字是一個(gè)特殊值(0xAA995566), 通知FPGA配置控制器處理后續(xù)的比特流數(shù)據(jù)。

解同步字

解同步字通知FPGA配置控制器比特流的末端位置。解同步字之后,所有的比特流數(shù)據(jù)被忽略,直到遇到下一個(gè)同步字。

命令

命令用于讀和寫FPGA配置控制器寄存器。每個(gè)比特流中出現(xiàn)的一些命令, 有的是ID-CODE,用于標(biāo)識(shí)比特流屬于哪個(gè)FPGA器件。幀地址寄存器(FAR)、幀數(shù)據(jù)寄存器(FDRI)和無操作( NOOP)將被忽略。

存儲(chǔ)器幀

存儲(chǔ)器幀是配置Xilinx FPGA的比特流基本單元。幀的大小與具體的PPGA系列有關(guān),系列不同,幀的大小也不同。Virtex-6 器件的幀有2592位。每個(gè)Virtex-6 器件具有的幀數(shù)不同,從最小7491(對(duì)于LX7ST)到最大5ss 548(對(duì)于LX550T)。幀用于多個(gè)邏輯片、I0、

BRAM及其他FPGA的配置。每幀都有一個(gè)地址,對(duì)應(yīng)于FPGA配置空間的位置。比特流使用FAR和FDRI命令序列來配置幀。

Virtex-6 FPGA配置用戶指南包含足夠的關(guān)于比特流和訪向FPGA配置控制器寄存器命令的文檔。然而,關(guān)于存儲(chǔ)器幀的詳細(xì)文檔不僅對(duì)于Xilinx FPGA無法獲得,而且對(duì)于其他供應(yīng)商的FPGA也是如此。

Xilinx的BITGEN實(shí)用程序

BITGEN是Xilinx的實(shí)用程序,利用本地電路描述( NCD)格式的布局布線后文件,創(chuàng)建用于FPGA配置的比特流。BITGEN 是一個(gè)高度可配置的工具,具有100多個(gè)命令行選項(xiàng)(在命令行工具用戶指南2中描述)。有些選項(xiàng)用于確定比特流輸出格式、啟用壓縮處理減少比特流大小、提高FPGA配置速度、使用CRC來確保數(shù)據(jù)完整性、對(duì)比特流加密等。

示例

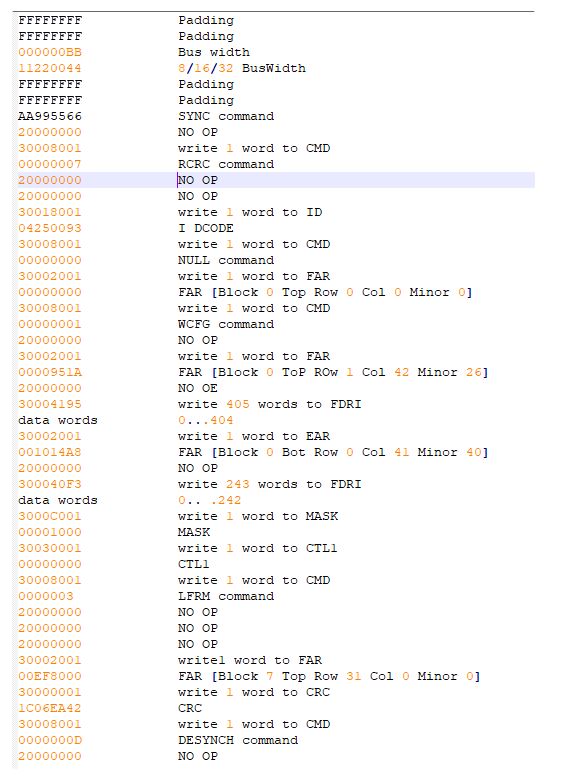

以下示例用于根據(jù)差異部分配置的短比特流,通過腳本語言描述比特流命令。腳本采用Perl編寫,在配套的網(wǎng)站上提供。

仔細(xì)觀察比特流,能區(qū)分出同步和解同步命令、屬于Virtex.6 LX240T PPGA的IDCODE,以及兩個(gè)405個(gè)和243個(gè)字的幀。

更多信息可以來這里獲取==>>電子技術(shù)應(yīng)用-AET<<