1. 引言

戈登·摩爾(Gordon Moore)在他提出了“摩爾定律”[1]的開(kāi)創(chuàng)性論文中預(yù)測(cè)了“清算日”的到來(lái)——“用分別封裝并相互連接的多個(gè)小功能系統(tǒng)構(gòu)建大型系統(tǒng)可能是更經(jīng)濟(jì)的。”今天,我們已經(jīng)度過(guò)了那個(gè)拐點(diǎn)。多個(gè)裸芯的封裝集成已廣泛應(yīng)用于半導(dǎo)體行業(yè),包括主流的中央處理單元(CPU)和通用圖形處理器單元(GP-GPU)[2]。

封裝內(nèi)小芯片的發(fā)展受多方面因素驅(qū)動(dòng)。克服光刻機(jī)最大尺寸的限制的,保障性能/功能的前提下生產(chǎn)更大規(guī)模的裸芯,是各大公司發(fā)展出其特有方案的主要原因。

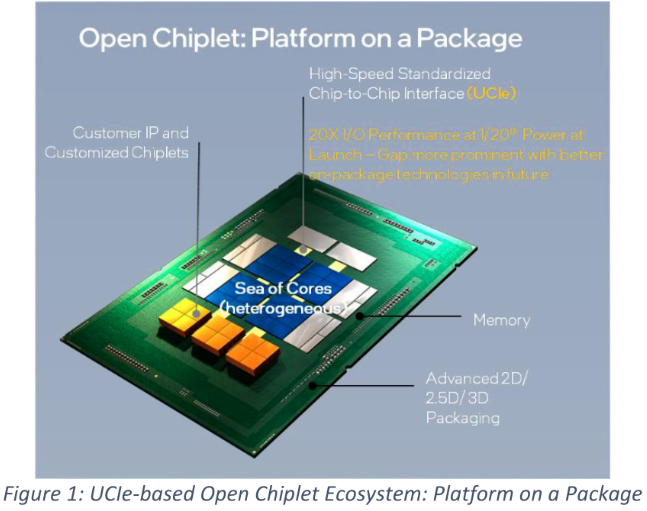

降低總體組合成本,同時(shí)擁有上市時(shí)間優(yōu)勢(shì),這將是發(fā)展Chiplet的一個(gè)令人信服的驅(qū)動(dòng)因素。例如,F(xiàn)igure 1[3]所示的計(jì)算核心可以在采用先進(jìn)工藝實(shí)現(xiàn),以提供領(lǐng)先的電源效率,而包含內(nèi)存和輸入/輸出(I/O)控制器功能的結(jié)構(gòu)可以復(fù)用已經(jīng)成熟工藝中的設(shè)計(jì)。這樣的分割方式也可以使裸芯更小,從而獲得更高的良率。此外,這種方法有助于降低IP移植成本,對(duì)于先進(jìn)工藝[3],IP移植成本顯著增加。

Chiplet的另一個(gè)價(jià)值是可以提供定制的解決方案。例如,人們可以根據(jù)特定產(chǎn)品領(lǐng)域的需求,選擇不同數(shù)量的運(yùn)算、內(nèi)存和I/O以及加速器芯片。人們不再需要為不同的細(xì)分市場(chǎng)做不同的裸芯設(shè)計(jì),降低了設(shè)計(jì),驗(yàn)證和產(chǎn)品成本。

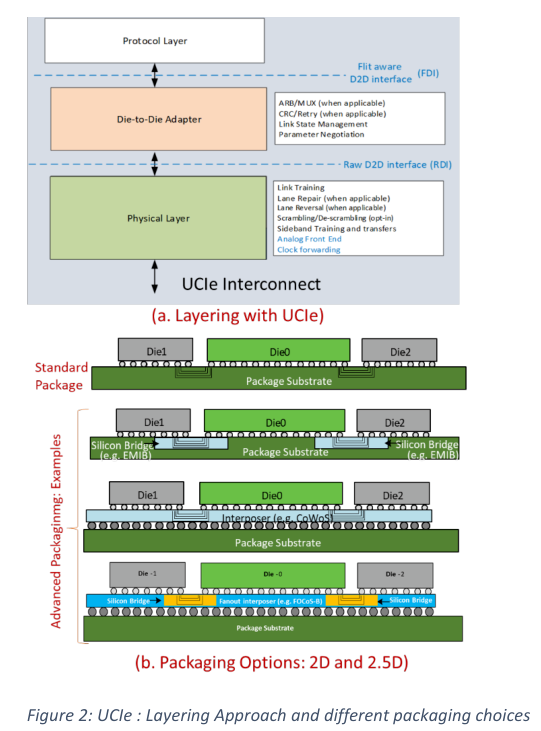

UCIe[4]是一種開(kāi)放的行業(yè)標(biāo)準(zhǔn)互連,為異構(gòu)芯片間提供了高帶寬、低延遲、高電源效率和高性?xún)r(jià)比的封裝內(nèi)連接,以滿(mǎn)足整個(gè)計(jì)算系統(tǒng)的需求。UCIe 1.0規(guī)范[4]包含了堆棧的所有層級(jí)(圖2a),是我們所知的唯一具有明確規(guī)范機(jī)制的完整規(guī)范,該規(guī)范面向使用PCI-Express(PCIe)[5、6]和Compute Express Link (CXL)[7]協(xié)議和軟件基礎(chǔ)設(shè)施的組件的異構(gòu)集成,以確保互操作性。這使得設(shè)計(jì)者能夠使用廣泛的封裝技術(shù)對(duì)不同來(lái)源的芯片進(jìn)行封裝,包括不同的工廠。UCIe是先前工作的演進(jìn),它已經(jīng)作為專(zhuān)有的多裸芯結(jié)構(gòu)接口(MDFI),在Intel Sapphire Rapids CPU中實(shí)現(xiàn)[2]。本文所描述的關(guān)鍵指標(biāo)、特性和仿真方法已在Sapphire Rapids silicon[2]中得到驗(yàn)證。

本文在第二節(jié)中深入研究了UCIe的要求和使用模式。在第三節(jié)中描述了我們提出的方法,該方法在UCIe規(guī)范[4]中得到了廣泛采用。我們將在第四節(jié)介紹我們的成果,并在第五節(jié)得出結(jié)論。

2. UCIe1.0規(guī)范針對(duì)的使用模式、封裝技術(shù)和性能指標(biāo)

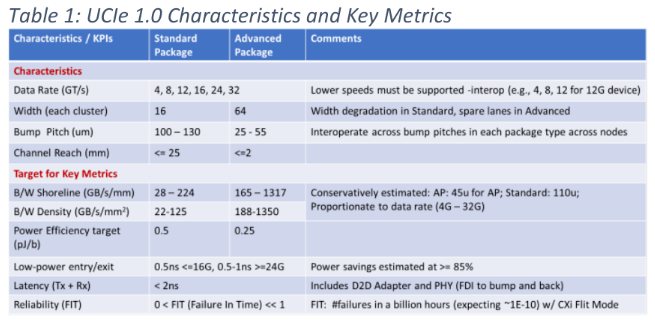

UCIe 1.0支持兩種類(lèi)型的封裝,如圖2b所示。標(biāo)準(zhǔn)封裝(2D)被稱(chēng)為UCIe-S,用于實(shí)現(xiàn)高性?xún)r(jià)比。先進(jìn)的封裝(UCIe-A)用于提高電源效率。有多種商業(yè)上可用的選擇,可以部署UCIe-S和UCIe-A,其中一些如圖所示。UCIe 1.0規(guī)范包含了這些類(lèi)別中的所有類(lèi)型的打包選擇。表1[3]總結(jié)了UCIe 1.0規(guī)范的業(yè)界領(lǐng)先性能指標(biāo)。

3. UCIe建議的方法

我們的方法是一個(gè)規(guī)范的分層標(biāo)準(zhǔn),包括協(xié)議層、適配器和物理層(PHY)。我們將首先簡(jiǎn)要說(shuō)明這些層,然后重點(diǎn)介紹獨(dú)特的電路架構(gòu)和封裝通道設(shè)計(jì)特性,以實(shí)現(xiàn)目標(biāo)性能、靈活性和互操作性。

A.分層

PHY負(fù)責(zé)電信號(hào)、時(shí)鐘、鏈路訓(xùn)練、邊帶等、電路架構(gòu)和封裝互連通道。

Die-to-die適配器為Chiplet提供鏈路狀態(tài)管理和參數(shù)協(xié)商。當(dāng)啟用時(shí),它通過(guò)其循環(huán)冗余校驗(yàn)(CRC)和鏈路級(jí)重傳機(jī)制保證數(shù)據(jù)的可靠傳遞。它的底層仲裁機(jī)制支持多種協(xié)議。256字節(jié)(或68字節(jié))流量控制單元(FLIT)支持底層的可靠傳輸機(jī)制。

我們將PCIe和CXL協(xié)議映射到UCIe中,因?yàn)檫@些協(xié)議被廣泛部署在所有計(jì)算機(jī)系統(tǒng)的板級(jí)上。這樣做是為了利用現(xiàn)有的生態(tài)系統(tǒng),確保無(wú)縫互操作性,使板級(jí)組件可以被打包到一個(gè)封裝中。通過(guò)PCIe和CXL,當(dāng)今平臺(tái)上部署的片上系統(tǒng)(SoC)、鏈路管理和安全解決方案可以無(wú)縫遷移到UCIe。

我們?yōu)閁CIe這樣die-to-die互連的使用模式的解決方案是全面的:使用直接內(nèi)存訪問(wèn)的數(shù)據(jù)傳輸,軟件發(fā)現(xiàn),錯(cuò)誤處理等,通過(guò)PCIe/CXL.io解決;內(nèi)存使用情況通過(guò)CXL.Mem處理;而加速器等應(yīng)用程序的緩存需求是通過(guò)CXL.cache解決的。我們還定義了一個(gè)“流協(xié)議”,它可以用來(lái)映射任何其他協(xié)議,如專(zhuān)有的對(duì)稱(chēng)緩存一致性協(xié)議(例如,超路徑互連)。我們的方法還使UCIe聯(lián)盟能夠創(chuàng)新出新的協(xié)議,以覆蓋新的使用模式或改進(jìn)現(xiàn)有的協(xié)議。

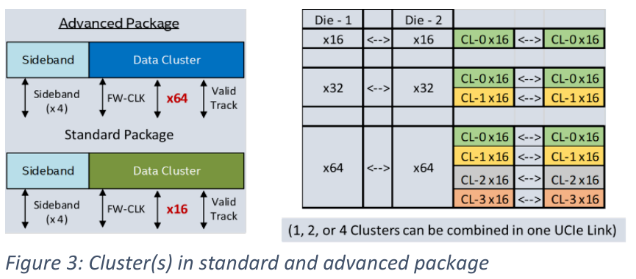

我們支持不同的數(shù)據(jù)速率、寬度、凸距和通道范圍,以確保最廣泛的互操作性,如表1所示。互連的構(gòu)建單元是一個(gè)集群(cluster),其中包括N個(gè)單端、單向、全雙工數(shù)據(jù)通道(標(biāo)準(zhǔn)封裝的N = 16,先進(jìn)封裝的N = 64),一個(gè)用于valid的單端的通道,一個(gè)用于tracking通道,每個(gè)方向有一個(gè)差分轉(zhuǎn)發(fā)時(shí)鐘,每個(gè)方向有兩個(gè)用于邊帶的單端通道(一個(gè)用于800Mhz時(shí)鐘,一個(gè)用于數(shù)據(jù))。邊帶接口用于狀態(tài)交換,方便數(shù)據(jù)集群中鏈路的訓(xùn)練,即使在在鏈路未被訓(xùn)練的情況下,也有寄存器訪問(wèn)機(jī)制,用于診斷。先進(jìn)封裝支持使用備用通道來(lái)處理故障通道(包括時(shí)鐘、valid、邊帶等),而標(biāo)準(zhǔn)封裝支持寬度降級(jí)來(lái)處理故障。可以聚合多個(gè)集群來(lái)為每個(gè)鏈接提供更高的性能,如圖3所示。

B.物理層架構(gòu)

我們?cè)跇?gòu)建UCIe PHY層時(shí)已經(jīng)將集成設(shè)備制造商(IDM)和外包半導(dǎo)體組裝和測(cè)試(OSAT)可移植性考慮在內(nèi)。大多數(shù)電路組件可以用數(shù)字類(lèi)型的電路構(gòu)建,如推挽發(fā)射機(jī)(TX)、數(shù)字延遲鎖定環(huán)(DLL)和相位插補(bǔ)器(PI)、基于變頻器的前端接收器(RX)、用于采樣的動(dòng)態(tài)鎖存比較器和基于變頻器的時(shí)鐘分布。一些組件可以與更高性能的標(biāo)準(zhǔn)模擬模塊互換,如用于RX模擬前端(AFE)的連續(xù)時(shí)間放大器、片上終端、電感器、片上穩(wěn)壓器等,它們可移植到任何現(xiàn)代IDM節(jié)點(diǎn)。

我們?yōu)閁CIe-A和UCIe-S提出了相同的時(shí)鐘和信號(hào)方案。這些方案包括源時(shí)鐘同步和匹配的時(shí)鐘/數(shù)據(jù)延遲路徑,以實(shí)現(xiàn)在噪聲較大的供電環(huán)境中仍有穩(wěn)定的性能,同時(shí)將不歸零(NRZ)編碼信號(hào)作為下一節(jié)將討論的通道規(guī)格的最佳能耗/性能。TX輸出擺幅被規(guī)定為400 mV-850 mV的寬工作范圍,以允許實(shí)現(xiàn)復(fù)雜性與通道能耗/性能優(yōu)化。RX必須滿(mǎn)足輸入在16GT/S時(shí)眼圖大小(高*寬)40mV*47ps以及在32GT/s是眼圖大小為40 mV*20ps的標(biāo)準(zhǔn)。在早期訓(xùn)練階段的參數(shù)協(xié)商將把擺幅等級(jí)傳達(dá)給接收的裸芯,此外RX觸發(fā)點(diǎn)以及其他參數(shù)校準(zhǔn)也可以在這個(gè)時(shí)候完成。

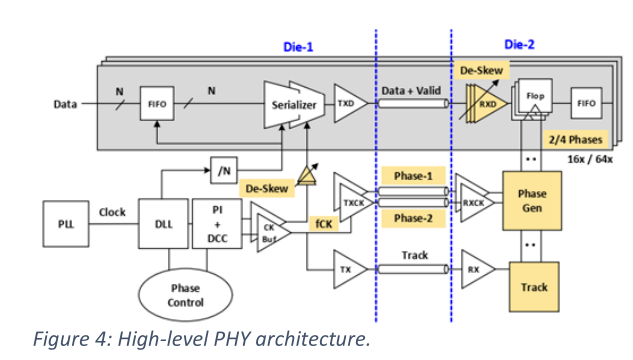

經(jīng)過(guò)訓(xùn)練后,鏈路的時(shí)鐘和數(shù)據(jù)路徑間將有大約0.5單位間隔(UI)。這個(gè)0.5UI的目標(biāo)使鏈路有效地成為一個(gè)“匹配的架構(gòu)”,對(duì)最大限度地減少確定性抖動(dòng)(DJ)對(duì)鏈路定時(shí)性能的影響至關(guān)重要。在降低供電電壓,時(shí)鐘和數(shù)據(jù)路徑之間的0.5 UI延遲增量為電源下降的幅度乘以電路路徑的α系數(shù)(即延遲變化相對(duì)于VCC變化的百分比)。通常在低壓供電時(shí),時(shí)鐘和數(shù)據(jù)路徑之間的延遲增量越大,兩條路徑之間的偏移就越大。這種額外的偏移會(huì)直接導(dǎo)致鏈接性能下降。建議的0.5 UI架構(gòu)允許在16 GT/s的電壓下提供40-50 mV的電源噪聲。相比之下,1.5或2.5的UI目標(biāo)將需要更嚴(yán)格的電源噪聲規(guī)格或高帶寬跟蹤機(jī)制,這可能會(huì)帶來(lái)大量的能耗。RX端的匹配架構(gòu)要求通過(guò)數(shù)據(jù)和時(shí)鐘路徑的延遲到采樣觸發(fā)器之間的間隔不超過(guò)0.1個(gè)UI。將由兩個(gè)具有控制端的CMOS緩沖器組成的糾偏緩沖器(De-Skew)添加到每個(gè)數(shù)據(jù)路徑通道,用于通道間的糾偏校準(zhǔn)。如果考慮到較高的電源噪聲容限,整體功率和噪聲影響可以忽略不計(jì)。圖4展示了我們提議的PHY體系結(jié)構(gòu)的概述。

來(lái)自RDI接口的線(xiàn)路(圖2a)經(jīng)過(guò)跨時(shí)鐘域FIFO,來(lái)重新計(jì)時(shí)協(xié)議鎖相環(huán)和物理層鎖相環(huán)時(shí)鐘域之間的信號(hào)。FIFO被轉(zhuǎn)換為串行輸出,并通過(guò)一個(gè)阻抗補(bǔ)償?shù)腡X驅(qū)動(dòng)程序傳輸。時(shí)鐘路徑包括一個(gè)延遲鎖相環(huán)(DLL),用于為精密的偏移調(diào)節(jié)器(PI)和占空比校正器(DCC)生成必要的參考值(正交或相同)。在接收機(jī)裸芯上,通過(guò)在數(shù)據(jù)RX AFE和采樣觸發(fā)器之間添加一些延遲(通常是2個(gè)反向器)來(lái)匹配發(fā)送到采樣器觸發(fā)器的數(shù)據(jù)和時(shí)鐘路徑,以匹配時(shí)鐘RX AFE+相位生成/時(shí)鐘分配帶來(lái)的延遲。

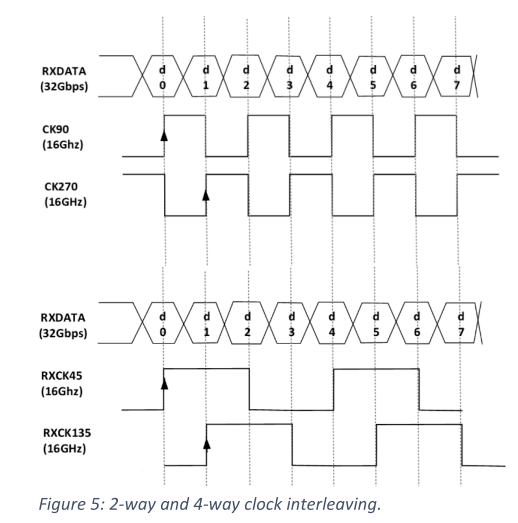

時(shí)鐘的兩個(gè)相位被分為偶數(shù)時(shí)鐘和奇數(shù)時(shí)鐘。對(duì)于4 GT/s, 8 GT/s, 12 GT/s和16 GT/s,兩個(gè)時(shí)鐘以90°和270°的相位,以一半數(shù)據(jù)速率(例如,2 GHz為4 GT/s, 4 GHz為8 GT/s)發(fā)出。這是基于傳輸端以0°相位傳輸數(shù)據(jù)而言的,因此到采樣器的時(shí)鐘和數(shù)據(jù)路徑之間所需的0.5 UI相位差。差分轉(zhuǎn)發(fā)時(shí)鐘的兩個(gè)邊緣都用來(lái)在RX處采樣,稱(chēng)為2路交錯(cuò)。對(duì)于24 GT/s和32 GT/s的操作,支持額外的可選4路交錯(cuò),配置為45/135度,以?xún)?yōu)化功率。圖5總結(jié)了用于實(shí)現(xiàn)靈活性和功率優(yōu)化的2路或4路時(shí)鐘交錯(cuò)選項(xiàng)。在較高的數(shù)據(jù)速率下,實(shí)現(xiàn)4路交錯(cuò)通常比2路交錯(cuò)更節(jié)能。在考慮到入口/出口延遲和相應(yīng)的高di/dt和更高的電源噪聲時(shí),建議使用全局時(shí)鐘方案獲取最佳的性能優(yōu)化。這在較低的數(shù)據(jù)速率下尤其重要,這也將與未來(lái)的3D die-to-die標(biāo)準(zhǔn)十分相關(guān)。

此外,PHY架構(gòu)還有一些附加細(xì)節(jié),包括一個(gè)Valid通道,用于在流量空閑時(shí)啟用時(shí)鐘門(mén)控(<1 ns)。我們估計(jì),在這種空閑狀態(tài)下,通過(guò)選通包括從鎖相環(huán)輸分布到每個(gè)PHY模塊的主干在內(nèi)的大部分時(shí)鐘,可以節(jié)省≥85%的總功率。這種方法在利用率低于100%情況下運(yùn)行的工作負(fù)載特別有效。我們還分配了一個(gè)Track通道,它可以在后臺(tái)由于溫度漂移而調(diào)整時(shí)鐘到數(shù)據(jù)的偏移。

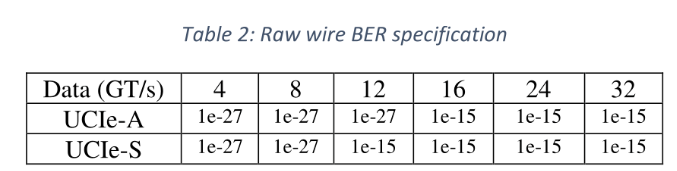

保持0.5 UI的時(shí)鐘到數(shù)據(jù)偏移的源同步時(shí)鐘,使得鏈路在電源噪聲環(huán)境中保持穩(wěn)定的性能。這使得可以采用較低的VCC,以實(shí)現(xiàn)最佳功率/延遲性能的最佳平衡,同時(shí)避免嚴(yán)格的電源調(diào)節(jié),以簡(jiǎn)化SoC集成。表2總結(jié)了在表1所示數(shù)據(jù)速率下,達(dá)到<<1.0的及時(shí)故障(FIT)率所需的原線(xiàn)誤碼率(BER)。在較低的操作數(shù)據(jù)速率下,PHY原線(xiàn)誤碼率為1e-27。在較高的數(shù)據(jù)速率下,原線(xiàn)誤碼率為1e-15;使用16位CRC可以實(shí)現(xiàn)目標(biāo)FIT。

C.標(biāo)準(zhǔn)封裝通道設(shè)計(jì)

我們根據(jù)最先進(jìn)的Flip-Chip封裝技術(shù)定義UCIe標(biāo)準(zhǔn)模塊,以實(shí)現(xiàn)表1中的性能目標(biāo)。我們的建議方案提供了很大的靈活性,包含了封裝行業(yè)中各種技術(shù)產(chǎn)品。我們建議采用一個(gè)固定大小的模塊,以促進(jìn)各芯片之間的互操作性。

圖6所示的Flip-Chip封裝,是當(dāng)今主流的封裝解決方案[8]。在過(guò)去的30年里,封裝技術(shù)獲得了極大的發(fā)展。目前,最大的層數(shù)大于20(例如,2個(gè)核心層,正反面均有9個(gè)堆砌層),最大的外形尺寸超過(guò)3000毫米?。為了與摩爾定律的擴(kuò)展保持同步,受控塌陷連接(C4)凸點(diǎn)的最小間距減小到約100 μ m,布線(xiàn)的最小間距減小到約20 μ m。這些使得每個(gè)布線(xiàn)層在芯片邊緣大約有20個(gè)IO/mm的密度。為了保持可負(fù)擔(dān)性,這些間距和密度預(yù)計(jì)將會(huì)緩慢增大。因此,更高的IO帶寬密度需要更多地依賴(lài)于更快的數(shù)據(jù)速率和更多的層數(shù)。

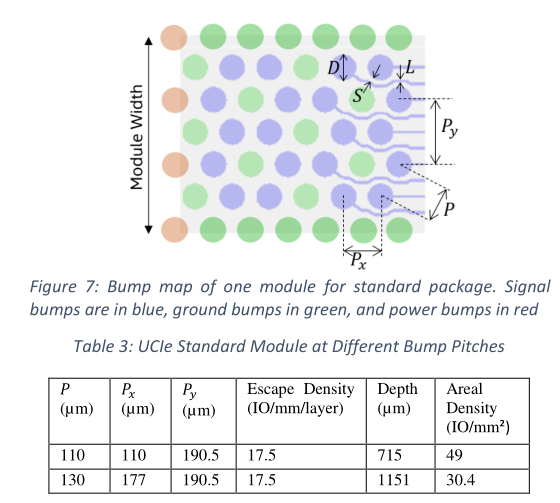

基本的UCIe-S模塊,無(wú)論是用于發(fā)射機(jī)(TX)還是接收機(jī)(RX),都由20個(gè)單向單端模式的信號(hào)組成。推薦的凸點(diǎn)排布如圖7所示。靠近裸芯邊緣的前10個(gè)信號(hào)在一個(gè)布線(xiàn)層中避開(kāi)凸點(diǎn)區(qū)域,而后面的其他10個(gè)信號(hào)在下一個(gè)布線(xiàn)層中使用相同的布線(xiàn)設(shè)計(jì)策略回避凸點(diǎn)區(qū)域。模塊寬度選擇為571.5μm,因此沿裸芯邊緣的間距Py為190.5μm。根據(jù)所選的技術(shù)選項(xiàng),其他尺寸的選擇是靈活的。表3列出了基于110 μ m和130 μ m最小凸距的兩種設(shè)計(jì)案例。對(duì)角線(xiàn)方向的間距P,深度方向的間距Px都有相應(yīng)的調(diào)整。其他尺寸需要滿(mǎn)足以下兩個(gè)條件:

P=D+L+2S (1)

P_y=D+3L+4S (2)

其中,D是通孔焊盤(pán)直徑,L是導(dǎo)線(xiàn)寬度,S是導(dǎo)線(xiàn)周?chē)拈g距。在571.5μm的模塊,引腳密度為17.5 IO/mm,兩個(gè)布線(xiàn)層總密度為35IO/mm。

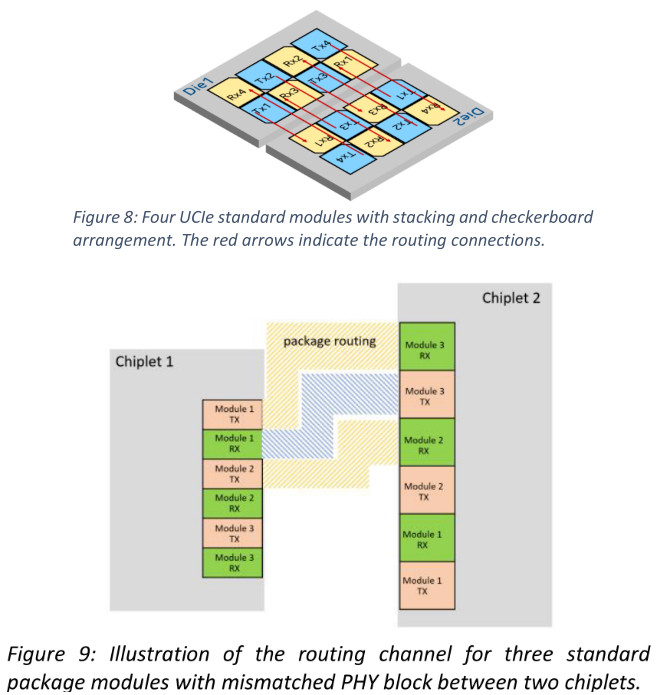

我們提出的UCIe-S模塊包括一個(gè)TX塊和一個(gè)RX塊。因此,全模組寬度為1143 μ m。引出走線(xiàn)的排序在TX和RX之間是對(duì)稱(chēng)的,因此一個(gè)PHY設(shè)計(jì)可以用來(lái)互連所有的Chiplet。標(biāo)準(zhǔn)模塊還支持堆疊,通過(guò)4個(gè)布線(xiàn)層層進(jìn)一步增加引出的IO密度至70 IO/mm。這些模塊以棋盤(pán)格的形式排列(圖8)。裸芯邊緣的模塊使用兩個(gè)頂層的走線(xiàn)層連接,而靠后的模塊使用兩個(gè)較深的路由層連接。我們建議堅(jiān)持相同的模塊寬度。如果兩個(gè)芯片之間的模塊寬度顯著不同(如圖9所示),則需要為扇入和扇出走線(xiàn)提供空間。這增加了通道長(zhǎng)度,并需要較大的裸芯間距離,此時(shí),兩個(gè)面對(duì)面的chiplet的PHY模塊過(guò)一個(gè)微小的芯片間隙互聯(lián)的方案是不可行的。

面積密度與凸點(diǎn)間距相關(guān)。如表3所示,較寬的間距會(huì)造成較大的凸點(diǎn)區(qū)域深度和較小的區(qū)域密度。封裝技術(shù)的進(jìn)步一直在推動(dòng)凸距變小,以增加面積密度。減少接地凸起也增加了區(qū)域密度。圖7中的凸點(diǎn)排布具有良好的接地隔離性,以確保通過(guò)深層封裝層的通道能夠滿(mǎn)足32GT/s的要求。然而,如果目標(biāo)數(shù)據(jù)速率較低,或如果不進(jìn)行模塊堆疊,且通空堆疊高度較低的話(huà),則可以減少接地凸點(diǎn)以節(jié)省硅面積。這樣就可以靈活地適應(yīng)帶寬密度、硅面積和包層數(shù)量之間的不同權(quán)衡。

D.先進(jìn)裝通道設(shè)計(jì)

在過(guò)去的十年中,出現(xiàn)了新的先進(jìn)的封裝架構(gòu),實(shí)現(xiàn)了封裝特征尺寸[8]的大幅減小。為了充分利用這些先進(jìn)技術(shù)的能力,我們定義了一個(gè)單獨(dú)的UCIe-A模塊來(lái)支持表1中的性能目標(biāo)。與標(biāo)準(zhǔn)模塊類(lèi)似,先進(jìn)模塊支持多種封裝技術(shù)。該模塊的建議邊緣寬度對(duì)于獨(dú)立開(kāi)發(fā)的芯片之間的互操作性至關(guān)重要。我們有內(nèi)置的修復(fù)冗余,這對(duì)實(shí)現(xiàn)良好的封裝良率至關(guān)重要。

工業(yè)上先進(jìn)的封裝技術(shù)使凸點(diǎn)間距小于55 μ m,并將布線(xiàn)間距改善到幾微米。其中許多技術(shù)都利用了硅制造能力。小通孔尺寸和良好的通孔排列使通孔能被走線(xiàn)所包圍。這為信號(hào)層間傳遞和交換布線(xiàn)順序創(chuàng)造了高度靈活性。這與標(biāo)準(zhǔn)封裝的解決方案有很大的不同。

圖7中標(biāo)準(zhǔn)模塊的凸點(diǎn)排布并不適用于先進(jìn)封裝技術(shù)。它強(qiáng)制采用16位集群設(shè)計(jì),并需要堆疊至少10個(gè)模塊,才能充分利用先進(jìn)封裝的布線(xiàn)密度。相應(yīng)片上數(shù)據(jù)進(jìn)出這些模塊的路徑非常復(fù)雜,阻礙了PHY的模塊化設(shè)計(jì)。它也不包含先進(jìn)封裝所要求的用于修復(fù)的冗余位。此外,圖8中的棋盤(pán)格模塊排列導(dǎo)致部分通道明顯變長(zhǎng),這將限制帶寬和電源效率。

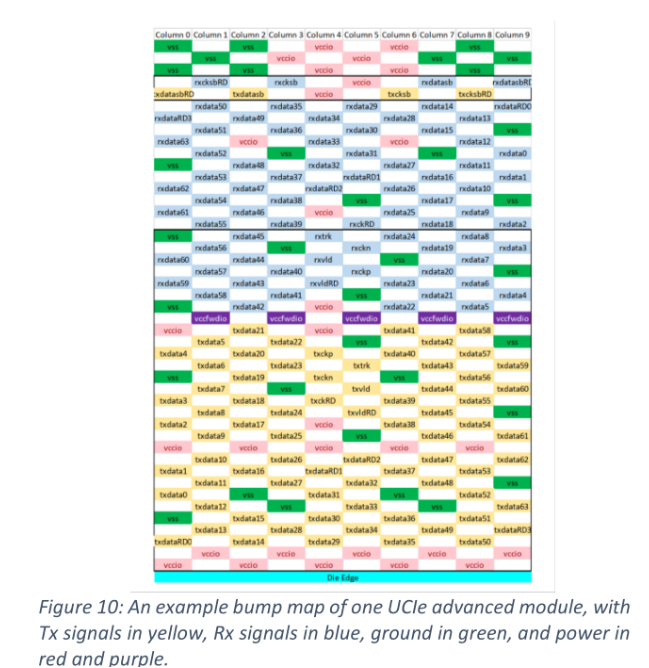

因此,先進(jìn)模塊被設(shè)計(jì)成不同的尺寸和外形。圖10顯示了一個(gè)基于45 μ m間距的凸點(diǎn)排布[4]。與標(biāo)準(zhǔn)模塊類(lèi)似,它由一個(gè)TX模塊和一個(gè)RX模塊組成。TX模塊靠近裸芯邊緣,而RX模塊在后面。兩者共74個(gè)信號(hào),其中數(shù)據(jù)通道64個(gè),overhead信號(hào)10個(gè)。其中一個(gè)特殊的overhead信號(hào)是用于修復(fù)的冗余信號(hào)。先進(jìn)的封裝解決方案通常涉及成千上萬(wàn)個(gè)小間距的微凸點(diǎn)互連。先進(jìn)模塊為每32個(gè)數(shù)據(jù)信號(hào)分配兩個(gè)冗余凸點(diǎn),以修復(fù)潛在的裝配故障。這是保證制造良率的必要條件。

模組寬度固定在388.8 μ m。當(dāng)使用先進(jìn)封裝時(shí),兩個(gè)芯片通常放在一起,以減少信道長(zhǎng)度,這對(duì)電源效率和收發(fā)器設(shè)計(jì)的非常關(guān)鍵。然而,如果兩個(gè)Chiplet之間的模塊寬度相差較大,扇入和扇出的連接空間就很小。這與圖9中標(biāo)準(zhǔn)封裝模塊的問(wèn)題類(lèi)似。由于先進(jìn)封裝信道具有很強(qiáng)的RC特性,對(duì)信道長(zhǎng)度非常敏感,模塊寬度不匹配會(huì)大大降低信道帶寬和功率效率。因此,固定的模塊寬度是芯片互操作的基礎(chǔ)。

45μm間距凸點(diǎn)共10列,模塊寬度388.8 μ m,如圖10所示。沿裸芯邊緣的凸距為77.76 μ m,在深度方向和對(duì)角線(xiàn)方向的凸距均約為45 μ m。這遵循六邊形模式,最大化了凸點(diǎn)密度。對(duì)于更緊密的凸點(diǎn)密度,可以調(diào)整列和行的數(shù)量,以實(shí)現(xiàn)最大的凸點(diǎn)密度。例如,如果封裝工藝支持25 μ m的最小凸距,則可以將列數(shù)增加到18個(gè),沿裸芯邊緣的凸距減小到43.2 μ m,使模塊寬度保持在388.8 μ m。沿深度和對(duì)角線(xiàn)方向的間距約為25 μ m。這也遵循一個(gè)六邊形的模式。

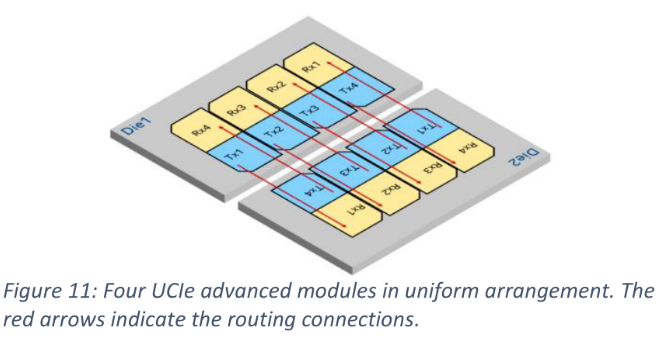

對(duì)于先進(jìn)模塊,裸芯邊緣的引出IO密度約為400 IO/mm。面積密度隨凸距的增大而增大。在45 μ m間距時(shí),凸點(diǎn)深度約為1 mm,因此面積密度約為400 IO/mm?。面積密度與凸距的平方呈反比關(guān)系,可以隨凸距減小而進(jìn)一步增大。先進(jìn)的封裝裝有通孔和導(dǎo)線(xiàn)的精細(xì)設(shè)計(jì)規(guī)則,因此凸點(diǎn)引出的限制比有機(jī)封裝少得多。TX和RX模塊可以沿裸芯邊緣均勻排列,而不是棋盤(pán)格圖案。如圖11所示,所有的TX模塊都可以放在模具邊緣,而所有的RX模塊都在它們的后面。這樣做有兩個(gè)優(yōu)點(diǎn):首先,它只需要單一的TX和RX塊設(shè)計(jì),因此簡(jiǎn)化了電路設(shè)計(jì)。第二,雙向的導(dǎo)線(xiàn)長(zhǎng)度相同。換句話(huà)說(shuō),它減少了最壞情況下的走線(xiàn)長(zhǎng)度。這大大提高了這些有損耗通道的帶寬。

圖示所示的高級(jí)模塊的凸點(diǎn)排布不適用于凸間距為110 μ m的標(biāo)準(zhǔn)封裝。標(biāo)準(zhǔn)封裝模塊至少2.5毫米深,而接地屏蔽遠(yuǎn)遠(yuǎn)不足以滿(mǎn)足標(biāo)準(zhǔn)封裝中的長(zhǎng)通孔。它將需要至少8個(gè)布線(xiàn)層來(lái)分解所有的信號(hào)。

4. 封裝通道性能結(jié)果

我們模擬了UCIe-S和UCIe-A模塊的參考通道,以驗(yàn)證其電氣性能。

A.標(biāo)準(zhǔn)封裝通道性能

標(biāo)準(zhǔn)封裝通道基于如圖8所示的堆疊模塊配置。各模塊采用圖7所示的凹凸圖,凹凸間距為110 μ m。封裝基板被假設(shè)為8-2-8,這表示在兩個(gè)核心層的正面和背面都有8個(gè)堆砌層。堆疊UCIe-S模塊的導(dǎo)線(xiàn)連接需要4層布線(xiàn)層,從封裝表面開(kāi)始依次為第2層、第4層、第6層、第8層。最壞的通道在第8金屬層,因?yàn)樗凶铋L(zhǎng)的垂直通過(guò)堆疊高度和最高的串?dāng)_。

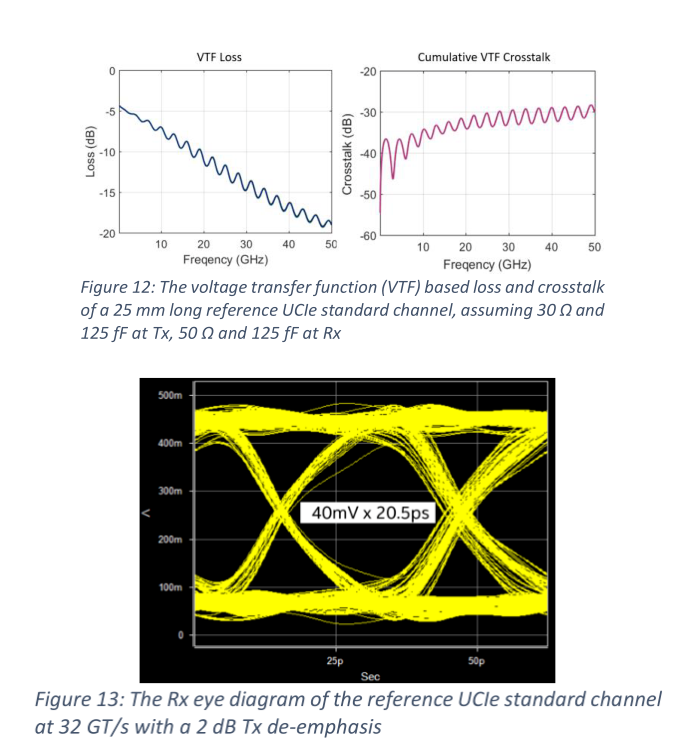

通道長(zhǎng)度取決于兩個(gè)芯片的位置。信道越長(zhǎng),損耗越大,信號(hào)裕度越差。圖12繪制了一個(gè)25mm長(zhǎng)的通道的特性。損耗和累積串?dāng)_是基于電壓傳遞函數(shù)(VTF)[4,9]而不是s參數(shù)。它將TX、RX的終端和容性負(fù)載與通道結(jié)合起來(lái)進(jìn)行綜合評(píng)價(jià)。在16 GHz時(shí),VTF損耗為-8.77 dB,累積VTF串?dāng)_為-31.3 dB。它們基于UCIe規(guī)范[4]中32gt /s標(biāo)準(zhǔn)封裝通道的TX和RX要求:TX終端30Ω,RX終端50Ω,TX和RX的等效電容均為125fF。低裸芯電容通常需要低壓靜電放電(ESD)保護(hù),片上電感線(xiàn)圈,TX和RX電路負(fù)載優(yōu)化。由于TX和RX的電阻終端和容性負(fù)載被納入圖12中的VTF損耗和串?dāng)_中,因此在通道特性中存在很小的反射。這些在時(shí)域仿真中可以被完全看到。在2 dB的TX去加重的情況下,32GT/s時(shí)的RX眼圖如圖13所示。根據(jù)峰值失真分析,在40 mV眼高時(shí),最壞情況下眼寬開(kāi)度大于65% UI。TX去加重有~10%的UI貢獻(xiàn)。除去時(shí)鐘和控制信號(hào)的開(kāi)銷(xiāo),整個(gè)芯片邊緣的數(shù)據(jù)帶寬密度達(dá)到了約224 GB/s/mm。

封裝內(nèi)通道可分為三段:第一個(gè)裸芯上的凸點(diǎn)引出區(qū)域、第一個(gè)裸芯與第二個(gè)裸芯之間的導(dǎo)線(xiàn)以及第二個(gè)裸芯的凸點(diǎn)接入?yún)^(qū)域。芯片間的連線(xiàn)通常是一條50 Ω?jìng)鬏斁€(xiàn),長(zhǎng)度可為兩毫米到十幾毫米。凸點(diǎn)引出和接入的片段非常短。整個(gè)通道相對(duì)簡(jiǎn)單。圖14顯示了16 GT/s時(shí)的裕量與圖12中參考通道的終端配置之間的關(guān)系。最佳的RX配置大約是50 Ω。這表明了50歐姆是減少RX反射的RX與通道阻抗匹配的首選。然而,TX端可以低于通道阻抗。較低的TX終端提高了進(jìn)入通道的電壓等級(jí),增加了RX電壓擺幅和信號(hào)裕度。然而,在TX端較大的不匹配將導(dǎo)致不必要的反射。因此,最佳的TX設(shè)置大約是30 Ω。對(duì)電阻終端的靈敏度不會(huì)受到TX去加重、電容負(fù)載或數(shù)據(jù)速率的明顯影響。對(duì)于較低數(shù)據(jù)速率和較短路徑的應(yīng)用,可以對(duì)終端進(jìn)行調(diào)整,換取更大的信號(hào)裕度和更好的能效。

B.先進(jìn)封裝通道性能

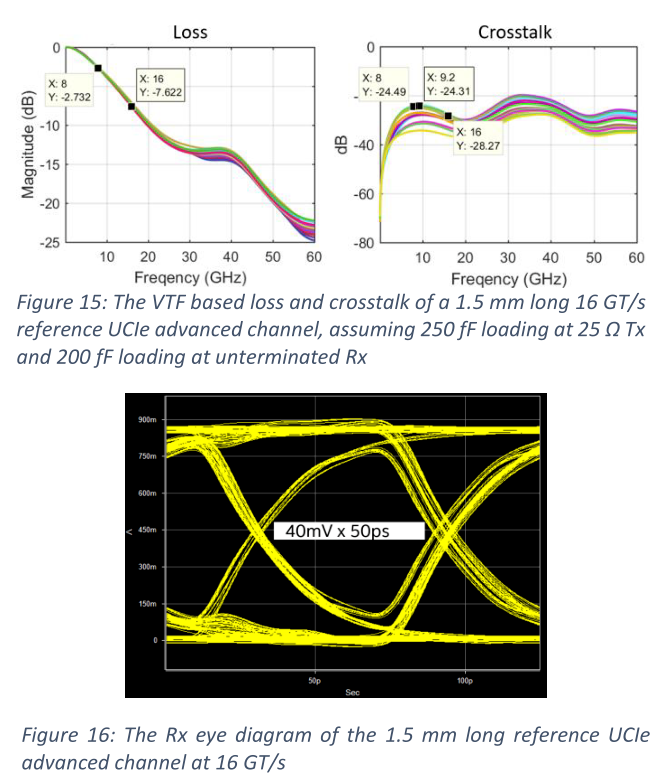

一個(gè)參考先進(jìn)封裝通道被放在一起來(lái)驗(yàn)證UCIe-A模塊的性能。凸點(diǎn)引出和布線(xiàn)是需要優(yōu)化的物理通道的兩個(gè)關(guān)鍵組件。凸點(diǎn)-通孔串?dāng)_對(duì)接地屏蔽的位置高度敏感。因此,屏蔽凸點(diǎn)的最佳位置需要在硅面積和串?dāng)_等級(jí)之間進(jìn)行權(quán)衡。金屬堆疊對(duì)線(xiàn)路性能影響很大。這是互連技術(shù)開(kāi)發(fā)的一個(gè)關(guān)鍵領(lǐng)域,用于優(yōu)化通道范圍、路由密度和帶寬。參考通道是基于圖10中的45 μ m間距凸點(diǎn)排布。基于1?m的最小寬度和間距設(shè)計(jì)規(guī)則進(jìn)行路徑設(shè)計(jì)。相反方向的信號(hào)被分成兩個(gè)路由層,中間以一個(gè)地面參考層隔開(kāi)。通道長(zhǎng)度假設(shè)為1.5 mm。圖15中疊加了20個(gè)信號(hào)的VTF損耗和累積串?dāng)_。最壞情況下VTF損耗在8 GHz時(shí)為-2.73 dB。最壞情況下累積VTF串?dāng)_在8 GHz時(shí)為-24.3 dB。VTF指標(biāo)是基于UCIe規(guī)范[4]中16GT/s先進(jìn)封裝通道的TX和RX要求: 25ΩTX上有250ff電容負(fù)載在以及在無(wú)端接的RX上有200 fF電容負(fù)載。由于難以在間距很小的凸點(diǎn)范圍內(nèi)安裝片上電感器,因此先進(jìn)封裝的電容負(fù)載更高。在16GT /s時(shí)對(duì)應(yīng)的RX眼圖如圖16所示。無(wú)端RX增加了電壓波動(dòng)。由于低損耗和低串?dāng)_達(dá)到奈奎斯特頻率,眼睛是廣泛打開(kāi)的。根據(jù)峰值失真分析,在不使用任何均衡電路的情況下,在40mv眼高處,最壞情況下眼寬開(kāi)度大于80% UI。這使得除開(kāi)銷(xiāo)信號(hào)外,以16GT/s速率跨越整個(gè)裸芯邊緣的帶寬密度約為658 GB/s/mm。這已經(jīng)是32 GT/s標(biāo)準(zhǔn)模塊的三倍。在相同的數(shù)據(jù)傳輸速率下,先進(jìn)模塊的帶寬密度是標(biāo)準(zhǔn)模塊的6倍。先進(jìn)的封裝技術(shù)正在迅速發(fā)展。設(shè)計(jì)特征尺寸不斷縮小,層數(shù)不斷增加。這些技術(shù)的進(jìn)步將繼續(xù)減少信道損耗和串?dāng)_,以支持更高的數(shù)據(jù)速率,如32 GT/s。

由于先進(jìn)封裝通道非常短,它對(duì)TX和RX終端的靈敏度與標(biāo)準(zhǔn)通道不同。圖17顯示了在16gt /s時(shí)的裕度與TX和RX終端配置之間的關(guān)系。它傾向于較強(qiáng)的TX,對(duì)RX終端未表現(xiàn)出顯著的敏感性。因此,我們?cè)O(shè)置UCIe-A TX終端電阻為25Ω,RX不端接。這樣可以最大化信道裕度,簡(jiǎn)化RX設(shè)計(jì),降低功耗。

5. 結(jié)論

該行業(yè)需要一個(gè)開(kāi)放的芯片生態(tài)系統(tǒng),它將會(huì)為計(jì)算機(jī)領(lǐng)域帶來(lái)革新。我們使用UCIe 1.0規(guī)范的方法提供了引人注目的電源效率和成本效益,并在前期解決了即插即用和規(guī)范性問(wèn)題。我們預(yù)計(jì)下一代的創(chuàng)新將發(fā)生在Chiplet級(jí)別,允許提供不同功能的芯片組合供客戶(hù)選擇,以最佳地滿(mǎn)足其應(yīng)用程序需求。

未來(lái),我們將對(duì)時(shí)鐘結(jié)構(gòu)和相應(yīng)的功率噪聲對(duì)信號(hào)裕度的影響進(jìn)行更多的靈敏度研究。隨著凸點(diǎn)間距的不斷縮小和3D封裝集成成為主流,我們期待有更多創(chuàng)新帶來(lái)更節(jié)能、更經(jīng)濟(jì)的解決方案。從延遲、帶寬和能效的角度來(lái)看,這些可能需要更寬的鏈路以更慢的速度運(yùn)行,并更接近于片上連接。在未來(lái)的幾十年里,封裝和半導(dǎo)體制造技術(shù)的進(jìn)步將徹底改變計(jì)算領(lǐng)域。UCIe做好了充分準(zhǔn)備,在生態(tài)系統(tǒng)中的不斷創(chuàng)新,以充分利用這些技術(shù)進(jìn)步。

感謝長(zhǎng)三角研究院(湖州)集成電路與系統(tǒng)研究中心的研究生劉洋同學(xué)和黃樂(lè)天老師對(duì)本文翻譯的支持和幫助。

更多信息可以來(lái)這里獲取==>>電子技術(shù)應(yīng)用-AET<<