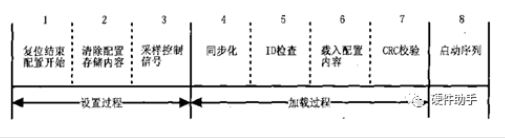

盡管FPGA的配置模式各不相同,但整個(gè)配置過程中FPGA的工作流程是一致的,分為三個(gè)部分:設(shè)置、加載、啟動(dòng)。

復(fù)位結(jié)束配置開始

有多種方式使FPGA的配置進(jìn)入這一過程。在上電時(shí),電壓達(dá)到FPGA要求之前,F(xiàn)PGA的上電復(fù)位模塊將使FPGA保持在復(fù)位狀態(tài);外部控制PROG_B引腳出現(xiàn)一個(gè)低脈沖也可以使FPGA保持在復(fù)位狀態(tài)。

清除配置存儲(chǔ)內(nèi)容

這一步稱為初始化,當(dāng)FPGA復(fù)位結(jié)束,配置存儲(chǔ)器的內(nèi)容會(huì)被自動(dòng)清除。在這個(gè)步驟中,除配置專用接口外,F(xiàn)PGA I/O均被置于高阻態(tài)。在整個(gè)初始化過程中,INIT_B引腳被置低并在初始化結(jié)束后恢復(fù)高電平。如果INIT_B信號(hào)在外部被拉低,F(xiàn)PGA將一直停留在初始化狀態(tài)。注意PROG_B信號(hào)的脈寬不能太窄。

采樣控制信號(hào)

初始化結(jié)束后,INIT_B信號(hào)回到高電平。FPGA開始采集模式選擇引腳M[1:0]和變量選擇引腳VS。如果為主動(dòng)模式,F(xiàn)PGA很快就會(huì)給出有效的CCLK。VS信號(hào)只在主動(dòng)BPI及其SPI模式中生效。此時(shí),F(xiàn)PGA開始在配置時(shí)鐘的上升沿對(duì)配置數(shù)據(jù)進(jìn)行采樣。

同步化

每一個(gè)FPGA配置數(shù)據(jù)流都有一個(gè)同步頭,它是一段特殊的同步字。同步字主要用于幫助FPGA確定正確的數(shù)據(jù)位置。同步字之前的配置數(shù)據(jù)都會(huì)被FPGA忽略,也就是FPGA僅僅在同步化之后才正式開始接收配置數(shù)據(jù)。一般而言,同步字都是由0/1數(shù)目相同的二進(jìn)制數(shù)組成的,如Spartan3為AA995566。

ID檢查

FPGA同步化后,會(huì)自動(dòng)檢測(cè)配置流中的器件ID和目標(biāo)器件ID是否一致。這一步確保了FPGA不會(huì)被錯(cuò)誤的配置流誤配置。

32位的ID中包含了28位的特征值和4位掩碼。特征值包括廠商信息,器件族,器件規(guī)模等。當(dāng)器件ID檢查遇到問題時(shí),F(xiàn)PGA會(huì)將內(nèi)部寄存器的第一位ID_Err置高,軟件也會(huì)顯示錯(cuò)誤信息。

載入配置內(nèi)容

在ID檢查順利通過后,F(xiàn)PGA開始加載配置數(shù)據(jù)。

CRC校驗(yàn)

在加載數(shù)據(jù)過程中,F(xiàn)PGA會(huì)對(duì)每一幀數(shù)據(jù)進(jìn)行CRC校驗(yàn)。如果失敗,F(xiàn)PGA會(huì)將INIT_B信號(hào)拉低并終止配置過程。

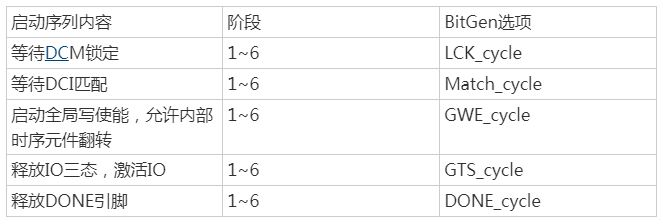

啟動(dòng)序列

FPGA配置數(shù)據(jù)加載完后,F(xiàn)PGA進(jìn)入啟動(dòng)序列。啟動(dòng)序列事件的默認(rèn)順序?yàn)橄柔尫臘ONE引腳,然后激活I(lǐng)/O,最后啟動(dòng)寫使能。實(shí)際使用中,可以通過BitGen參數(shù)對(duì)啟動(dòng)順序進(jìn)行設(shè)置來滿足不同的需求。

更多信息可以來這里獲取==>>電子技術(shù)應(yīng)用-AET<<