現(xiàn)場可編程門陣列(FPGA)可以實現(xiàn)任意數(shù)字邏輯,從微處理器到視頻生成器或加密礦機(jī),一應(yīng)俱全。FPGA由許多邏輯模塊組成,每個邏輯模塊通常由觸發(fā)器和邏輯功能以及連接邏輯模塊的路由網(wǎng)絡(luò)組成。FPGA的特殊之處在于它是可編程的硬件:您可以重新定義每個邏輯塊及其之間的連接,用來構(gòu)建復(fù)雜的數(shù)字電路,而無需物理上連接各個門和觸發(fā)器,也不必花費設(shè)計專用集成電路的費用。

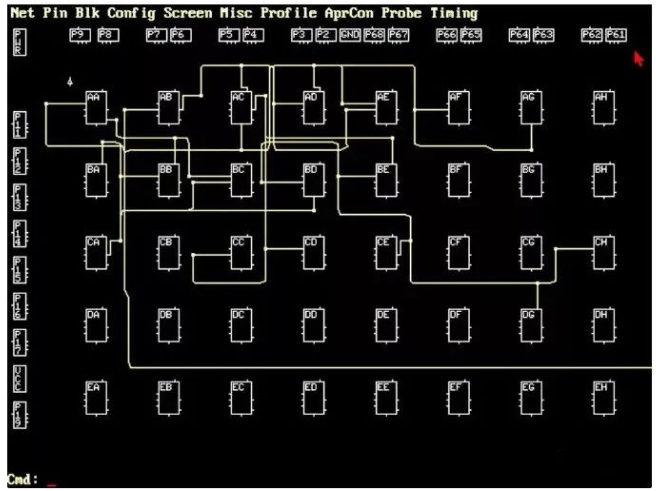

內(nèi)部裸片顯微照片

FPGA是由Ross Freeman發(fā)明的,他在1984年共同創(chuàng)立了Xilinx,并推出了第一款FPGA——XC2064。這種FPGA比現(xiàn)代FPGA簡單得多,它只包含64個邏輯塊。而現(xiàn)代FPGA中的邏輯塊有幾千個或數(shù)百萬個,但它導(dǎo)致了目前價值數(shù)十億美元的FPGA產(chǎn)業(yè)。由于其重要性,XC2064被列入芯片名人堂。在這篇文章中,我們對Xilinx的XC2064進(jìn)行了逆向工程,解釋了它的內(nèi)部電路(上圖)以及 "比特流 "是如何對它進(jìn)行編程的。

第一款FPGA芯片-Xilinx XC2064

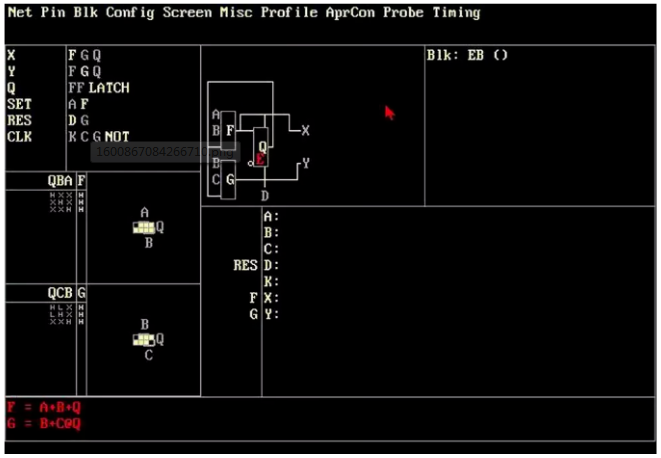

如今,F(xiàn)PGA是采用Verilog或VHDL之類的硬件描述語言編程的,但當(dāng)時Xilinx提供了他們自己的開發(fā)軟件XACT,運(yùn)行在MS-DOS操作系統(tǒng)之下,價格高達(dá)12,000美元。XACT自然無法與現(xiàn)在的FPGA開發(fā)工具相比,XACT通過用戶定義了每個邏輯塊的功能(如下面的屏截圖所示)以及邏輯塊之間的連接,對連接進(jìn)行布線連接,并生成可加載到FPGA中的比特流文件。

XACT的屏幕截圖

兩個查找表F和G在屏幕底部實現(xiàn)邏輯運(yùn)算,上面部分顯示該邏輯的卡諾圖

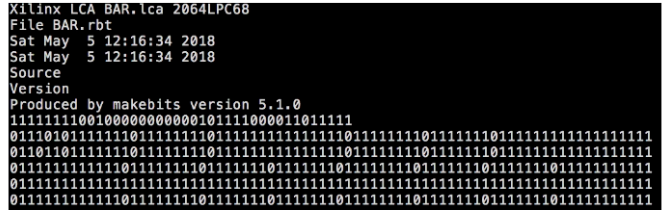

通過位流(具有專有格式的位序列)配置FPGA。如果您查看XC2064的比特流(如下所示),那是令人費解的混合模式,這些模式不規(guī)則地重復(fù),并散布在比特流中。XACT中的功能定義與位流中的數(shù)據(jù)之間沒有明確的聯(lián)系。但是,研究FPGA的物理電路可以揭示比特流數(shù)據(jù)的結(jié)構(gòu),并且可以理解。

通過位流(具有專有格式的位序列)配置FPGA。如果您查看XC2064的比特流(如下所示),那是令人費解的混合模式,這些模式不規(guī)則地重復(fù),并散布在比特流中。XACT中的函數(shù)定義與位流中的數(shù)據(jù)之間沒有明確的聯(lián)系。但是,研究FPGA的物理電路可以揭示比特流數(shù)據(jù)的結(jié)構(gòu),并且可以理解。

XC2064的比特流

FPGA如何工作

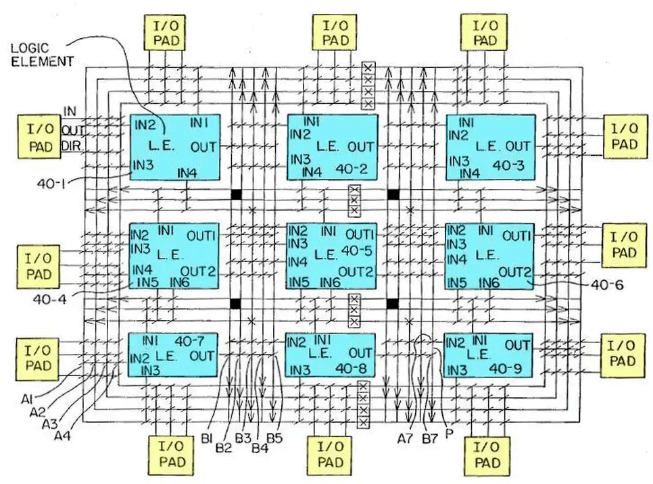

下圖來自原始FPGA專利,顯示了FPGA的基本結(jié)構(gòu)。在此簡化的FPGA中,有9個邏輯塊(藍(lán)色)和12個I/O引腳。互連網(wǎng)絡(luò)將組件連接在一起。通過設(shè)置互連上的開關(guān)(對角線),邏輯塊相互連接并連接到I/O引腳。每個邏輯元素都可以使用所需的邏輯功能進(jìn)行編程。其結(jié)果是一個高度可編程的芯片,可以實現(xiàn)任何適合可用的電路。

FPGA專利顯示通過互連連接的邏輯塊(LE)

CLB:可配置邏輯塊

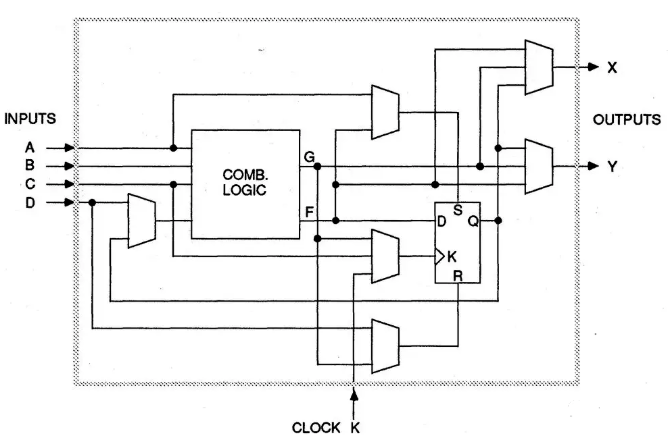

雖然上圖顯示了九個可配置邏輯塊(CLB),但XC2064有64個CLB。下圖顯示了每個CLB的結(jié)構(gòu)。每個CLB有四個輸入(A、B、C、D)和兩個輸出(X和Y)。兩者之間是組合邏輯,可以使用任何所需的邏輯功能進(jìn)行編程。CLB還包含一個觸發(fā)器,允許FPGA實現(xiàn)計數(shù)器、移位寄存器、狀態(tài)機(jī)和其他有狀態(tài)電路。梯形是多路復(fù)用器,可以編程通過其任何輸入。多路復(fù)用器允許為特定任務(wù)配置CLB,為觸發(fā)器控件和輸出選擇所需的信號。

XC2064中的可配置邏輯塊

那么,組合邏輯如何實現(xiàn)任意邏輯功能?它會采用與門、或門、異或門等邏輯嗎?

不,它使用一種稱為查找表(LUT)的巧妙技巧,實際上它包含的是邏輯功能的真值表。例如,三個變量的功能由其真值表中的8行定義。LUT由8位內(nèi)存以及多路復(fù)用電路組成,以選擇正確的值。通過將值存儲在這8位內(nèi)存中,可以實現(xiàn)任何3輸入邏輯功能。

互 連

FPGA的第二個關(guān)鍵部分是互連,可以對其進(jìn)行編程以不同方式連接CLB。互連相當(dāng)復(fù)雜,但是粗略的描述是每個CLB之間有幾個水平和垂直線段。CLB互連點允許在水平線和垂直線之間建立連接,從而可以創(chuàng)建任意路徑。

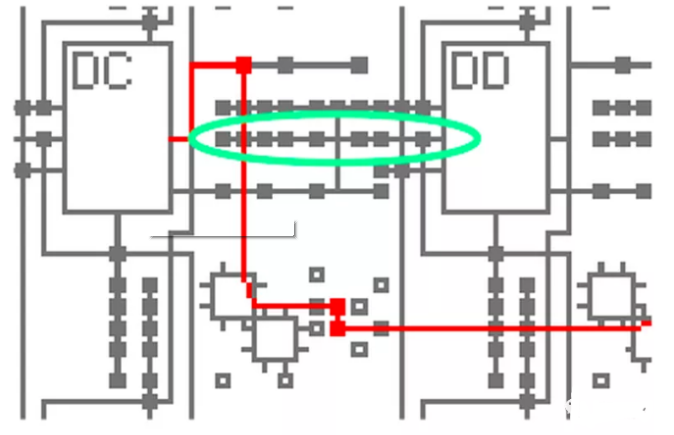

更復(fù)雜的連接通過“交換矩陣”(switchmatrices)完成。每個開關(guān)矩陣都有8個引腳,可以(幾乎)任意方式將它們連接在一起。下圖顯示了XC2064的互連結(jié)構(gòu),提供了到邏輯塊(青色)和I / O引腳(黃色)的連接。該圖顯示了路由功能的特寫。綠色框是8針開關(guān)矩陣,而小方塊是可編程的互連點。

XC2064 FPGA具有一個8x8的CLB網(wǎng)格

每個CLB都有從AA到HH的字母名稱。互連可以將例如塊DC的輸出連接到塊DE的輸入,如下所示。紅線表示路由路徑,紅色小方塊表示已激活的路由點。離開模塊DC后,信號由第一個路由點定向到8針開關(guān)(綠色),該信號將其引導(dǎo)到另外兩個路由點和另一個8針開關(guān)。(未顯示未使用的垂直和水平路徑。)請注意,布線相當(dāng)復(fù)雜;即使是這條短路徑,也使用了四個路由點和兩個開關(guān)。

從塊DC的輸出路由到塊DE的信號示例

下面的屏幕截圖顯示了 XACT 程序中的路由外觀。黃線指示邏輯塊之間的路由。隨著信號的加入,挑戰(zhàn)在于如何有效地路由而不使路徑發(fā)生沖突。XACT 軟件包執(zhí)行自動路由,但也可以手動編輯路由。

XACT程序的屏幕截圖

此MS-DOS程序通過鍵盤和鼠標(biāo)進(jìn)行控制

Implementation

本文的其余部分討論了XC2064的內(nèi)部電路,從裸片照片中的反向工程。

下圖顯示了XC2064芯片的布局。FPGA的主要部分是8×8的網(wǎng)格。每個圖塊包含一個邏輯塊和相鄰的路由電路。盡管圖片顯示將邏輯塊(CLB)顯示為與圍繞它們的路由不同的實體,但這并不是 FPGA的實現(xiàn)方式。取而代之的是,每個邏輯塊和相鄰路由都實現(xiàn)為單個實體,即圖塊。(具體來說,圖塊包括每個CLB上方和左側(cè)的路由。)

XC2064芯片的布局

I/O模塊圍繞集成電路的邊緣提供與外界的通信。它們連接到小的綠色方形焊盤,該焊盤連接到芯片的外部引腳。裸片被緩沖區(qū)(綠色)劃分:兩個垂直和兩個水平。這些緩沖器可放大在電路中傳播很長距離的信號,從而減少延遲。垂直移位寄存器(粉紅色)和水平列選擇電路(藍(lán)色)用于將比特流加載到芯片中,如下所述。

Tile的內(nèi)部結(jié)構(gòu)

下圖顯示了XC2064中單個Tile的布局;如上圖所示,該芯片包含64個這樣的Tile擠在一起。每個Tile約有40%的面積被保存配置位的內(nèi)存單元(綠色)所占據(jù)。頂部三分之一處通過兩個交換矩陣和許多單獨的路由交換處理互連路由,下面是邏輯塊。邏輯塊的關(guān)鍵部分是輸入的多路復(fù)用器、觸發(fā)器和查找表(LUT)。每個塊通過垂直和水平布線連接到相鄰的塊,以實現(xiàn)互連,電源和接地。配置數(shù)據(jù)位被水平地饋送到存儲單元,而垂直信號選擇要加載的存儲單元的特定列。

XC2064中單個Tile的布局

晶體管

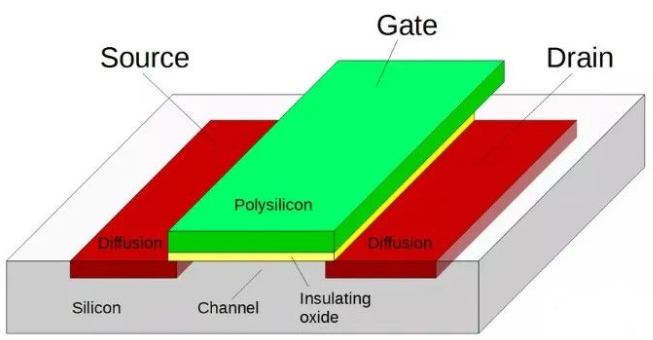

FPGA由CMOS邏輯實現(xiàn),該邏輯由NMOS和PMOS晶體管構(gòu)建。晶體管在FPGA中具有兩個主要作用。首先,可以將它們組合以形成邏輯門。其次,晶體管被用作信號通過的開關(guān),例如以控制路由。在此作用下,該晶體管稱為傳輸晶體管。

MOSFET的結(jié)構(gòu)

下面的裸片照片特寫顯示了在顯微鏡下晶體管的外觀。多晶硅柵極是兩個摻雜硅區(qū)域之間的蛇形線。

比特流和配置存儲

XC2064 中的配置信息存儲在配置內(nèi)存單元中。FPGA 的內(nèi)存不是使用 RAM 塊進(jìn)行存儲,而是分布在 160×71 網(wǎng)格中的芯片上,確保每個位都位于它控制電路旁邊。下圖顯示了配置比特流如何加載到 FPGA 中。比特流被送入從芯片中心(粉紅色)向下運(yùn)行的移位寄存器中。將 71 位加載到移位寄存器中后,列選擇電路(藍(lán)色)將選擇特定的內(nèi)存列,并并行加載到此列中。然后,將接下來的 71 位加載到移位寄存器中,左側(cè)的下一列將成為所選列。此過程將重復(fù) FPGA 的所有 160 列,將整個比特流加載到芯片中。使用移位寄存器可避免大量內(nèi)存尋址電路。

比特流如何加載到FPGA中

重要的是,比特流的分布與文件中的分布完全相同:比特流文件中的比特布局與芯片上的物理布局匹配。如下所示,每個位都存儲在FPGA控制電路的旁邊。因此,比特流文件格式直接由硬件電路的布局確定。例如,當(dāng)由于緩沖電路而在FPGA切片之間存在間隙時,相同的間隙會出現(xiàn)在位流中。比特流的內(nèi)容不是圍繞字段,數(shù)據(jù)表或配置塊之類的軟件概念來設(shè)計的。了解比特流取決于從硬件角度而非軟件角度進(jìn)行思考。

如下所示實現(xiàn)配置存儲器的每一位。每個存儲單元均包含兩個以環(huán)路連接的反相器。該電路具有兩個穩(wěn)定狀態(tài),因此可以存儲一個位:頂部反相器為1,底部反相器為0,反之亦然。為了寫入該單元,左側(cè)的傳輸晶體管被激活,使數(shù)據(jù)信號通過。數(shù)據(jù)線上的信號只會使逆變器過載,從而寫入所需的位。(您也可以使用相同的路徑從FPGA中讀取配置數(shù)據(jù)。)Q和反相Q輸出控制FPGA中所需的功能,例如關(guān)閉路由連接,為查找表提供位,或控制鎖存器電路。(在大多數(shù)情況下,僅使用Q輸出。)

下圖顯示了存儲單元的物理布局。左圖顯示了八個存儲單元,其中一個單元高亮顯示。每條水平數(shù)據(jù)線饋入該行中的所有存儲單元。每列選擇行選擇該列中的所有存儲單元以進(jìn)行寫入。中間照片放大了一個存儲單元的硅和多晶硅晶體管。

存儲單元的物理布局

查找表多路復(fù)用器

如前所述,F(xiàn)PGA通過使用查找表來實現(xiàn)任意邏輯功能。下圖顯示了如何在XC2064中實現(xiàn)查找表。左側(cè)的八個值存儲在八個存儲單元中。四個多路復(fù)用器根據(jù)A 輸入值選擇每對值中的一個 。如果 A 為0,則選擇最高值;如果 A 為1,則選擇最低值。接下來,較大的多路復(fù)用器根據(jù)B 和 選擇四個值之一 C。在這種情況下,結(jié)果是所需的值 A XOR B XOR C。通過在查找表中放置不同的值,可以根據(jù)需要更改邏輯功能。

使用查找表實現(xiàn)XOR

每個多路復(fù)用器都是通過晶體管來實現(xiàn)的。根據(jù)控制信號,其中一個傳遞晶體管被激活,將該輸入傳遞到輸出。下圖顯示了LUT電路的一部分,多路復(fù)用了其中的兩個比特。右邊是兩個存儲器單元。每一個比特都要經(jīng)過一個反相器進(jìn)行放大,然后經(jīng)過中間的多路復(fù)用器的傳遞晶體管,選擇其中的一個比特。

LUT實現(xiàn)中的電路特寫

鎖存器

每個CLB包含一個觸發(fā)器,允許FPGA實現(xiàn)鎖存器,狀態(tài)機(jī)和其他有狀態(tài)電路。下圖顯示了觸發(fā)器的實現(xiàn)。它使用主/輔助設(shè)計。當(dāng)時鐘為低電平時,第一個多路復(fù)用器讓數(shù)據(jù)進(jìn)入主鎖存器。當(dāng)時鐘變高時,多路復(fù)用器關(guān)閉第一個鎖存器的環(huán)路,并保持該值。(該位通過“或”門,“與非”門和反相器兩次反轉(zhuǎn),因此保持不變。)同時,當(dāng)時鐘變高時,輔助鎖存器的多路復(fù)用器從第一個鎖存器接收該位(請注意,時鐘已反轉(zhuǎn))。該值成為觸發(fā)器的輸出。當(dāng)時鐘變低時,次級的多路復(fù)用器關(guān)閉環(huán)路,從而鎖存該位。因此,觸發(fā)器是邊緣敏感的,在時鐘的上升沿鎖存該值。置位和復(fù)位線強(qiáng)制觸發(fā)器為高電平或低電平。

8-pin交換矩陣

交換矩陣是一個重要的路由元件。每個開關(guān)有八個"引腳"(每側(cè)兩個),幾乎可以連接任意引腳組合在一起。這允許信號比單個路由節(jié)點更靈活地轉(zhuǎn)動、拆分或交叉。下圖顯示了四個 CLB (cyan)之間的路由網(wǎng)絡(luò)的一部分。交換矩陣(綠色)可與右側(cè)連接的任意組合連接。請注意,每個引腳可以連接到其他 7 個引腳中的 5 個。例如,引腳 1 可以連接到引腳 3,但無法連接到引腳 2 或 4。這使得矩陣幾乎是一個橫欄,有20個潛在的連接,而不是28個。

開關(guān)矩陣由一排傳輸晶體管實現(xiàn),該傳輸晶體管由上方和下方的存儲單元控制。晶體管的兩側(cè)是可以通過該晶體管連接的兩個開關(guān)矩陣引腳。因此,每個開關(guān)矩陣具有20個相關(guān)聯(lián)的控制位。

每個圖塊兩個矩陣,即每個圖塊產(chǎn)生40個控制位。下圖顯示了其中一個存儲單元,該存儲單元連接到下面的傳輸晶體管的長彎曲柵極。該晶體管控制引腳5和引腳1之間的連接。

其中一個存儲單元

因此,與該存儲單元相對應(yīng)的位流中的位控制引腳5和引腳1之間的開關(guān)連接。同樣,其他存儲單元及其相關(guān)晶體管控制其他開關(guān)連接。請注意,這些連接的順序不遵循特定的模式。因此,位流位和開關(guān)引腳之間的映射是隨機(jī)的。

輸入路由

CLB的輸入在位流中使用不同的編碼方案,這由硬件實現(xiàn)方式解釋。在下圖中,八個圓圈的節(jié)點是CLB框DD的潛在輸入。

CLB的輸入在位流中使用的編碼方案示意圖

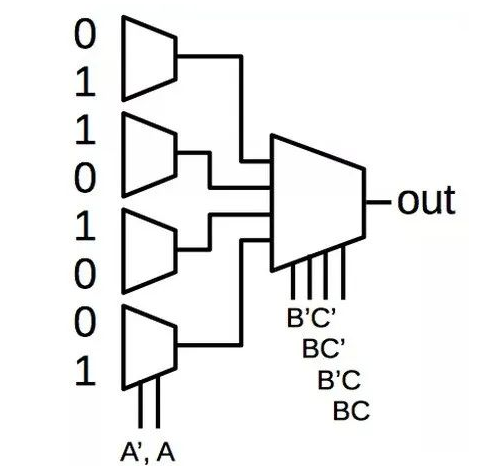

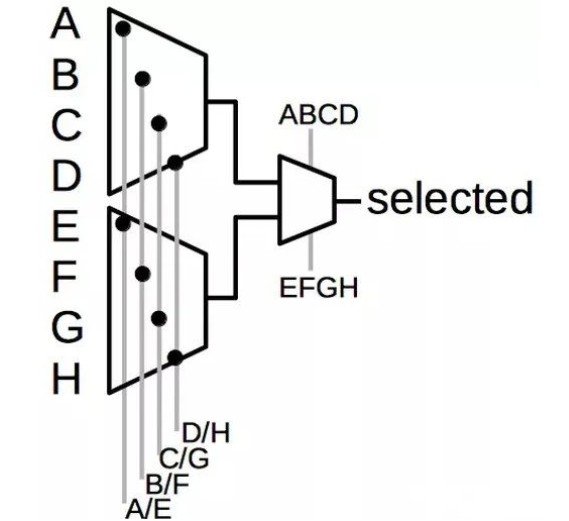

最多只能將一個節(jié)點配置為輸入,因為將兩個信號連接到同一輸入將使它們短路。使用多路復(fù)用器選擇所需的輸入。一個簡單的解決方案是使用8路多路復(fù)用器,其中3個控制位選擇8個信號之一。另一個簡單的解決方案是使用8個通過晶體管,每個晶體管都有自己的控制信號,其中一個選擇所需的信號。但是,F(xiàn)PGA使用一種混合方法,該方法避免了第一種方法的解碼硬件,但使用了5個控制信號,而不是第二種方法所需的8個控制信號。

FPGA使用多路復(fù)用器選擇八個輸入之一

上面的示意圖顯示了FPGA中使用的兩級多路復(fù)用器方法。在第一階段,控制信號之一被激活。第二階段從頂部或底部選擇信號作為輸出。例如,假設(shè)控制信號 B/F 發(fā)送到第一級,“ ABCD”發(fā)送到第二級;輸入B是唯一將傳遞到輸出的B。因此,選擇八個輸入之一需要在比特流中使用5位,并使用5個存儲單元。

結(jié) 論

XC2064使用各種高度優(yōu)化的電路來實現(xiàn)其邏輯塊和路由。該電路需要緊湊的布局,以適合芯片。即使這樣,XC2064還是一個非常大的芯片,比當(dāng)時的微處理器還大,因此一開始很難制造,而且要花費數(shù)百美元。與現(xiàn)代FPGA相比,XC2064的單元數(shù)量非常少,但是即使如此,它也引發(fā)了革命性的新產(chǎn)品線。

了解XC2064比特流的關(guān)鍵是兩個概念。首先,F(xiàn)PGA由64個塊組成,這些塊是將邏輯塊和路由結(jié)合在一起的重復(fù)塊。盡管FPGA被描述為具有被路由包圍的邏輯塊,但這并不是實現(xiàn)它們的方式。

第二個概念是,比特流中沒有抽象。它直接映射到FPGA的二維布局中。因此,只有考慮FPGA的物理布局,比特流才有意義。

更多信息可以來這里獲取==>>電子技術(shù)應(yīng)用-AET<<

電子技術(shù)應(yīng)用專欄作家 FPGA開源工作室

原文鏈接:https://mp.weixin.qq.com/s/nvtkXATnV_eGP7Ejq_xRig