邏輯電路" target="_blank">組合邏輯電路與時(shí)序邏輯電路

數(shù)字電路根據(jù)邏輯功能的不同特點(diǎn),可以分成兩大類:一類叫做組合邏輯電路,簡稱組合電路或組合邏輯;另一類叫做時(shí)序邏輯電路,簡稱時(shí)序電路或時(shí)序邏輯。

如果數(shù)字電路滿足任意時(shí)刻的輸出僅僅取決于該時(shí)刻的輸入,那么該數(shù)字電路為組合邏輯電路。相反,如果數(shù)字電路任意時(shí)刻的輸出不僅取決于當(dāng)前時(shí)刻的輸入,而且還取決于數(shù)字電路原來的狀態(tài),那么該數(shù)字電路為時(shí)序邏輯電路。例如,下圖中只由一個(gè)與門組成的電路就是一個(gè)組合邏輯電路。

對(duì)于上圖所示數(shù)字電路,無論在任何時(shí)刻,并且無論上次A、B輸入是什么情況,只要在當(dāng)前時(shí)刻輸入端口A、B同時(shí)為邏輯1時(shí),輸出端C才會(huì)輸出邏輯1,而其他情況下輸出端C都會(huì)輸出邏輯0。由此可見符合組合邏輯電路的定義。

如果上圖中與門的兩個(gè)輸入端分別是來自一個(gè)寄存器的輸入和輸出,如下圖所示,那么這就肯定是一個(gè)時(shí)序電路。

對(duì)于上圖所示數(shù)字電路,假設(shè)寄存器中目前保存的值是邏輯1,而此時(shí)輸入端B沒有從邏輯0到邏輯1的跳變(B相當(dāng)于寄存器的時(shí)鐘信號(hào)),設(shè)此時(shí)B為邏輯0,那么如果輸入端A為邏輯1,則C輸出邏輯1;但是如果過了一段時(shí)間后,A變?yōu)?,且隨后B的上升沿到來,那么寄存器中保持的值變?yōu)檫壿?,那么在這之后,若令輸入端A為邏輯1,B為邏輯0,則由于寄存器中保存著邏輯0值,所以C輸出邏輯0。對(duì)比前后兩種情況,A、B兩端的輸入都是邏輯1,但是C的輸出卻不同。由此可見,該數(shù)字電路的輸出并不完全由輸入決定,因此它是一個(gè)時(shí)序邏輯電路。

對(duì)比如上兩例我們可以看出,時(shí)序邏輯電路和組合邏輯電路并不是完全割裂開來的,而更像是一種包含關(guān)系,即時(shí)序邏輯電路中肯定有組合邏輯的成分存在,但組合邏輯電路中卻不可能有時(shí)序邏輯的成分存在。由此可見,只要加以恰當(dāng)?shù)南拗疲瑫r(shí)序邏輯電路甚至可以完全模擬組合邏輯電路的功能,例如查找表LUT。FPGA中用LUT來實(shí)現(xiàn)組合邏輯,但是LUT本身是不包含任何功能的,在FPGA上電或配置的時(shí)候?qū)ζ渲械拇鎯?chǔ)載體進(jìn)行相關(guān)設(shè)定的賦值,然后LUT由于記住了這個(gè)賦值設(shè)定,才能模仿各種各樣的組合邏輯功能。由于FPGA一般都是基于SRAM工藝的,因此FPGA中的LUT不太可能是基于多路選擇器和一系列到電源和地的熔絲組成,如果該查找表是由ROM、RAM或者寄存器等實(shí)現(xiàn)的,那么它也是有記憶的,只不過在整個(gè)電路工作期間,它不會(huì)改變自己的記憶罷了。所以,我們可以認(rèn)為時(shí)序邏輯電路是有記憶的,而組合邏輯電路是無記憶的。有記憶的可以模仿無記憶的,而無記憶的卻不能模仿有記憶的。

同步邏輯電路與異步邏輯電路

基于FPGA的設(shè)計(jì)幾乎都是時(shí)序邏輯電路,極少會(huì)有設(shè)計(jì)純組合邏輯電路的情況。記憶性賦予時(shí)序邏輯電路更多的功能和更豐富的表達(dá),因此,時(shí)序邏輯電路在FPGA的設(shè)計(jì)中占有非常重要的地位。對(duì)于時(shí)序邏輯,按信號(hào)間關(guān)系來看,又可分為同步時(shí)序邏輯和異步時(shí)序邏輯,簡稱同步邏輯和異步邏輯。

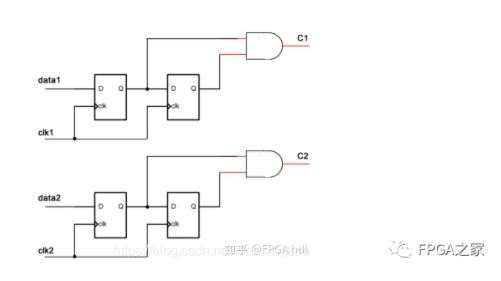

時(shí)序邏輯電路中最關(guān)鍵的就是驅(qū)動(dòng)各個(gè)記憶元素(例如寄存器、RAM甚至鎖存器等)進(jìn)行記憶動(dòng)作的時(shí)鐘信號(hào)。通常,我們認(rèn)為只被一個(gè)時(shí)鐘信號(hào)驅(qū)動(dòng)的設(shè)計(jì)叫做同步時(shí)序邏輯。這是因?yàn)樗杏洃浽囟荚诒煌粋€(gè)時(shí)鐘信號(hào)驅(qū)動(dòng),那么它們的輸出都會(huì)同時(shí)變化,所以它們對(duì)數(shù)字電路的影響是同步的。例如下圖:

不過這個(gè)定義還有些狹隘,廣義的同步時(shí)序邏輯概念中,允許數(shù)字電路中有多個(gè)時(shí)鐘存在,但是這些時(shí)鐘之間應(yīng)該有著固定的因果關(guān)系,又或者它們所驅(qū)動(dòng)的記憶單元在電路上是完全隔離的。對(duì)于第一種情況:如果多個(gè)時(shí)鐘信號(hào)之間有固定的因果關(guān)系的話,那么即使它們對(duì)電路的影響不是完全同時(shí)的,但可以根據(jù)時(shí)鐘之間的因果關(guān)系推斷出這種時(shí)間上的固定誤差,從而電路狀態(tài)的變化也是完全可預(yù)期的,因此可以認(rèn)為是同步。例如

如果多個(gè)時(shí)鐘驅(qū)動(dòng)的記憶單元之間完全是隔離的,那么其實(shí)它們就是多個(gè)同步時(shí)序邏輯電路的簡單集合體,因此也是同步的。例如:

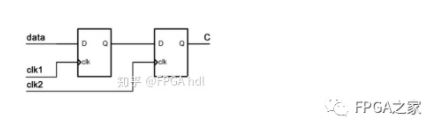

那么從廣義同步時(shí)序邏輯電路的概念出發(fā),凡是不符合的即屬于異步時(shí)序邏輯電路。不過這樣的定義顯得太過偷懶,那么這里總結(jié)一下異步時(shí)序邏輯的特點(diǎn),給出異步時(shí)序邏輯電路的概念:如果時(shí)序邏輯電路存在至少一個(gè)這樣的組合邏輯功能塊——它的輸入、輸出端口不全來自或?qū)胍粋€(gè)時(shí)鐘或若干個(gè)具有因果關(guān)系的時(shí)鐘所驅(qū)動(dòng)的記憶元素,那么該電路為異步時(shí)序邏輯電路。例如,下圖組合邏輯(一根連線也是組合邏輯,可看成緩沖門)的輸入由clk1時(shí)鐘驅(qū)動(dòng)的寄存器提供,輸出卻給了clk2驅(qū)動(dòng)的寄存器。

或下圖,與門的輸入來自不同的時(shí)鐘所驅(qū)動(dòng)的寄存器。

或下圖,與門的兩個(gè)輸入一個(gè)來自時(shí)鐘驅(qū)動(dòng)的寄存器,一個(gè)來自純組合的輸入端口。

對(duì)比同步邏輯和異步邏輯的概念,我們可以了解到它們也不是完全割裂開來的,其實(shí)也是一種包含關(guān)系。即異步邏輯中肯定有同步邏輯的成分在,但是同步邏輯中不可能有異步的成分在。關(guān)于異步時(shí)序邏輯電路的使用一定要盡量避免,如果不能避免一定要非常的謹(jǐn)慎和小心。

更多信息可以來這里獲取==>>電子技術(shù)應(yīng)用-AET<<