1、什么是Setup 和Holdup時(shí)間?

答:Setup/hold TIme 是測(cè)試芯片對(duì)輸入信號(hào)和時(shí)鐘信號(hào)之間的時(shí)間要求。

建立時(shí)間是指觸發(fā)器的時(shí)鐘信號(hào)上升沿到來(lái)以前,數(shù)據(jù)穩(wěn)定不變的時(shí)間。輸入信號(hào)應(yīng)提前時(shí)鐘上升沿(如上升沿有效)T時(shí)間到達(dá)芯片,這個(gè)T就是建立時(shí)間-Setup TIme。如不滿足setup TIme,這個(gè)數(shù)據(jù)就不能被這一時(shí)鐘打入觸發(fā)器,只有在下一個(gè)時(shí)鐘上升沿,數(shù)據(jù)才能被打入觸發(fā)器。

保持時(shí)間是指觸發(fā)器的時(shí)鐘信號(hào)上升沿到來(lái)以后,數(shù)據(jù)穩(wěn)定不變的時(shí)間。如果holdTIme不夠,數(shù)據(jù)同樣不能被打入觸發(fā)器。

2、什么是競(jìng)爭(zhēng)與冒險(xiǎn)現(xiàn)象?解決辦法?

答:在組合邏輯中,由于門的輸入信號(hào)通路中經(jīng)過(guò)了不同的延時(shí),導(dǎo)致到達(dá)該門的時(shí)間不一致叫競(jìng)爭(zhēng)。產(chǎn)生毛刺叫冒險(xiǎn)。如果布爾式中有相反的信號(hào)則可能產(chǎn)生競(jìng)爭(zhēng)和冒險(xiǎn)現(xiàn)象。

解決方法:一是添加布爾式的消去項(xiàng),二是在芯片外部加電容。三加選通信號(hào)。用D觸發(fā)器,格雷碼計(jì)數(shù)器,同步電路等優(yōu)秀的設(shè)計(jì)方案可以消除。

3、如何解決亞穩(wěn)態(tài)?Metastability

答:亞穩(wěn)態(tài)是指觸發(fā)器無(wú)法在某個(gè)規(guī)定時(shí)間段內(nèi)達(dá)到一個(gè)可確認(rèn)的狀態(tài)。當(dāng)一個(gè)觸發(fā)器進(jìn)入亞穩(wěn)態(tài)時(shí),既無(wú)法預(yù)測(cè)該單元的輸出電平,也無(wú)法預(yù)測(cè)何時(shí)輸出才能穩(wěn)定在某個(gè)正確的電平上。在這個(gè)穩(wěn)定期間,觸發(fā)器輸出一些中間級(jí)電平,或者可能處于振蕩狀態(tài),并且這種無(wú)用的輸出電平可以沿信號(hào)通道上的各個(gè)觸發(fā)器級(jí)聯(lián)式傳播下去。

解決方法:

1 、降低系統(tǒng)時(shí)鐘頻率

2 、用反應(yīng)更快的Flip-Flop

3 、引入同步機(jī)制,防止亞穩(wěn)態(tài)傳播

4 、改善時(shí)鐘質(zhì)量,用邊沿變化快速的時(shí)鐘信號(hào)

關(guān)鍵是器件使用比較好的工藝和時(shí)鐘周期的裕量要大。

4、說(shuō)說(shuō)靜態(tài)、動(dòng)態(tài)時(shí)序模擬的優(yōu)缺點(diǎn)

靜態(tài)時(shí)序分析是采用窮盡分析方法來(lái)提取出整個(gè)電路存在的所有時(shí)序路徑,計(jì)算信號(hào)在這些路徑上的傳播延時(shí),檢查信號(hào)的建立和保持時(shí)間是否滿足時(shí)序要求,通過(guò)對(duì)最大路徑延時(shí)和最小路徑延時(shí)的分析,找出違背時(shí)序約束的錯(cuò)誤。它不需要輸入向量就能窮盡所有的路徑,且運(yùn)行速度很快、占用內(nèi)存較少,不僅可以對(duì)芯片設(shè)計(jì)進(jìn)行全面的時(shí)序功能檢查,而且還可利用時(shí)序分析的結(jié)果來(lái)優(yōu)化設(shè)計(jì),因此靜態(tài)時(shí)序分析已經(jīng)越來(lái)越多地被用到數(shù)字集成電路設(shè)計(jì)的驗(yàn)證中。

動(dòng)態(tài)時(shí)序模擬就是通常的仿真,因?yàn)椴豢赡墚a(chǎn)生完備的測(cè)試向量,覆蓋門級(jí)網(wǎng)表中的每一條路徑。因此在動(dòng)態(tài)時(shí)序分析中,無(wú)法暴露一些路徑上可能存在的時(shí)序問(wèn)題;

靜態(tài)時(shí)序分析缺點(diǎn):

1、無(wú)法識(shí)別偽路徑

2、不適合異步電路

3、不能驗(yàn)證功能

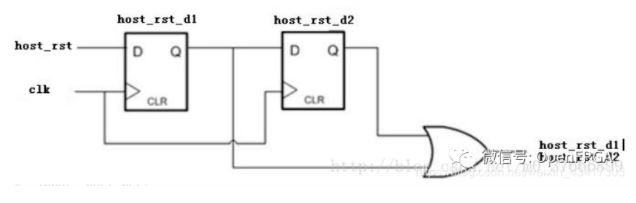

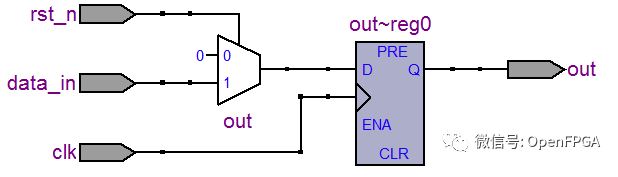

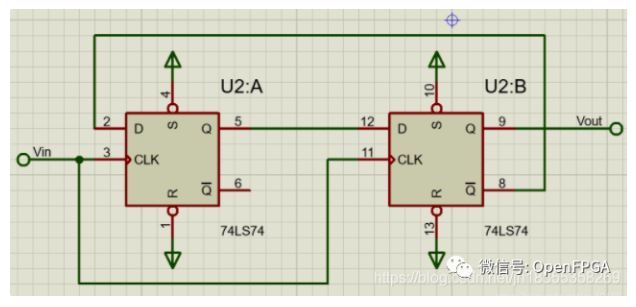

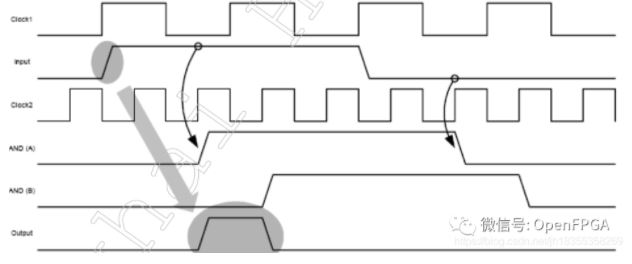

5、用VERILOG寫一段代碼,實(shí)現(xiàn)消除一個(gè)glitch。 濾掉小于1個(gè)周期glitch的原理圖如下:

verilog代碼實(shí)現(xiàn)如下:

module digital_filter_(clk_in,rst,host_rst,host_rst_filter);

input clk_in;

input rst;

input host_rst;

output host_rst_filter;

reg host_rst_d1;

reg host_rst_d2;

always@(posedge clk_in or negedge rst)

begin

if(~rst)

begin

host_rst_d1 <= 1'b1;

host_rst_d2 <= 1'b1;

end

else

begin

host_rst_d1 <= host_rst;

host_rst_d2 <= host_rst_d1;

end

end

assign host_rst_filter = host_rst_d1 | host_rst_d2;

endmodule

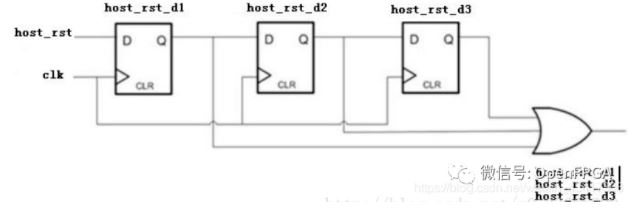

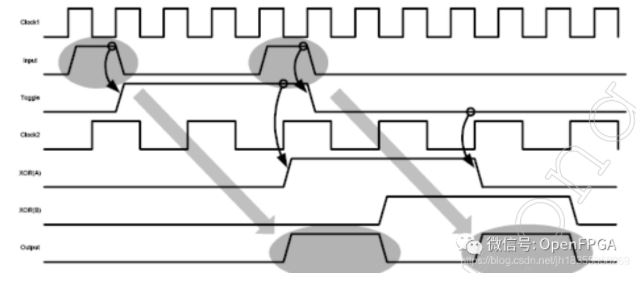

濾掉大于1個(gè)周期且小于2個(gè)周期glitch的原理圖如下:

verilog代碼實(shí)現(xiàn)如下:

module digital_filter_(clk_in,rst,host_rst,host_rst_filter);

input clk_in;

input rst;

input host_rst;

output host_rst_filter;

reg host_rst_d1;

reg host_rst_d2;

reg host_rst_d3;

always@(posedge clk_in or negedge rst)

begin

if(~rst)

begin

host_rst_d1 <= 1'b1;

host_rst_d2 <= 1'b1;

host_rst_d3 <= 1'b1;

end

else

begin

host_rst_d1 <= host_rst;

host_rst_d2 <= host_rst_d1;

host_rst_d3 <= host_rst_d2;

end

end

assign host_rst_filter = host_rst_d1 | host_rst_d2 | host_rst_d3;

endmodule

6、簡(jiǎn)述建立時(shí)間和保持時(shí)間 建立時(shí)間Tsu(setup):觸發(fā)器在時(shí)鐘上升沿到來(lái)之前,其數(shù)據(jù)輸入端的數(shù)據(jù)必須保持不變的最小時(shí)間。 保持時(shí)間Th(hold):觸發(fā)器在時(shí)鐘上升沿到來(lái)之后,其數(shù)據(jù)輸入端的數(shù)據(jù)必須保持不變的最小時(shí)間。 7、簡(jiǎn)述觸發(fā)器和鎖存器之間的差別 鎖存器對(duì)電平信號(hào)敏感,在輸入脈沖的電平作用下改變狀態(tài)。 D觸發(fā)器對(duì)時(shí)鐘邊沿敏感,檢測(cè)到上升沿或下降沿觸發(fā)瞬間改變狀態(tài)。 8、計(jì)算最小周期

Tco:寄存器時(shí)鐘輸入到數(shù)據(jù)輸出的時(shí)間 Tdata:寄存器間的走線延遲 Tsu :建立時(shí)間 Tskew:時(shí)鐘偏斜 最小時(shí)鐘周期:

Tmin = Tco + Tdata + Tsu - Tskew。最快頻率Fmax = 1/Tmin

Tskew = Tclkd – Tclks。

9、時(shí)鐘抖動(dòng)和時(shí)鐘偏移的概念及產(chǎn)生原因,如何避免? 時(shí)鐘抖動(dòng)jitter:指時(shí)鐘信號(hào)的跳變沿不確定,故是時(shí)鐘頻率上的不一致。 時(shí)鐘偏移Skew:指全局時(shí)鐘產(chǎn)生的各個(gè)子時(shí)鐘信號(hào)到達(dá)不同觸發(fā)器的時(shí)間點(diǎn)不同,是時(shí)鐘相位的不一致。 jitter主要受外界干擾引起,通過(guò)各種抗干擾手段可以避免。而skew由數(shù)字電路內(nèi)部各路徑布局布線長(zhǎng)度和負(fù)載不同導(dǎo)致,利用全局時(shí)鐘網(wǎng)絡(luò)可盡量將其消除。 10、同步復(fù)位和異步復(fù)位的區(qū)別

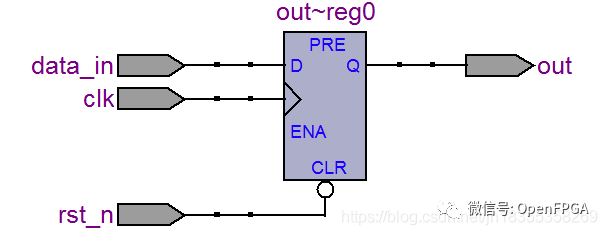

同步復(fù)位是復(fù)位信號(hào)隨時(shí)鐘邊沿觸發(fā)有效。異步復(fù)位是復(fù)位信號(hào)有效和時(shí)鐘無(wú)關(guān)。 如異步復(fù)位:

同步復(fù)位:

同步邏輯和異步邏輯的區(qū)別: 同步邏輯是時(shí)鐘之間有固定的因果關(guān)系。異步邏輯是各時(shí)鐘之間沒(méi)有固定的因果關(guān)系 同步電路和異步電路區(qū)別: 同步電路有統(tǒng)一的時(shí)鐘源,經(jīng)過(guò)PLL分頻后的時(shí)鐘驅(qū)動(dòng)的模塊,因?yàn)槭且粋€(gè)統(tǒng)一的時(shí)鐘源驅(qū)動(dòng),所以還是同步電路。異步電路沒(méi)有統(tǒng)一的時(shí)鐘源。 同步復(fù)位和異步復(fù)位的優(yōu)缺點(diǎn): 同步復(fù)位優(yōu)點(diǎn):

有利于仿真器的仿真

可以使所設(shè)計(jì)的系統(tǒng)100%成為同步電路,這有利于時(shí)序分析,而且綜合出來(lái)的Fmax一般較高

因?yàn)樗挥凶哂行У臅r(shí)鐘沿到來(lái)時(shí)才有效,所有濾除了高于時(shí)鐘周期頻率的毛刺

缺點(diǎn):

復(fù)位信號(hào)必須大于時(shí)鐘周期,才能使其真正被系統(tǒng)識(shí)別并完成復(fù)位任務(wù)。同時(shí)還要考慮諸如時(shí)鐘偏斜、組合邏輯路徑延遲等因素。

由于大部分的邏輯器件庫(kù)中的DFF都只有異步復(fù)位端口,所以采用同步復(fù)位的情況下,綜合器就會(huì)在寄存器的數(shù)據(jù)輸入端口插入組合邏輯,這樣會(huì)耗費(fèi)更多的邏輯資源。

異步復(fù)位的優(yōu)點(diǎn):

大部分的邏輯器件庫(kù)中的DFF都只有異步復(fù)位端口,因此采用異步復(fù)位更省資源

設(shè)計(jì)相對(duì)簡(jiǎn)單

異步復(fù)位信號(hào)識(shí)別方便,可以很方便的使用FPGA的全局復(fù)位端口GSR

缺點(diǎn):

在異步復(fù)位釋放的時(shí)候容易出問(wèn)題,具體來(lái)說(shuō)就是:假如復(fù)位釋放時(shí)正好在時(shí)鐘有效沿附近,就很容易出現(xiàn)亞穩(wěn)態(tài)

復(fù)位信號(hào)容易受毛刺影響

11、什么是線與邏輯?在硬件電路上有什么要求? 線與邏輯是指兩根線直接相連能夠?qū)崿F(xiàn)與的功能。在硬件上需要OC門,如果不采用OC門會(huì)會(huì)導(dǎo)致門電路管電流過(guò)大而燒壞邏輯門。用OC門實(shí)現(xiàn)線與,應(yīng)在輸出端口加一個(gè)上拉電阻。

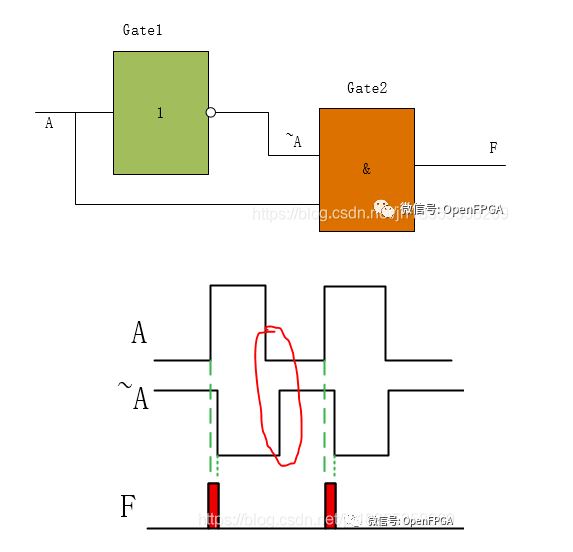

12、什么是競(jìng)爭(zhēng)冒險(xiǎn)?如何判斷?怎么樣消除?

在組合邏輯電路中,同一信號(hào)經(jīng)過(guò)不同的路徑到達(dá)某一匯合點(diǎn)的時(shí)間有先有后,這種現(xiàn)象稱為競(jìng)爭(zhēng)。 由于競(jìng)爭(zhēng)而使電路發(fā)生瞬時(shí)錯(cuò)誤的現(xiàn)象稱為冒險(xiǎn)。 消除方法: 1、輸出端加濾波電容。在輸出端和地直接接一個(gè)幾十皮法的電容可以吸收掉尖峰干擾脈沖。 2、加選通脈沖 3、修改邏輯設(shè)計(jì) 4、利用格雷碼每次只有一位跳變,消除了競(jìng)爭(zhēng)冒險(xiǎn)產(chǎn)生的條件。

舉例:

下面這個(gè)電路,使用了兩個(gè)邏輯門,一個(gè)非門和一個(gè)與門,本來(lái)在理想情況下F的輸出

應(yīng)該是一直穩(wěn)定的0輸出,但是實(shí)際上每個(gè)門電路從輸入到輸出是一定會(huì)有時(shí)間延遲的,

這個(gè)時(shí)間通常叫做電路的開關(guān)延遲。而且制作工藝、門的種類甚至制造時(shí)微小的工藝偏

差,都會(huì)引起這個(gè)開關(guān)延遲時(shí)間的變化。

F = A & ~A

有競(jìng)爭(zhēng)不一定產(chǎn)生冒險(xiǎn),如紅線處。有冒險(xiǎn)一定存在競(jìng)爭(zhēng)。

13、異步FIFO深度計(jì)算

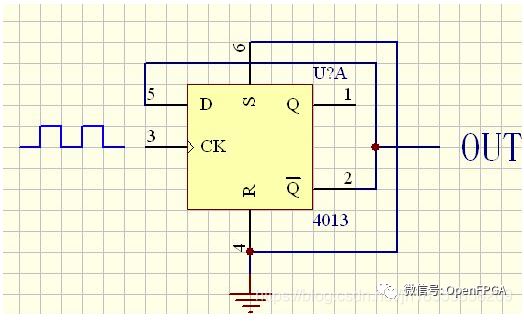

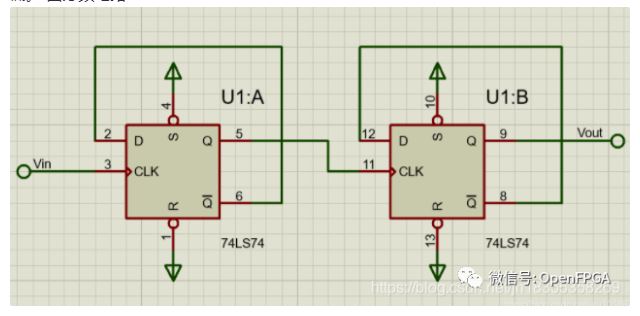

如果數(shù)據(jù)流連續(xù)不斷則FIFO深度無(wú)論多少,只要讀寫時(shí)鐘不同源同頻則都會(huì)丟數(shù); FIFO用于緩沖塊數(shù)據(jù)流,一般用在寫快讀慢時(shí), FIFO深度 / (寫入速率 - 讀出速率) = FIFO被填滿時(shí)間 應(yīng)大于 數(shù)據(jù)包傳送時(shí)間= 數(shù)據(jù)量 / 寫入速率 例:A/D采樣率50MHz,dsp讀A/D讀的速率40MHz,要不丟失地將10萬(wàn)個(gè)采樣數(shù)據(jù)送入DSP,在A/D在和DSP之間至少加多大容量(深度)的FIFO才行? 100,000 / 50MHz = 1/ 500 s = 2ms (50MHz - 40MHz) * 1/500 = 20k既是FIFO深度。 14、畫出用D觸發(fā)器實(shí)現(xiàn)2倍分頻的邏輯電路

將D觸發(fā)器的Q非端接到數(shù)據(jù)輸入端D即可實(shí)現(xiàn)二分頻,說(shuō)白了就是CLK時(shí)鐘信號(hào)的一個(gè)周期Q端電平反轉(zhuǎn)一次。Q和~Q輸出的都是二分頻電路,只不過(guò)是反相的。~Q是先高后低。 四分頻電路:

15、系統(tǒng)最高速度計(jì)算(最快時(shí)鐘頻率)和流水線設(shè)計(jì)思想: 同步電路的速度是指同步系統(tǒng)時(shí)鐘的速度,同步時(shí)鐘愈快,電路處理數(shù)據(jù)的時(shí)間間隔越短,電路在單位時(shí)間內(nèi)處理的數(shù)據(jù)量就愈大。假設(shè)Tco是觸發(fā)器的輸入數(shù)據(jù)被時(shí)鐘打入到觸發(fā)器到數(shù)據(jù)到達(dá)觸發(fā)器輸出端的延時(shí)時(shí)間(Tco=Tsetpup+Thold);Tdelay是組合邏輯的延時(shí);Tsetup是D觸發(fā)器的建立時(shí)間。假設(shè)數(shù)據(jù)已被時(shí)鐘打入D觸發(fā)器,那么數(shù)據(jù)到達(dá)第一個(gè)觸發(fā)器的Q輸出端需要的延時(shí)時(shí)間是Tco,經(jīng)過(guò)組合邏輯的延時(shí)時(shí)間為Tdelay,然后到達(dá)第二個(gè)觸發(fā)器的D端,要希望時(shí)鐘能在第二個(gè)觸發(fā)器再次被穩(wěn)定地打入觸發(fā)器,則時(shí)鐘的延遲必須大于Tco+Tdelay+Tsetup,也就是說(shuō)最小的時(shí)鐘周期Tmin =Tco+Tdelay+Tsetup,即最快的時(shí)鐘頻率Fmax =1/Tmin。FPGA開發(fā)軟件也是通過(guò)這種方法來(lái)計(jì)算系統(tǒng)最高運(yùn)行速度Fmax。因?yàn)門co和Tsetup是由具體的器件工藝決定的,故設(shè)計(jì)電路時(shí)只能改變組合邏輯的延遲時(shí)間Tdelay,所以說(shuō)縮短觸發(fā)器間組合邏輯的延時(shí)時(shí)間是提高同步電路速度的關(guān)鍵所在。由于一般同步電路都大于一級(jí)鎖存,而要使電路穩(wěn)定工作,時(shí)鐘周期必須滿足最大延時(shí)要求。故只有縮短最長(zhǎng)延時(shí)路徑,才能提高電路的工作頻率。可以將較大的組合邏輯分解為較小的N塊,通過(guò)適當(dāng)?shù)姆椒ㄆ骄峙浣M合邏輯,然后在中間插入觸發(fā)器,并和原觸發(fā)器使用相同的時(shí)鐘,就可以避免在兩個(gè)觸發(fā)器之間出現(xiàn)過(guò)大的延時(shí),消除速度瓶頸,這樣可以提高電路的工作頻率。這就是所謂“流水線”技術(shù)的基本設(shè)計(jì)思想,即原設(shè)計(jì)速度受限部分用一個(gè)時(shí)鐘周期實(shí)現(xiàn),采用流水線技術(shù)插入觸發(fā)器后,可用N個(gè)時(shí)鐘周期實(shí)現(xiàn),因此系統(tǒng)的工作速度可以加快,吞吐量加大。注意,流水線設(shè)計(jì)會(huì)在原數(shù)據(jù)通路上加入延時(shí),另外硬件面積也會(huì)稍有增加。

16、FPGA設(shè)計(jì)工程師努力的方向: SOPC、SOC,高速串行I/O,低功耗,可靠性,可測(cè)試性和設(shè)計(jì)驗(yàn)證流程的優(yōu)化等方面。 隨著芯片工藝的提高,芯片容量、集成度都在增加,F(xiàn)PGA設(shè)計(jì)也朝著高速、高度集成、低功耗、高可靠性、高可測(cè)、可驗(yàn)證性發(fā)展。芯片可測(cè)、可驗(yàn)證,正在成為復(fù)雜設(shè)計(jì)所必備的條件,盡量在上板之前查出bug,將發(fā)現(xiàn)bug的時(shí)間提前,這也是一些公司花大力氣設(shè)計(jì)仿真平臺(tái)的原因。另外隨著單板功能的提高、成本的壓力,低功耗也逐漸進(jìn)入FPGA設(shè)計(jì)者的考慮范圍,完成相同的功能下,考慮如何能夠使芯片的功耗最低,據(jù)說(shuō)altera、xilinx都在根據(jù)自己的芯片特點(diǎn)整理如何降低功耗的文檔。高速串行IO的應(yīng)用,也豐富了FPGA的應(yīng)用范圍,像xilinx的v2pro中的高速鏈路也逐漸被應(yīng)用。

17、異步信號(hào)同步處理

對(duì)于單bit信號(hào): 慢時(shí)鐘域到快時(shí)鐘域信號(hào)的轉(zhuǎn)換,用沿同步:

要求輸入異步信號(hào)的寬度應(yīng)該有兩個(gè)快速時(shí)鐘域的時(shí)鐘周期(在快時(shí)鐘域下打兩拍,采上升沿。需要前面的限制嗎?)。 快時(shí)鐘域到慢時(shí)鐘域信號(hào)的轉(zhuǎn)換,用脈沖同步:

要求輸入異步脈沖信號(hào)之間的間隔至少要在兩個(gè)慢速時(shí)鐘的時(shí)鐘周期之上,如果小于這 個(gè)值,兩個(gè)快時(shí)鐘域的單bit信號(hào)轉(zhuǎn)到慢時(shí)鐘域可能就變成了一個(gè)兩周期寬度的信號(hào)了。

18、FPGA中可以綜合實(shí)現(xiàn)為RAM/ROM/CAM的三種資源及其注意事項(xiàng)? 三種資源:BLOCK RAM,觸發(fā)器(FF),查找表(LUT); 注意事項(xiàng): 1:在生成RAM等存儲(chǔ)單元時(shí),應(yīng)該首選BLOCK RAM 資源;其原因有二:第一:使用BLOCK RAM等資源,可以節(jié)約更多的FF和4-LUT等底層可編程單元。使用BLOCK RAM可以說(shuō)是“不用白不用”,是最大程度發(fā)揮器件效能,節(jié)約成本的一種體現(xiàn);第二:BLOCK RAM是一種可以配置的硬件結(jié)構(gòu),其可靠性和速度與用LUT和REGISTER構(gòu)建的存儲(chǔ)器更有優(yōu)勢(shì)。 2:弄清FPGA的硬件結(jié)構(gòu),合理使用BLOCK RAM資源; 3:分析BLOCK RAM容量,高效使用BLOCK RAM資源; 4:分布式RAM資源(DISTRIBUTE RAM) 查找表(look-up-table)簡(jiǎn)稱為L(zhǎng)UT,LUT本質(zhì)上就是一個(gè)RAM。目前FPGA中多使用4(V7和A7都是6輸入)輸入的LUT,所以每一個(gè)LUT可以看成一個(gè)有 4位地址線的16x1的RAM。當(dāng)用戶通過(guò)原理圖或HDL語(yǔ)言描述了一個(gè)邏輯電路以后,PLD/FPGA開發(fā)軟件會(huì)自動(dòng)計(jì)算邏輯電路的所有可能的結(jié)果,并把結(jié)果事先寫入RAM,這樣,每輸入一個(gè)信號(hào)進(jìn)行邏輯運(yùn)算就等于輸入一個(gè)地址進(jìn)行查表,找出地址對(duì)應(yīng)的內(nèi)容,然后輸出即可

19、HDL語(yǔ)言的層次概念? HDL語(yǔ)言是分層次的、類型的,最常用的層次概念有系統(tǒng)與標(biāo)準(zhǔn)級(jí)、功能模塊級(jí),行為級(jí),寄存器傳輸級(jí)和門級(jí)。系統(tǒng)級(jí),算法級(jí),RTL級(jí)(行為級(jí)),門級(jí),開關(guān)級(jí)

20、IC設(shè)計(jì)前端到后端的流程和EDA工具? 設(shè)計(jì)前端也稱邏輯設(shè)計(jì),后端設(shè)計(jì)也稱物理設(shè)計(jì),兩者并沒(méi)有嚴(yán)格的界限,一般涉及到與工藝有關(guān)的設(shè)計(jì)就是后端設(shè)計(jì)。 1:規(guī)格制定:客戶向芯片設(shè)計(jì)公司提出設(shè)計(jì)要求。 2:詳細(xì)設(shè)計(jì):芯片設(shè)計(jì)公司(Fabless)根據(jù)客戶提出的規(guī)格要求,拿出設(shè)計(jì)解決方案和具體實(shí)現(xiàn)架構(gòu),劃分模塊功能。目前架構(gòu)的驗(yàn)證一般基于systemC語(yǔ)言,對(duì)價(jià)后模型的仿真可以使用systemC的仿真工具。例如:CoCentric和Visual Elite等。 3:HDL編碼:設(shè)計(jì)輸入工具:ultra ,visual VHDL等 4:仿真驗(yàn)證:modelsim 5:邏輯綜合:synplify 6:靜態(tài)時(shí)序分析:synopsys的Prime Time 7:形式驗(yàn)證:Synopsys的Formality.

IC設(shè)計(jì)分為前端和后端。前端設(shè)計(jì)主要將HDL語(yǔ)言-->網(wǎng)表,后端設(shè)計(jì)是網(wǎng)表-->芯片版圖。 前端主要有需求分析與架構(gòu)設(shè)計(jì)、RTL設(shè)計(jì)、仿真驗(yàn)證、邏輯綜合、STA、形式驗(yàn)證。后端主要包括DFT、布局規(guī)劃、布線以及版圖物理驗(yàn)證。

21、MOORE 與 MEELEY狀態(tài)機(jī)的特征?

Moore 狀態(tài)機(jī)的輸出僅與當(dāng)前狀態(tài)值有關(guān), 且只在時(shí)鐘邊沿到來(lái)時(shí)才會(huì)有狀態(tài)變化。 Mealy 狀態(tài)機(jī)的輸出不僅與當(dāng)前狀態(tài)值有關(guān), 而且與當(dāng)前輸入值有關(guān)。

22、說(shuō)說(shuō)靜態(tài)、動(dòng)態(tài)時(shí)序模擬的優(yōu)缺點(diǎn)? 靜態(tài)時(shí)序分析是采用窮盡分析方法來(lái)提取出整個(gè)電路存在的所有時(shí)序路徑,計(jì)算信號(hào)在這些路徑上的傳播延時(shí),檢查信號(hào)的建立和保持時(shí)間是否滿足時(shí)序要求,通過(guò)對(duì)最大路徑延時(shí)和最小路徑延時(shí)的分析,找出違背時(shí)序約束的錯(cuò)誤。它不需要輸入向量就能窮盡所有的路徑,且運(yùn)行速度很快、占用內(nèi)存較少,不僅可以對(duì)芯片設(shè)計(jì)進(jìn)行全面的時(shí)序功能檢查,而且還可利用時(shí)序分析的結(jié)果來(lái)優(yōu)化設(shè)計(jì),因此靜態(tài)時(shí)序分析已經(jīng)越來(lái)越多地被用到數(shù)字集成電路設(shè)計(jì)的驗(yàn)證中。 動(dòng)態(tài)時(shí)序模擬就是通常的仿真,因?yàn)椴豢赡墚a(chǎn)生完備的測(cè)試向量,覆蓋門級(jí)網(wǎng)表中的每一條路徑。因此在動(dòng)態(tài)時(shí)序分析中,無(wú)法暴露一些路徑上可能存在的時(shí)序問(wèn)題;

23、FPGA內(nèi)部結(jié)構(gòu)及資源: FPGA主要由可編程單元、可編程I/O單元及布線資源構(gòu)成。 可編程邏輯單元(可配置邏輯單元,CLB)由兩個(gè)SLICE構(gòu)成,SLICE主要包括實(shí)現(xiàn)組合邏輯的LUT和實(shí)現(xiàn)時(shí)序邏輯的觸發(fā)器。FPGA內(nèi)部還包含專用存儲(chǔ)單元BRAM,運(yùn)算單元DSP Slice,及專用內(nèi)嵌功能單元,如:PLL、Serdes等。

24、名詞解釋,寫出下列縮寫的中文(或者英文)含義: FPGA :Field Programmable Gate Array 現(xiàn)場(chǎng)可編程門陣列 VHDL:( Very-High-Speed Integrated Circuit Hardware Description Language) 甚高速集成電路硬件描述語(yǔ)言 HDL :Hardware Description Language硬件描述語(yǔ)言 EDA:Electronic Design Automation 電子設(shè)計(jì)自動(dòng)化 CPLD:Complex Programmable Logic Device 復(fù)雜可編程邏輯器件 PLD :Programmable Logic Device 可編程邏輯器件 GAL:generic array logic 通用陣列邏輯 LAB:Logic Array Block 邏輯陣列塊 CLB :Configurable Logic Block 可配置邏輯模塊 EAB: Embedded Array Block 嵌入式陣列塊 SOPC: System-on-a-Programmable-Chip可編程片上系統(tǒng) LUT :Look-Up Table 查找表 JTAG: Joint Test Action Group 聯(lián)合測(cè)試行為組織 IP: Intellectual Property 知識(shí)產(chǎn)權(quán) ASIC :Application Specific Integrated Circuits 專用集成電路 ISP :In System Programmable 在系統(tǒng)可編程 ICR :In Circuit Re-config 在電路可重構(gòu) RTL: Register Transfer Level 寄存器傳輸級(jí)

25、FPGA內(nèi)部LUT實(shí)現(xiàn)組合邏輯的原理: LUT相當(dāng)于存放邏輯表達(dá)式對(duì)應(yīng)真值表的RAM。軟件將邏輯表達(dá)式所有可能結(jié)果列出后存放在RAM中,輸入作為RAM地址,輸出為邏輯運(yùn)算結(jié)果。如使用LUT模擬二輸入“與”邏輯。列出真值表:00 – 0,01 – 0,10 – 0,11 – 1。此時(shí)將00 01 10 11作為地址線,依次將結(jié)果0 0 0 1存放在RAM中。當(dāng)輸入00時(shí)及輸出0&0=0.

26、 低功耗技術(shù): 功耗可用公式描述:Power = KFCV^2,即功率等于常數(shù)系數(shù)工作頻率負(fù)載電容值*電壓的平方。 故從以下幾個(gè)方面降低功耗方式: a.控制工作頻率:降低頻率增大數(shù)據(jù)路徑寬度,動(dòng)態(tài)頻率調(diào)整,門控時(shí)鐘(時(shí)鐘使能有效時(shí)鐘才進(jìn)入寄存器時(shí)鐘輸入引腳) b.減少電容負(fù)載:使用幾何尺寸更小的邏輯門,其電容負(fù)載較小,功率也隨之減少。 c.降低工作電壓:動(dòng)態(tài)改變工作電壓、零操作電壓(直接關(guān)閉系統(tǒng)中一部分的電源)

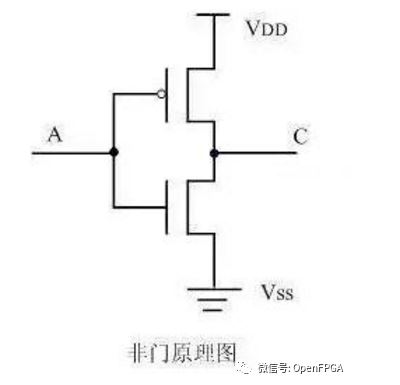

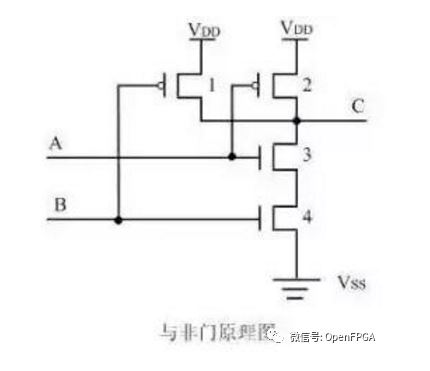

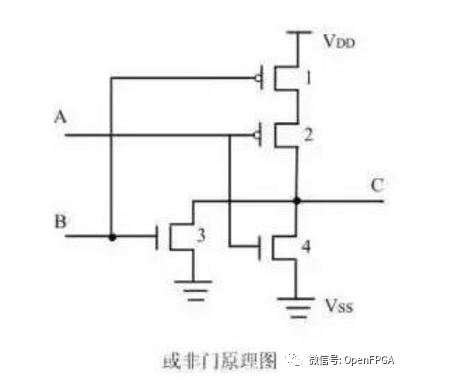

27、MOS管基本概念及畫圖: MOS中文意思是金屬氧化物半導(dǎo)體場(chǎng)效應(yīng)管,由柵極(G)、漏級(jí)(D)、源級(jí)(S)組成。分為PMOS和NMOS兩種類型,區(qū)別在于G級(jí)高電平時(shí),N型管導(dǎo)通,P型管截止。兩者往往是成對(duì)出現(xiàn)的,即CMOS。只要一只導(dǎo)通,另一只則不導(dǎo)通,現(xiàn)代單片機(jī)主要是采用CMOS工藝制成的。 畫圖一般需要根據(jù)一個(gè)簡(jiǎn)單的邏輯表達(dá)式,畫出CMOS電路圖結(jié)構(gòu)。需要掌握常用邏輯門的實(shí)現(xiàn)方式。

總體來(lái)看還是挺好記的,與非門和或非門都是上下各兩個(gè)MOS管,且上面是PMOS,下面是NMOS。不同之處在于與非是“上并下串”,或非是“上串下并”。

28、FPGA詳細(xì)設(shè)計(jì)流程(面試提問(wèn)) 與數(shù)字IC設(shè)計(jì)流程類似,以xilinx vivado工具為例,主要有以下步驟:系統(tǒng)規(guī)劃、RTL輸入、行為仿真、邏輯綜合、綜合后仿真(可選)、綜合后設(shè)計(jì)分析(時(shí)序及資源)、設(shè)計(jì)實(shí)現(xiàn)(包括布局布線及優(yōu)化)、實(shí)現(xiàn)后設(shè)計(jì)分析(時(shí)序及資源)、板級(jí)調(diào)試、bitstream固化。

29、時(shí)序約束相關(guān)有哪幾種時(shí)序路徑:

input paths:外部引腳到內(nèi)部寄存器 register-to-register paths:系統(tǒng)內(nèi)部寄存器到寄存器路徑 output paths:內(nèi)部寄存器到外部引腳的路徑 port to port paths:FPGA輸入端口到輸出端口路徑(不常用)

30、創(chuàng)建時(shí)序約束的關(guān)鍵步驟: baseline約束:create clocks define clocks interactions I/O約束:set input and output delays 例外約束:set timing execptions(set_max_delay/set_min_delay、set_multicycle_path、set_false_path) 設(shè)計(jì)初期可先不加I/O約束,但baseline約束要盡早建立。

31、 SRAM和DRAM的區(qū)別 SRAM是靜態(tài)隨機(jī)訪問(wèn)存儲(chǔ)器,由晶體管存儲(chǔ)數(shù)據(jù),無(wú)需刷新,讀寫速度快。DRAM是動(dòng)態(tài)隨機(jī)訪問(wèn)存儲(chǔ)器,由電容存儲(chǔ)數(shù)據(jù),由于電容漏電需要?jiǎng)討B(tài)刷新,電容充放電導(dǎo)致讀寫速度較SRAM低。但DRAM成本較低,適合做大容量片外緩存。

32、CMOS和TTL電路區(qū)別是什么? 兩者區(qū)別主要體現(xiàn)在三個(gè)方面: 結(jié)構(gòu):CMOS電路由場(chǎng)效應(yīng)管構(gòu)成,TTL由雙極性晶體管構(gòu)成。 電平范圍:CMOS邏輯電平范圍大(5~15V),TTL只工作在5V以下,因此CMOS噪聲容限比TTL大,抗干擾能力強(qiáng)。 功耗與速率:CMOS的功耗比TTL小,但工作頻率低于TTL。

TTL不能直接驅(qū)動(dòng)CMOS電平,需要加上拉電阻,而CMOS可以直接驅(qū)動(dòng)TTL

33、JTAG接口信號(hào)及功能 JTAG實(shí)際上使用的只有四個(gè)信號(hào):時(shí)鐘TCK、狀態(tài)機(jī)控制信號(hào)TMS、數(shù)據(jù)輸入信號(hào)TDI、數(shù)據(jù)輸出信號(hào)TDO。

34、上拉電阻用途: 1、當(dāng) TTL 電路驅(qū)動(dòng) COMS 電路時(shí),如果 TTL 電路輸出的高電平低于 COMS 電路的最低 高電平 (一般為 3.5V ) , 這時(shí)就需要在 TTL 的輸出端接上拉電阻, 以提高輸出高電平的值。 2、 OC 門電路必須加上拉電阻,以提高輸出的高 電平值。 3、為加大輸出引腳的驅(qū)動(dòng)能力,有的單片機(jī)管腳上也常使用上拉電阻。 4、在 COMS 芯片上,為了防止靜電造成損壞,不用的管腳不能懸空,一般接上拉電阻產(chǎn)生降低輸入阻抗,提供泄荷通路。 5、芯片的管腳加上拉電阻來(lái)提高輸出電平,從而提高芯片輸入信號(hào)的噪聲容限增強(qiáng)抗干擾能力。 6、提高總線的抗電磁干擾能力。管腳懸空就比較容易接受外界的電磁干擾。 7、長(zhǎng)線傳輸中電阻不匹配容易引起反射波干擾,加上下拉電阻是電阻匹配,有效的抑制反射波干擾

35、有四種復(fù)用方式,頻分多路復(fù)用,寫出另外三種 四種復(fù)用方式:頻分多路復(fù)用( FDMA ),時(shí)分多路復(fù)用( TDMA ),碼分多路復(fù)用(CDMA ),波分多路復(fù)用( WDM A) 。

36、基爾霍夫定理的內(nèi)容 基爾霍夫定律包括電流定律和電壓定律: 電流定律:在集總電路中, 在任一瞬時(shí), 流向某一結(jié)點(diǎn)的電流之和恒等于由該結(jié)點(diǎn)流出的電流之和 。 電壓定律:在集總電路中,在任一瞬間, 沿電路中的任一回路繞行一周,在該回路上電動(dòng)勢(shì)之和恒等于各電阻上的電壓降之和

37、三段式狀態(tài)機(jī) 一段式: 只有一個(gè)always block,把所有的邏輯(輸入、輸出、狀態(tài))都在一個(gè)always block的時(shí)序邏輯中實(shí)現(xiàn)。這種寫法看起來(lái)很簡(jiǎn)潔,但是不利于維護(hù),如果狀態(tài)復(fù)雜一些就很容易出錯(cuò),不推薦這種方法。

在簡(jiǎn)單的狀態(tài)機(jī)可以使用。

二段式: 有兩個(gè)always block,把時(shí)序邏輯和組合邏輯分隔開來(lái)。時(shí)序邏輯里進(jìn)行當(dāng)前狀態(tài)和下一狀態(tài)的切換,組合邏輯實(shí)現(xiàn)各個(gè)輸入、輸出以及狀態(tài)判斷。這種寫法不僅便于閱讀、理解、維護(hù),而且利于綜合器優(yōu)化代碼,利于用戶添加合適的時(shí)序約束條件,利于布局布線器實(shí)現(xiàn)設(shè)計(jì)。在兩段式描述中,當(dāng)前狀態(tài)的輸出用組合邏輯實(shí)現(xiàn),可能存在競(jìng)爭(zhēng)和冒險(xiǎn),產(chǎn)生毛刺。

要求對(duì)狀態(tài)機(jī)的輸出用寄存器打一拍,但很多情況不允許插入寄存器節(jié)拍,此時(shí)使用三段式描述。其優(yōu)勢(shì)在于能夠根據(jù)狀態(tài)轉(zhuǎn)移規(guī)律,在上一狀態(tài)根據(jù)輸入條件判斷出當(dāng)前狀態(tài)的輸出,從而不需要額外插入時(shí)鐘節(jié)拍。 三段式: 有三個(gè)always block,一個(gè)時(shí)序邏輯采用同步時(shí)序的方式描述狀態(tài)轉(zhuǎn)移,一個(gè)采用組合邏輯的方式判斷狀態(tài)轉(zhuǎn)移條件、描述狀態(tài)轉(zhuǎn)移規(guī)律,第三個(gè)模塊使用同步時(shí)序的方式描述每個(gè)狀態(tài)的輸出。代碼容易維護(hù),時(shí)序邏輯的輸出解決了兩段式組合邏輯的毛刺問(wèn)題,但是從資源消耗的角度上看,三段式的資源消耗多一些。 二段式和三段式的區(qū)別主要是每個(gè)狀態(tài)的輸出使用組合邏輯還是用時(shí)序邏輯,組合邏輯實(shí)現(xiàn),可能存在競(jìng)爭(zhēng)和冒險(xiǎn),產(chǎn)生毛刺。

38、什么是狀態(tài)圖? 狀態(tài)圖是以幾何圖形的方式來(lái)描述時(shí)序邏輯電路的狀態(tài)轉(zhuǎn)移規(guī)律以及輸出與輸入的關(guān)系。

39、用你熟悉的設(shè)計(jì)方式設(shè)計(jì)一個(gè)可預(yù)置初值的 7 進(jìn)制循環(huán)計(jì)數(shù)器 ,15 進(jìn)制的呢?

module counter7(clk,rst,load,data,cout);

input clk,rst,load;

input [2:0] data;

output reg [2:0] cout;

always@(posedge clk) begin

if(!rst)

cout<=3 ' d0;

else if(load)

cout<=data;

else if(cout>=3 ' d6)

cout<=3 ' d0;

else

cout<=cout+3 ' d1;

end

endmodule

40、你所知道的可編程邏輯器件有哪些?

PAL , PLA , GAL , CPLD , FPGA

41、SRAM,FALSH MEMORY,DRAM , SSRAM及 SDRAM的區(qū)別 ? SRAM :靜態(tài)隨機(jī)存儲(chǔ)器,存取速度快,但容量小,掉電后數(shù)據(jù)會(huì)丟失,不像DRAM需要不停的 REFRESH ,制造成本較高,通常用來(lái)作為快取(CACHE)記憶體使用。

FLASH :閃存,存取速度慢,容量大,掉電后數(shù)據(jù)不會(huì)丟失

DRAM :動(dòng)態(tài)隨機(jī)存儲(chǔ)器,必須不斷的重新的加強(qiáng) (REFRESHED) 電位差量,否則電位差將降低至無(wú)法有足夠的能量表現(xiàn)每一個(gè)記憶單位處于何種狀態(tài)。價(jià)格比 SRAM 便宜,但訪問(wèn)速度較慢,耗電量較大,常用作計(jì)算機(jī)的內(nèi)存使用。

SSRAM :即同步靜態(tài)隨機(jī)存取存儲(chǔ)器。對(duì)于 SSRAM 的所有訪問(wèn)都在時(shí)鐘的上升 /下降沿啟動(dòng)。地址、數(shù)據(jù)輸入和其它控制信號(hào)均于時(shí)鐘信號(hào)相關(guān)。

SDRAM :即同步動(dòng)態(tài)隨機(jī)存取存儲(chǔ)器。

42、有源濾波器和無(wú)源濾波器的區(qū)別

無(wú)源濾波器:這種電路主要有無(wú)源元件 R、 L 和 C組成

有源濾波器:集成運(yùn)放和 R、C 組成,具有不用電感、體積小、重量輕等優(yōu)點(diǎn)。集成運(yùn)放的開環(huán)電壓增益和輸入阻抗均很高, 輸出電阻小, 構(gòu)成有源濾波電路后還具有一定的電壓放大和緩沖作用。但集成運(yùn)放帶寬有限, 所以目前的有源濾波電路的工作 頻率難以做得很高。

43. 什么是同步邏輯和異步邏輯? 同步時(shí)序邏輯電路的特點(diǎn):各觸發(fā)器的時(shí)鐘端全部連接在一起,并接在系統(tǒng) 時(shí)鐘端,只有當(dāng)時(shí)鐘脈沖到來(lái)時(shí),電路的狀態(tài)才能改變。改變后的狀態(tài)將一直保持到下一個(gè)時(shí)鐘脈沖的到來(lái),此時(shí)無(wú)論外部輸入有無(wú)變化,狀態(tài)表中的每個(gè)狀態(tài)都是穩(wěn)定的。 異步時(shí)序邏輯電路的特點(diǎn): 電路中除可以使用帶時(shí)鐘的觸發(fā)器外,還可以使用不帶 時(shí)鐘的觸發(fā)器和延遲元件作為存儲(chǔ)元件,電路中沒(méi)有統(tǒng)一的時(shí)鐘,電路狀態(tài)的改變由外 部輸入的變化直接引起。 同步邏輯是時(shí)鐘之間有固定的因果關(guān)系。異步邏輯是各時(shí)鐘之間沒(méi)有固定的因果關(guān)系。

44. 同步復(fù)位和異步復(fù)位的區(qū)別 同步復(fù)位是在時(shí)鐘沿變化時(shí),完成復(fù)位動(dòng)作。 優(yōu)點(diǎn): 1)抗干擾能力高,可以提出復(fù)位信號(hào)中周期短于時(shí)鐘周期的毛刺; 2)有利于靜態(tài)時(shí)序分析工具的分析; 3)有利于基于周期的仿真工具的仿真。 缺點(diǎn): 1)占用更多資源; 2)對(duì)復(fù)位信號(hào)的脈沖寬度有要求,由于線路上的延遲;可能需要多個(gè)時(shí)鐘周期的復(fù)位脈沖的寬度,而且很難保證復(fù)位信號(hào)到達(dá)各個(gè)寄存器的時(shí)序; 3)同步復(fù)位依賴時(shí)鐘,如果電路中時(shí)鐘信號(hào)出現(xiàn)問(wèn)題則無(wú)法復(fù)位。 異步復(fù)位是只要復(fù)位信號(hào)滿足條件就完成復(fù)位動(dòng)作。 優(yōu)點(diǎn): 1)不需要額外的邏輯資源,實(shí)現(xiàn)簡(jiǎn)單; 2)復(fù)位信號(hào)不依賴于時(shí)鐘。 缺點(diǎn): 1)復(fù)位信號(hào)易受外界干擾,并對(duì)電路內(nèi)的毛刺敏感; 2)復(fù)位信號(hào)的隨機(jī)性可能導(dǎo)致時(shí)序違規(guī),也就是復(fù)位信號(hào)釋放時(shí)在時(shí)鐘有效沿附近,會(huì)使電路處于亞穩(wěn)態(tài)。

45. FPGA芯片內(nèi)有哪兩種儲(chǔ)存器資源? FPGA 芯片內(nèi)有兩種存儲(chǔ)器資源:一種叫block ram,另一種是由 LUT 配置成的內(nèi)部存儲(chǔ)器(也就是分布式ram)。Blockram由一定數(shù)量固定大小的存儲(chǔ)塊構(gòu)成的,使用BLOCK RAM資源不占用額外的邏輯資源,并且速度快。但是使用的時(shí)候消耗BLOCKRAM的資源是其塊大小的整數(shù)倍。

46. 什么是競(jìng)爭(zhēng)與冒險(xiǎn)現(xiàn)象?怎樣判斷?怎樣消 除? 競(jìng)爭(zhēng):在組合邏輯中,由于門的輸入信號(hào)通路 中經(jīng)過(guò)了不同的延時(shí),導(dǎo)致到達(dá)該門的時(shí)間不一致叫競(jìng)爭(zhēng)。 冒險(xiǎn): 由于競(jìng)爭(zhēng)而使電路輸出發(fā)生瞬時(shí)錯(cuò)誤的現(xiàn)象叫做冒險(xiǎn)。(也就是由于競(jìng)爭(zhēng)產(chǎn)生的毛刺叫做冒險(xiǎn)) 判斷方法: 1)代數(shù)法:如果布爾式中有相反的信號(hào)則很有可能產(chǎn)生競(jìng)爭(zhēng)和冒險(xiǎn)現(xiàn)象; 2)圖形法:有兩個(gè)相切的卡諾圈并且相切處沒(méi)有被其他卡諾圈包圍,就有可能出現(xiàn)競(jìng)爭(zhēng)和冒險(xiǎn)現(xiàn)象; 3)實(shí)驗(yàn)法:使用示波器觀測(cè)。 解決方法: 1)加濾波電路,消除毛刺影響; 2)加選通信號(hào),避開毛刺; 3)增減冗余項(xiàng)消除邏輯冒險(xiǎn)。

更多信息可以來(lái)這里獲取==>>電子技術(shù)應(yīng)用-AET<<