對(duì)于FPGA來說,設(shè)計(jì)人員可以充分利用其可編程能力以及相關(guān)的工具來準(zhǔn)確估算功耗,然后再通過優(yōu)化技術(shù)來使FPGA和相應(yīng)的硬件設(shè)計(jì)滿足其功耗方面的要求。

一、靜態(tài)功耗和動(dòng)態(tài)功耗來由以及其變化規(guī)律

在28nm工藝時(shí),電流泄漏問題對(duì)ASIC和FPGA都變得嚴(yán)重,在16nm工藝下這一問題同樣更加具有挑戰(zhàn)性。為獲得更高的晶體管性能,必須降低閾值電壓,但同時(shí)也加大電流泄漏。AMD-Xilinx公司在降低電流泄漏方面做了許多優(yōu)化后,源于泄漏的靜態(tài)功耗在最差和典型工藝條件下的變化仍然有2:1。其泄漏功耗受內(nèi)核電壓(VCCINT)的影響很大,大約與其立方成比例,哪怕VCCINT僅上升5%,靜態(tài)功耗就會(huì)提高約15%。另外泄漏電流還與結(jié)(或芯片)溫密切相關(guān)。

FPGA中靜態(tài)功耗的其它來源是工作電路的直流電流,但在很大程度上,這部分電流隨工藝和溫度的變化不大。例如I/O電源(如HSTL、SSTL和LVDS等I/O標(biāo)準(zhǔn)的端接電壓)以及LVDS等電流驅(qū)動(dòng)型I/O的直流電流。有些FPGA模擬模塊也帶來靜態(tài)功耗,但同樣與工藝和溫度的關(guān)系不大。例如,Xilinx FPGA中用來控制時(shí)鐘的數(shù)字時(shí)鐘管理器(DCM)、鎖相環(huán)(PLL),以及Xilinx FPGA中用于輸入和輸出IO可編程延遲的單元IODELAY。

動(dòng)態(tài)功耗是指FPGA內(nèi)核或I/O的開關(guān)活動(dòng)引起的功耗。為計(jì)算動(dòng)態(tài)功耗,是需要知道開關(guān)晶體管和連線的數(shù)量、電容和開關(guān)頻率。在FPGA器件里面晶體管在金屬連線間實(shí)現(xiàn)邏輯和可編程互連,電容則包括晶體管寄生電容和金屬互連線電容。

動(dòng)態(tài)功率的公式:PDYNAMIC=nCV2?,其中,n=開關(guān)結(jié)點(diǎn)的數(shù)量,C=電容,V=電壓擺幅,f=開關(guān)頻率。

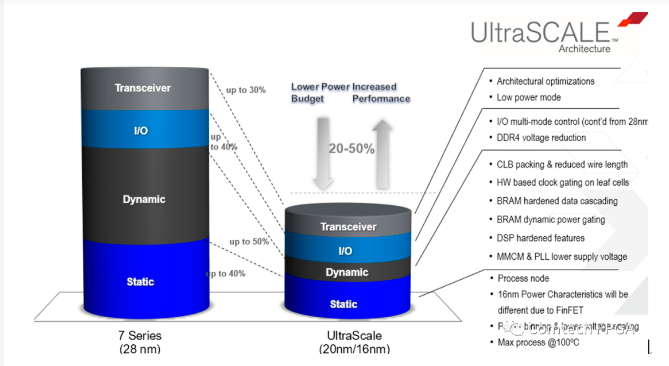

AMD-Xilinx在20nm & 16nm節(jié)點(diǎn)Ultrascale系列器件使用FinFET工藝,F(xiàn)inFET與Planar相比在相同速度條件下功耗低20%-50%。FinFET工藝通過抬升溝道,包裹溝道四周的柵極可以創(chuàng)建一種完全耗盡型溝道,從而克服平面晶體管的漏電流問題。FinFET所具有的更好的溝道控制能力可以用來實(shí)現(xiàn)更低的閾值和供電電壓,從而來控制器件的功耗。

更緊湊的邏輯封裝(通過內(nèi)部FPGA架構(gòu)改變)可以減少開關(guān)晶體管的數(shù)量,也可以采用更小尺寸的晶體管可以縮短晶體管之間的連線長(zhǎng)度,從而降低動(dòng)態(tài)功率。Ultrascale+ FPGA中的16nm晶體管柵極電容更小、互連線長(zhǎng)度也更短,兩者完美的結(jié)合起來可將結(jié)點(diǎn)的電容減小約15%至20%,這可進(jìn)一步降低動(dòng)態(tài)功率。

電壓對(duì)于動(dòng)態(tài)功率同樣有比較大的影響。從28nm轉(zhuǎn)向16nm工藝,僅僅通過將VCCINT從1.0V降至0.72V,Ultrascale FPGA設(shè)計(jì)的動(dòng)態(tài)功率就降低了約50%。再加上結(jié)構(gòu)增強(qiáng)帶來的功率降低,總的動(dòng)態(tài)功耗比28 nm工藝技術(shù)時(shí)降低達(dá)40%至50%。

(注:動(dòng)態(tài)功率與VCCINT的平方成正比,但對(duì)于FPGA內(nèi)核來說基本上與溫度和工藝無關(guān)。)

二、利用FPGA設(shè)計(jì)技術(shù)降低功耗

Xilinx公司提供了兩款功率分析工具。XPower EsTImator (XPE)電子數(shù)據(jù)表工具可在設(shè)計(jì)人員在沒有做實(shí)際的硬件和RTL設(shè)計(jì)前使用。在設(shè)計(jì)實(shí)施完成后,則可以采用第二款工具XPower Analyzer來檢查所做的改變對(duì)功耗的影響。

降低功耗的一種方法就是為設(shè)計(jì)選擇與需要最匹配的FPGA型號(hào),然后利用其可編程能力進(jìn)一步優(yōu)化設(shè)計(jì)的功耗。正確的設(shè)計(jì)會(huì)同時(shí)優(yōu)化靜態(tài)功耗和動(dòng)態(tài)功耗。源于泄漏電流的靜態(tài)功率正比于邏輯資源的數(shù)量,也就是說正比于構(gòu)造特定FPGA所使用的晶體管數(shù)量。

因此,如果減少所使用的FPGA資源,采用更小的器件實(shí)現(xiàn)設(shè)計(jì),那么就可以降低靜態(tài)功耗。降低設(shè)計(jì)的規(guī)模有很多種的方案,最基本的一種技巧就是邏輯功能分時(shí)復(fù)用。如果兩組電路完成一組線性功能并且彼此完全相同,那么就可以只用一組電路但將速率提高一倍來完成同樣的功能,這樣需要的邏輯資源就減少一半。

另一種縮小邏輯規(guī)模的方法是利用Xilinx FPGA的部分重配置功能,當(dāng)兩部分電路不同時(shí)工作時(shí),可以在某個(gè)時(shí)間段將某部分電路重新配置實(shí)現(xiàn)另一種電路功能。同時(shí)盡量保證不要讓設(shè)計(jì)的時(shí)序太緊張,因?yàn)闀r(shí)序緊張會(huì)需要更多的邏輯和寄存器。

此外,還應(yīng)當(dāng)充分發(fā)揮FPGA架構(gòu)中集成的硬IP塊(BRAM、DSP、FIFO、Ethernet MAC、PCI Express)的優(yōu)點(diǎn)。

如果資源充足的情況將功能移動(dòng)到不太受限制的資源,例如,將狀態(tài)機(jī)轉(zhuǎn)移到BRAM、或者將計(jì)數(shù)器轉(zhuǎn)移到DSP48模塊、寄存器轉(zhuǎn)移到移位寄存器邏輯,以及將BRAM轉(zhuǎn)移到查找表RAM(LUTRAM)。

如下幾種是常用優(yōu)化資源節(jié)省功耗方式:

1.避免冗余DCM或PLL,優(yōu)先使用PLL(相對(duì)MMCM省電),簡(jiǎn)單分頻功能使用BUFGCE_DIV替代DCM或PLL;

2.Slice中移位寄存器實(shí)現(xiàn)寄存器打拍,注意slice移位寄存器無法實(shí)現(xiàn)復(fù)位;

3.硬核DSP& Block RAM優(yōu)化時(shí)序盡量使用內(nèi)部寄存器打拍,注意DSP& Block RAM硬核內(nèi)部寄存器不支持異步復(fù)位;

4.Block RAM 增加CE需要使用數(shù)據(jù)時(shí)候才輸出數(shù)據(jù)節(jié)省功耗;

5.級(jí)聯(lián)Block RAM盡量拼深度,任何時(shí)候只打開其中一個(gè)Block RAM;

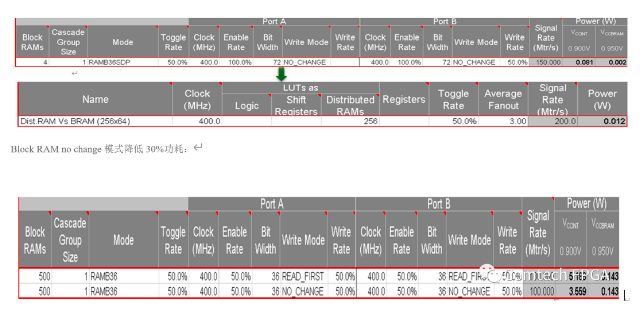

6.Block RAM no change模式降低30%功耗;

7.BUFGCE(扇出100K)或者BUFCE_LEAF(扇出100K)實(shí)現(xiàn)門控時(shí)鐘降低功耗;

8.如果DSP27x18有效位寬10x10,盡量使用高位A[26:16] X [17 :7]低位填充0(進(jìn)位鏈?zhǔn)褂蒙伲A糠臖數(shù)據(jù)口降低功耗。

a、檢查時(shí)鐘資源使用是否合理

降低靜態(tài)功率的另一個(gè)方法是仔細(xì)檢查設(shè)計(jì),避免冗余的直流電源消耗。設(shè)計(jì)中經(jīng)常會(huì)使用到具有多余或隱藏DCM或PLL的模塊,這種情況可能在模塊設(shè)計(jì)后忘記將多余的資源去除,或者在構(gòu)建下一代產(chǎn)品時(shí)使用了一些遺留代碼。將DCM或PLL抽象到設(shè)計(jì)的頂層,這樣模塊之間就可以共享資源,從而可進(jìn)一步減小設(shè)計(jì)的規(guī)模并降低直流功率。PLL相對(duì)MMCM省電,在PLL & MMCM同時(shí)滿足設(shè)計(jì)需要的情況下優(yōu)先使用PLL。在簡(jiǎn)單分頻應(yīng)用場(chǎng)景,使用BUFGCE_DIV替代DCM或PLL。

優(yōu)化存儲(chǔ)器模塊使用可降低FPGA設(shè)計(jì)的動(dòng)態(tài)功耗,從而進(jìn)一步降低總體功耗。由于動(dòng)態(tài)功耗受到容抗(面積或長(zhǎng)度)和頻率的函數(shù)影響比較大,因此應(yīng)當(dāng)檢查設(shè)計(jì)中訪問塊存儲(chǔ)器的方式并確定能夠?qū)θ菘购皖l率進(jìn)行優(yōu)化的區(qū)域。

b、優(yōu)化RAM的使用

AMD-Xilinx FPGA提供兩種類型存儲(chǔ)器陣列BRAM和LUTRAM。18Kbit或36Kbit的BRAM是針對(duì)大存儲(chǔ)器模塊而優(yōu)化的,LUTRAM基于FPGA中的查找表,是針對(duì)細(xì)粒度存儲(chǔ)而優(yōu)化。Xilinx Ultrascale FPGA中,LUTRAM的單位是64bit。在這兩種類型中,BRAM功耗更大一些,那么啟用BRAM后靜態(tài)功率是其功耗的最大部分,而其跳變的功耗相對(duì)動(dòng)態(tài)功耗小。

設(shè)計(jì)人員可以采取一些步驟來優(yōu)化BRAM的功耗。例如,僅在讀或?qū)懼芷诓艈⒂肂RAM;對(duì)于較小的存儲(chǔ)器模塊可以使用LUTRAM來代替BRAM,將BRAM留給較大的存儲(chǔ)器模塊使用。另一種技術(shù)是合理安排存儲(chǔ)器陣列來減少其占用的延遲面積、使性能最大化并盡量降低其功耗。

Xilinx工具也可以幫助選擇適合的存儲(chǔ)器陣列。例如考慮某個(gè)設(shè)計(jì)中需要兩組存儲(chǔ)器區(qū)域,可以先比較256 x 64bit存儲(chǔ)器結(jié)構(gòu)的功率,通過XPE工具顯示出小存儲(chǔ)器陣列最好用LUTRAM來實(shí)現(xiàn),這樣比用BRAM節(jié)約85%的功耗。這是因?yàn)槿绻捎肂RAM的話,只能用4個(gè)36K位的模塊來實(shí)現(xiàn)1個(gè)(256 x 64bit)4 Kbit的存儲(chǔ)器,有很多空間被浪費(fèi)。

36Kb Block RAM 可以當(dāng)成兩個(gè)18Kb Block RAM使用,18(數(shù)據(jù)位寬) x 512(數(shù)據(jù)深度)時(shí)消耗一個(gè)9Kbit block,同樣9Kbit Block RAM大小的存儲(chǔ)空間36(數(shù)據(jù)位寬) x 256(數(shù)據(jù)深度)消耗兩個(gè)9Kbit Block RAM。36Kb Block RAM 可以當(dāng)成一個(gè)36Kb Block RAM使用時(shí),36(數(shù)據(jù)位寬) x 512(數(shù)據(jù)深度)時(shí)消耗兩個(gè)9Kbit Block RAM,同樣18Kbit Block RAM大小的存儲(chǔ)空間72(數(shù)據(jù)位寬) x 256(數(shù)據(jù)深度)消耗四個(gè)9Kbit Block RAM。

Block RAM增加CE需要使用數(shù)據(jù)時(shí)候才輸出數(shù)據(jù)節(jié)省功耗:

c、AMD-Xilinx FPGA的時(shí)鐘門控功能

利用BUFGMUX時(shí)鐘緩沖器將FPGA內(nèi)的某個(gè)全局時(shí)鐘關(guān)閉,或者動(dòng)態(tài)選擇較慢的時(shí)鐘。還可以使用BUFGCE時(shí)鐘緩沖器進(jìn)行按時(shí)鐘周期(cycle-by-cycle)的門控,與ASIC設(shè)計(jì)中使用的時(shí)鐘門控技術(shù)類似。在實(shí)際設(shè)計(jì)中可以同時(shí)使用這兩種功能。在某些設(shè)計(jì)中,一些模塊并非始終使用,但對(duì)于功耗影響卻很大,此時(shí)這些方法非常有用。以時(shí)鐘周期為基礎(chǔ)或者按多個(gè)時(shí)鐘周期的組合開啟或關(guān)閉可能有成千上萬個(gè)負(fù)載規(guī)模大型時(shí)鐘域。

d、在電路板級(jí)功耗降低

PCB設(shè)計(jì)師、機(jī)械工程師和系統(tǒng)架構(gòu)師在電路板級(jí)可以考慮通過以下幾個(gè)方面來降低FPGA的功耗,F(xiàn)PGA的內(nèi)核電壓和結(jié)溫對(duì)于功耗的不同方面都有很強(qiáng)的影響。

控制VCCINT內(nèi)核電壓是板級(jí)降低功耗的一種方法。源于泄漏的靜態(tài)功耗以及動(dòng)態(tài)功耗都高度依賴于FPGA的內(nèi)核電壓。因此,減少泄漏的一種方法就是將內(nèi)核電壓設(shè)置在接近額定值的地方,而不是工作在Ultrascale電壓范圍0.85V(0.876V = +5%)。

采用現(xiàn)代開關(guān)穩(wěn)壓器,可以獲得±1.5%的電壓穩(wěn)定度,而不是標(biāo)準(zhǔn)的±5%規(guī)格。保持內(nèi)核電壓在0.85V(而不是最大值0.876V),可將泄漏導(dǎo)致的靜態(tài)功耗降低15%,同時(shí)動(dòng)態(tài)功耗降低10%。

降低FPGA結(jié)溫的一種簡(jiǎn)單明顯的方法是利用散熱更好的PCB或散熱器。FPGA設(shè)計(jì)人員只要能夠降低功耗的優(yōu)化都是值得去嘗試設(shè)計(jì)的。在結(jié)溫100℃左右時(shí),15℃的溫度降低可以將源于泄漏導(dǎo)致的靜態(tài)功耗降低20%。通過監(jiān)控FPGA中的溫度和電壓也可以降低功耗。

Ultrascale FPGA中包含一個(gè)稱為System Monitor的模擬模塊,可以監(jiān)控外部和內(nèi)部模擬電壓以及芯片內(nèi)部溫度。System Monitor基于一個(gè)10位的A/D變換器,能夠在-40℃至+125℃范圍內(nèi)提供準(zhǔn)確可靠的測(cè)量結(jié)果。A/D變換器將片上傳感器的輸出數(shù)字化,可以利用它來監(jiān)控多達(dá)17路外部模擬輸入,從而監(jiān)控系統(tǒng)性能與外部環(huán)境。模塊內(nèi)包括可配置的閾值和告警電平,通過可配置寄存器內(nèi)存儲(chǔ)測(cè)量結(jié)果,因此可方便地連接到用戶邏輯或微處理器。

此外,I/O功率成為在功耗和性能平衡過程中需要考慮的另一重要因素,通過更為優(yōu)化的I/O選擇可以進(jìn)一步降低總體功耗,驅(qū)動(dòng)力量大電平標(biāo)準(zhǔn)所消耗的功率也更大,因此功率隨輸出速率和跳變速率線性變化。然而LVDS是個(gè)例外,因?yàn)樗捎昧伺c跳變速率無關(guān)的固定電流源,使用serial transceiver替代并行LVDS并行組實(shí)現(xiàn)FPGA數(shù)據(jù)互聯(lián)可以節(jié)省功耗。使用set input delay替換IDELAY器件可以節(jié)省功耗。

結(jié)語

FPGA的動(dòng)態(tài)和靜態(tài)功率優(yōu)化會(huì)一直都是設(shè)計(jì)中一個(gè)比較大的挑戰(zhàn),所以AMD-Xilinx將繼續(xù)致力于優(yōu)化FPGA的功率管理工具和設(shè)計(jì)方法,同時(shí)也將不斷努力在芯片層面上解決功耗問題。本文參考UltraScale/UltraScale+ Power ReducTIon Techniques文檔,同時(shí)也感謝AMD-Xilinx專家TIko的熱情指導(dǎo)。

更多信息可以來這里獲取==>>電子技術(shù)應(yīng)用-AET<<