DRAM的發(fā)展方向

對于 DRAM,主要目標(biāo)是繼續(xù)將 1T-1C 單元的封裝尺寸擴(kuò)大到 4F2 的實(shí)際極限。挑戰(zhàn)在于垂直晶體管結(jié)構(gòu)、高 κ 電介質(zhì)以提高電容密度,同時保持低泄漏。一般來說,DRAM 的技術(shù)要求隨著縮放而變得更加困難。在過去的幾年中,DRAM 引入了許多新技術(shù)(例如,193 nm 氟化氬 (ArF) 浸沒式High NA 光刻技術(shù)和雙圖形技術(shù)、改進(jìn)的單元 FET 技術(shù),包括鰭型晶體管、掩埋字線/單元 FET 技術(shù)等等)。

由于 DRAM 存儲電容器在物理上隨著尺寸縮小而變小,因此等效氧化物厚度 (EOT) 必須急劇縮小以保持足夠的存儲電容。為了擴(kuò)展 EOT,需要具有高相對介電常數(shù) (κ) 的介電材料。因此,采用高κ(ZrO2/Al2O/ZrO2)的金屬-絕緣體-金屬(MIM)電容器作為接地規(guī)則在48nm和30nm半間距之間的DRAM的電容器。和這個材料進(jìn)化和改進(jìn)一直持續(xù)到 20 nm HP 和超高 κ(鈣鈦礦 κ > 50~100)材料被釋放。此外,高 κ 絕緣體的物理厚度應(yīng)按比例縮小以適應(yīng)最小特征尺寸。因此,電容器的 3-D 結(jié)構(gòu)將從圓柱形變?yōu)橹巍?/p>

另一方面,隨著外圍CMOS器件的微縮,這些器件形成后的工藝步驟需要低溫工藝流程。這對于通常在 CMOS 器件形成后構(gòu)建的 DRAM 單元工藝來說是一個挑戰(zhàn),因此僅限于低溫處理。DRAM 外圍設(shè)備要求可以放寬 Ioff 但需要更多 Ion 的低待機(jī)功耗 (LSTP) 設(shè)備。但是,在未來,將需要高 κ 金屬柵極來維持性能。

另一個重要主題是從 6F2 到 4F2 cell的遷移。由于半間距縮放變得非常困難,因此不可能維持成本趨勢。保持成本趨勢并逐代增加總比特輸出的最有希望的方法是改變單元尺寸因子 (a) 縮放比例(其中 a = [DRAM 單元尺寸]/[DRAM 半間距])。目前 6F2(a = 6)是最常見的。例如,垂直單元晶體管是必需的,但仍然存在一些挑戰(zhàn)。另一種選擇是使用 3D DRAM。

總之,需要保持足夠的存儲電容和足夠的單元晶體管性能以在未來保持保留時間特性。他們的困難要求正在增加,以繼續(xù)擴(kuò)展 DRAM 設(shè)備并獲得更大的產(chǎn)品尺寸(即 >16 Gb)。除此之外,如果與引入新技術(shù)相比,成本微縮的效率變差,那么DRAM微縮將會停止,而采用3D單元堆疊結(jié)構(gòu),或者采用新的DRAM概念。

Flash的演進(jìn)方式

有幾種交叉的存儲器技術(shù)具有一個共同的特征——非易失性。要求和挑戰(zhàn)因應(yīng)用而異,范圍從僅需要 Kb 存儲的 RFID 到芯片中數(shù)百 Gb 的高密度存儲。非易失性存儲器可分為兩大類——閃存(NAND Flash 和 NOR Flash)和非基于電荷的存儲存儲器。非易失性存儲器基本上無處不在,許多應(yīng)用程序使用通常不需要前沿技術(shù)節(jié)點(diǎn)的嵌入式存儲器。More Moore 非易失性存儲器表僅跟蹤前沿獨(dú)立部件的存儲器挑戰(zhàn)和潛在解決方案。

閃存基于簡單的單晶體管 (1T) 單元,其中晶體管既用作訪問(或單元選擇)設(shè)備又用作存儲節(jié)點(diǎn)。目前閃存服務(wù)于99%以上的應(yīng)用。

當(dāng)存儲電子的數(shù)量達(dá)到統(tǒng)計極限時,即使可以進(jìn)一步縮小器件尺寸,實(shí)現(xiàn)更小的單元,存儲器陣列中所有器件的閾值電壓分布也變得不可控,邏輯狀態(tài)不可預(yù)測。因此,存儲密度不能通過持續(xù)縮放基于電荷的設(shè)備來無限增加。然而,通過垂直堆疊存儲層可能會繼續(xù)有效提高密度。

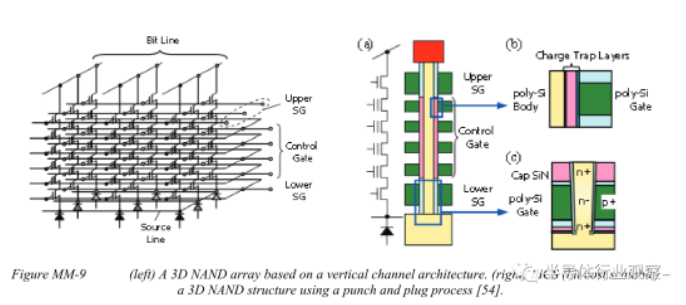

通過完成一個設(shè)備層然后完成另一層等等來堆疊的經(jīng)濟(jì)性值得懷疑。如圖 MM-9 所示,在堆疊幾層設(shè)備后,每位成本開始上升。此外,由于復(fù)雜處理增加的互連和良率損失導(dǎo)致陣列效率下降,可能會進(jìn)一步降低此類 3D 堆疊的每比特成本優(yōu)勢。

在2007 年,業(yè)內(nèi)提出了一種“punch and plug”方法來垂直制造位線串,以大大簡化加工步驟。這種方法使 3D 堆疊設(shè)備只需幾個步驟,而不是通過重復(fù)處理,從而為 NAND 閃存提供了一條新的低成本擴(kuò)展路徑。圖 MM-9 說明了一種這樣的方法。最初創(chuàng)造的bit-cost-scalable(或 BiCS)架構(gòu)將 NAND 串從水平位置轉(zhuǎn)為垂直位置 90 度。字線(WL)保持在水平面上。如圖 MM-9 所示,這種類型的 3D 方法比完整設(shè)備的堆疊要經(jīng)濟(jì)得多,并且成本效益不會達(dá)到相當(dāng)高的層數(shù)。

自 2007 年以來,已經(jīng)提出了許多基于 BiCS 概念的架構(gòu),當(dāng)中包括一些使用浮柵而不是電荷捕獲層進(jìn)行存儲的架構(gòu),這些技術(shù)在過去 2-3 年中已經(jīng)投入量產(chǎn)。一般來說,所有 3D NAND 方法都采用了一種策略,即使用比傳統(tǒng) 2D NAND 大得多的面積占用空間。3D NAND 的 x 和 y 尺寸(相當(dāng)于 2D 中的單元尺寸)在 100nm 范圍內(nèi)甚至更高,而最小的 2D NAND 約為 15nm。更大的“單元尺寸”是通過堆疊大量存儲層來實(shí)現(xiàn)具有競爭力的封裝密度的。

3D NAND 的經(jīng)濟(jì)性因其復(fù)雜而獨(dú)特的制造需求而變得更加混亂。盡管較大的單元尺寸似乎放寬了對細(xì)線光刻的要求,但要實(shí)現(xiàn)高數(shù)據(jù)速率,最好使用large page size尺寸,而這又會轉(zhuǎn)化為細(xì)間距位線和金屬線。因此,即使單元尺寸很大,金屬線仍然需要約 20nm 的半間距,這只能通過具有雙圖案的 193i 光刻來實(shí)現(xiàn)。深孔刻蝕難度大、速度慢,刻蝕產(chǎn)量一般很低。沉積多層電介質(zhì)和/或多晶硅,以及多層膜和深孔的計量都是對陌生領(lǐng)域的挑戰(zhàn)。這些都轉(zhuǎn)化為對新設(shè)備和占地面積的大量投資,以及對晶圓流和良率的新挑戰(zhàn)。

最終的未知數(shù)是可以堆疊多少層。

層的堆疊似乎沒有硬性物理限制。超過一定的縱橫比(也許是 100:1?)時,當(dāng)反應(yīng)離子蝕刻過程中的離子被側(cè)壁上的靜電荷彎曲并且不能進(jìn)一步向下移動時,蝕刻停止(etch-stop)現(xiàn)象可能會限制一次操作中可以蝕刻的層數(shù) . 然而,這可以通過堆疊更少的層、蝕刻和堆疊更多的層(以更高的成本)來繞過。

堆疊許多層可能會產(chǎn)生使晶圓彎曲的高應(yīng)力,盡管這需要仔細(xì)設(shè)計,但它似乎并不是無法解決的物理極限。即使在 200 層(每層約 50nm)時,總堆疊高度約為 10?m,仍然與邏輯 IC 的 10-15 層金屬層處于同一范圍內(nèi)。這種層厚度不會顯著影響裸芯片厚度(目前最薄約為 40?m)。

然而,在 1000 層時,總層厚度可能會導(dǎo)致厚die不符合在薄封裝中堆疊多個die(例如,16 或 32)的形狀因數(shù)。目前量產(chǎn)176層,300+層有望實(shí)現(xiàn),甚至500、800層也有可能。除了處理挑戰(zhàn)之外,堆疊更多層還增加了接觸更多字線所需的面積開銷。該區(qū)域開銷,加上增加的處理復(fù)雜性,最終將通過添加更多層來降低成本效益。

當(dāng)堆疊更多層被證明太困難時,面積 x-y 足跡的重新縮小可能最終會開始。然而,這種趨勢并不能保證。如果孔縱橫比是限制因素,那么縮小占位面積不會降低該比率,因此也無濟(jì)于事。此外,與緊密間距的 2D NAND 相比,更大的單元尺寸似乎至少部分有助于 3D NAND 的更好性能(速度和循環(huán)可靠性)。x-y 縮放是否仍能提供這樣的性能尚不清楚。

因此,未來幾代的路線圖預(yù)測在 2022 年與當(dāng)前節(jié)點(diǎn)保持一致。另一方面,增加每個存儲單元的存儲位數(shù)雖然在技術(shù)上具有挑戰(zhàn)性,但似乎取得了進(jìn)展。這在一定程度上是為了利用 3D NAND 器件本質(zhì)上更大,因此存儲的電子更多,更容易制成更多的邏輯電平。

目前 4 位/單元器件 (QLC) 正在量產(chǎn),并且樂觀地認(rèn)為 5 位/單元甚至更多可能在不久的將來變得可行。一個單元中更多的存儲位需要在性能上做出一些折衷,因?yàn)樗枰L的時間來編程和讀取,并且在將邏輯電平壓縮在一起時可靠性會受到影響。然而對于許多讀取密集型應(yīng)用程序來說,為了降低成本,這種權(quán)衡是可以接受的。

新興存儲的不確定性

由于存儲電荷太少,2D NAND Flash 縮放受到統(tǒng)計波動的限制,一些不基于電荷存儲的非常規(guī)非易失性存儲器(鐵電或 FeRAM、磁性或 MRAM、相變或 PCRAM,以及電阻或 ReRAM)正在開發(fā)中,形成通常稱為“新興”存儲器的類別。

盡管 2D NAND 正在被 3D NAND 取代(不再受制于電子太少的缺點(diǎn)),但基于非電荷的新興存儲器的一些特性(例如低電壓操作或隨機(jī)存取)正在被各種各樣的應(yīng)用關(guān)注從而獲得繼續(xù)發(fā)展的機(jī)會。這些新興的存儲器通常具有兩端結(jié)構(gòu)(例如,電阻器或電容器),因此很難同時用作單元格選擇設(shè)備。存儲單元一般以1T-1C、1T-1R或1D-1R的形式結(jié)合單獨(dú)的存取器件。

1 FeRAM:鐵隨機(jī)存儲器

FeRAM 器件通過切換和感測鐵電電容器的極化狀態(tài)來實(shí)現(xiàn)非易失性。要讀取內(nèi)存狀態(tài),必須跟蹤鐵電電容器的磁滯回線( hysteresis loop),并且存儲的數(shù)據(jù)被破壞并且必須在讀取后寫回(破壞性讀取,如 DRAM)。由于這種“破壞性讀取”,找到既能提供足夠的極化變化又能在延長的工作周期內(nèi)保持必要穩(wěn)定性的鐵電材料和電極材料是一項挑戰(zhàn)。

許多鐵電材料對于 CMOS 制造材料的正常補(bǔ)充來說是陌生的,并且可以通過傳統(tǒng)的 CMOS 處理條件退化。FeRAM 速度快、功耗低、電壓低,因此適用于 RFID、智能卡、ID 卡和其他嵌入式應(yīng)用。處理難度限制了它的廣泛采用。最近,提出了基于 HfO2 的鐵電 FET,其鐵電性用于改變 FET 的 Vt,從而可以形成類似于閃存的 1T 單元。如果開發(fā)成熟,這種新存儲器可以用作低功耗且速度非常快的類似閃存的存儲器。

2 MRAM:磁性內(nèi)存

MRAM (Magnetic RAM) 設(shè)備采用磁性隧道結(jié) (MTJ:magnetic tunnel junction) 作為存儲元件。MTJ 單元由兩種鐵磁材料組成,由用作隧道勢壘的薄絕緣層隔開。當(dāng)一層的磁矩切換為與另一層對齊(或與另一層的方向相反)時,電流流過 MTJ 的有效電阻會發(fā)生變化。可以讀取隧道電流的大小以指示存儲的是“一”還是“零”。場切換 MRAM 可能是最接近理想的“通用存儲器”的,因?yàn)樗欠且资缘摹⒖焖俚牟⑶铱梢詿o限循環(huán)。因此,它可以用作 NVM 以及 SRAM 和 DRAM。

然而,在 IC 電路中產(chǎn)生磁場既困難又低效。盡管如此,F(xiàn)ield Switching MTJ MRAM已經(jīng)成功制成產(chǎn)品。然而,當(dāng)存儲元件縮放時,切換所需的磁場會增加,而電遷移會限制可用于產(chǎn)生更高 H 場的電流密度。因此,預(yù)計現(xiàn)場開關(guān) MTJ MRAM 不太可能擴(kuò)展到 65nm 節(jié)點(diǎn)以上。

“STT(spin-transfer torque )”方法的最新進(jìn)展提供了一種新的潛在解決方案,其中自旋極化電流將其角動量轉(zhuǎn)移到自由磁性層,從而在不借助外部磁場的情況下反轉(zhuǎn)其極性。在自旋轉(zhuǎn)移過程中,大量電流通過 MTJ 隧道層,這種應(yīng)力可能會降低寫入耐久性。在進(jìn)一步縮放時,存儲元件的穩(wěn)定性會受到熱噪聲的影響,因此預(yù)計在 32nm 及以下需要垂直磁化材料。最近已經(jīng)證明了垂直磁化。

隨著NAND Flash的快速發(fā)展,以及最近推出的有望繼續(xù)等效縮放的3D NAND,STT-MRAM取代NAND的希望似乎渺茫。然而,其類似 SRAM 的性能和比傳統(tǒng) 6T-SRAM 小得多的占用空間在該應(yīng)用中引起了極大的興趣,特別是在不需要高循環(huán)耐久性的移動設(shè)備中,例如在計算中。因此,STT-MRAM 現(xiàn)在大多不被視為獨(dú)立內(nèi)存,而是嵌入式內(nèi)存 ,并且不在獨(dú)立 NVM 表中進(jìn)行跟蹤。

STT-MRAM 不僅是嵌入式 SRAM 替代品的潛在解決方案,也是嵌入式閃存 (NOR) 替代品的潛在解決方案。這對于物聯(lián)網(wǎng)應(yīng)用來說可能特別有趣,因?yàn)榈凸氖亲钪匾摹A硪环矫妫瑢τ谑褂酶叽鎯γ芏鹊钠渌度胧较到y(tǒng)應(yīng)用,預(yù)計 NOR 閃存將繼續(xù)占據(jù)主導(dǎo)地位,因?yàn)樗匀桓叱杀拘б妗4送猓W存能夠承受 PCB 板焊接過程(約 250°C)而不會丟失其預(yù)加載代碼,這是眾所周知的,許多新興存儲器尚未能夠證明這一點(diǎn)。

3 PCRAM

PCRAM 器件使用硫?qū)倩锊AВㄗ畛S玫幕衔锸?Ge2Sb2Te5,或 GST)的非晶態(tài)和晶態(tài)之間的電阻率差異來存儲邏輯電平。該器件由頂部電極、硫族化物相變層和底部電極組成。泄漏路徑被與相變元件串聯(lián)的存取晶體管(或二極管)切斷。

相變寫入操作包括:(1) RESET,其中硫族化物玻璃通過短電脈沖瞬間熔化,然后快速淬火成具有高電阻率的非晶固體,以及 (2) SET,其中振幅較低但更長脈沖(通常 >100ns)將非晶相退火為低電阻晶態(tài)。1T-1R(或 1D-1R)單元比 NOR Flash 更大或更小,取決于使用的是 MOSFET 還是 BJT(或二極管。該設(shè)備可以被編程為任何最終狀態(tài)而無需擦除先前狀態(tài),從而提供更快的編程吞吐量。簡單的電阻器結(jié)構(gòu)和低電壓操作也使 PCRAM 對于嵌入式 NVM 應(yīng)用具有吸引力。

PCRAM 的主要挑戰(zhàn)是重置相變元件所需的高電流(fraction of mA),以及相對較長的設(shè)置時間和高溫耐受性以在回流焊期間(約 250°C)保留預(yù)加載代碼。熱干擾是 PCRAM 可擴(kuò)展性的潛在挑戰(zhàn)。然而,熱干擾效應(yīng)是非累積的(不像閃存,其中導(dǎo)致電荷注入的編程和讀取干擾是累積的)并且較高溫度的RESET脈沖很短(10ns。相變材料與電極的相互作用可能會帶來長期的可靠性問題并限制循環(huán)耐久性,是類 DRAM 應(yīng)用的主要挑戰(zhàn)。與 DRAM 一樣,PCRAM 是真正的隨機(jī)存取、位可變存儲器。

已經(jīng)使用碳納米管作為電極證明, PCRAM 器件可以做到 < 5nm 的可擴(kuò)展性,并且復(fù)位電流遵循較大器件的外推線。至少在一個案例中,證明了 1E11 的循環(huán)耐力。相變存儲器從2011年開始用于功能手機(jī),取代NOR Flash,2012年開始在~45nm節(jié)點(diǎn)量產(chǎn),但此后沒有新產(chǎn)品推出。在過去的幾年中,PCM 存儲器也被瞄準(zhǔn)為嵌入式應(yīng)用程序的 eFlash 替代品的潛在候選者 。在這些工作中,不同類別的相變材料的合金化允許獲得符合焊接回流的存儲器;然而,如此高的溫度穩(wěn)定性是以較慢的寫入速度為代價的。

4 ReRAM:電阻式存儲器

目前正在研究一大類兩端器件,其中存儲狀態(tài)由金屬-絕緣體-金屬 (MIM:metal-insulator-metal ) 結(jié)構(gòu)的電阻率決定,用于存儲應(yīng)用。其中許多電阻式存儲器仍處于研究階段。由于他們承諾縮小到 10nm 以下,并以極高的頻率 (< ns) 和低功耗運(yùn)行,過去十年中許多工業(yè)實(shí)驗(yàn)室的重點(diǎn)研發(fā)工作使這項技術(shù)被廣泛認(rèn)為是 NAND 的潛在繼承者(包括 3D NAND ).

作為一種雙端器件,高密度 ReRAM 的發(fā)展一直受到缺乏良好選擇器器件的限制。然而,3D XP 內(nèi)存的最新進(jìn)展似乎已經(jīng)解決了這個瓶頸,如果解決了不穩(wěn)定位等其他技術(shù)問題,ReRAM 可能會取得快速進(jìn)展。除了 3D XP 陣列(類似于基于 PCRAM 的 3D XP 存儲器)之外,還可以使用 2D 陣列和小字線 (WL) 和小位線 (BL) 半間距制造高密度 ReRAM 產(chǎn)品。

此外,如果最終采用 OTS 類型的選擇器器件,那么使用底部的晶體管和 3D 陣列中每個 ReRAM 器件的 OTS 選擇器來制造 BiCS 型 3D ReRAM 似乎是可行的,如圖 MM-10 所示。盡管由于引入 3D XP 內(nèi)存似乎解決了雙極選擇器設(shè)備的瓶頸,但尚未推出高密度 ReRAM 產(chǎn)品,但可以合理預(yù)期 ReRAM 的進(jìn)展。

然而最近,開發(fā)高密度 ReRAM 的熱情似乎消退了。這可能是由于兩個原因。(1) 3D NAND Flash的成功增加了進(jìn)入門檻, (2) 難以滿足大型陣列的可靠性要求。(請注意,針對嵌入式應(yīng)用程序的較小 Mb 大小陣列成功開發(fā) ReRAM 已發(fā)布多項公告。)

在過去的幾年中,上述這些問題似乎注定了高密度 ReRAM 的大規(guī)模應(yīng)用。最初關(guān)于 ReRAM 由數(shù)千個原子組成,不受統(tǒng)計波動影響的論點(diǎn)現(xiàn)在看來值得懷疑。似乎操作 ReRAM 的燈絲僅由幾個原子(離子)組成。似乎有證據(jù)表明,即使是相對較大的 ReRAM 設(shè)備也會受到統(tǒng)計波動的影響。因此,我們不看好高密度應(yīng)用的 ReRAM。

更多精彩內(nèi)容歡迎點(diǎn)擊==>>電子技術(shù)應(yīng)用-AET<<